CMOS(互补金属氧化物半导体)是一种广泛使用的集成电路技术,它利用了两种类型的晶体管:N型和P型。CMOS门电路是数字逻辑电路的基本构建块,包括CMOS与门、或门、非门、异或门等。要判断CMOS门电路的输出状态,我们需要了解以下几个关键方面:

- CMOS晶体管的工作原理:

- N型晶体管(NMOS):在栅极电压高于源极电压时导通,低于源极电压时截止。

- P型晶体管(PMOS):在栅极电压低于源极电压时导通,高于源极电压时截止。

- CMOS门电路的基本结构:

- CMOS与门:由一对NMOS和PMOS晶体管组成,只有当所有输入都为高电平时,输出才为高电平。

- CMOS或门:由一对NMOS和PMOS晶体管组成,只要有一个输入为高电平,输出就为高电平。

- CMOS非门:由一对NMOS和PMOS晶体管组成,输出与输入相反。

- CMOS异或门:由多个CMOS与门、或门和非门组成,实现输入的异或逻辑。

- CMOS门电路的静态特性:

- CMOS门电路的动态特性:

- CMOS门电路的输出状态判断方法:

- 逻辑表:列出所有可能的输入组合及其对应的输出状态。

- 真值表:列出所有可能的输入组合及其对应的真值输出(0或1)。

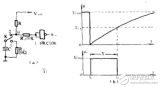

- 波形图:显示输入信号和输出信号随时间变化的图形。

- CMOS门电路的设计考虑:

- 电源电压:CMOS门电路的电源电压通常为3.3V或5V。

- 负载电容:设计时需要考虑输出端的负载电容,以确保传播延迟在可接受范围内。

- 噪声容限:CMOS门电路具有一定的噪声容限,可以容忍一定程度的电压波动。

- CMOS门电路的故障诊断:

- 短路测试:检查晶体管是否短路。

- 开路测试:检查晶体管是否开路。

- 静态电流测试:检查CMOS门电路的静态电流是否在正常范围内。

- CMOS门电路的应用:

- CMOS门电路的发展趋势:

- 工艺缩放:随着工艺技术的发展,CMOS门电路的尺寸不断缩小,性能不断提高。

- 低功耗设计:为了降低功耗,CMOS门电路的设计越来越注重低功耗技术。

- 新型逻辑门:研究人员正在探索新型的CMOS逻辑门,以实现更高的性能和更低的功耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

晶体管

+关注

关注

77文章

9678浏览量

138049 -

CMOS门电路

+关注

关注

0文章

6浏览量

4901 -

集成电路技术

+关注

关注

0文章

4浏览量

1697

发布评论请先 登录

相关推荐

转载-------TTL和CMOS门电路的区别

本帖最后由 hxing 于 2014-3-23 14:48 编辑

TTL和CMOS门电路的区别:1. TTL和带缓冲的TTL信号 输出高电平>2.4V,输出低电平=2.0V,输入

发表于 03-23 14:27

CMOS和TTL集成门电路多余输入端如何处理?

使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法: 1、与门和与非门电路:由于与门电路的逻辑功能是输入信号只要有低电平,输出

发表于 08-30 11:18

CMOS和TTL集成门电路多余输入端如何处理?

使用CMOS门电路时输入端特别注意不能悬空。在使用时应采用以下方法: 1、与门和与非门电路:由于与门电路的逻辑功能是输入信号只要有低电平,输出

发表于 12-03 10:49

CMOS逻辑门电路

CMOS逻辑门电路

CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的

发表于 04-06 23:25

•2.2w次阅读

CMOS电路什么输入为高电平 cmos门电路输出电平判断

半导体)管道组成。在CMOS电路中,输入信号的高和低电平取决于输入信号的电压和电路中的配置。 对于CMOS门电路来说,

cmos或非门电路与ttl或非门电路的逻辑功能

本文就CMOS或非门电路和TTL或非门电路的逻辑功能进行了详细讲解。首先介绍了CMOS和TTL两种电路的基本原理和实现方式。然后分别从输入特

非门电路的输入端电阻模式怎么设置电平状态

非门电路的输入端电阻模式设置电平状态的方法主要取决于非门电路的类型(如TTL、CMOS等)以及具体的设计需求。以下是一些一般性的指导原则:

怎么判断cmos门电路的输出状态

怎么判断cmos门电路的输出状态

评论