三态输出门(Tri-State Output Gate)是一种特殊类型的逻辑门,它具有三个状态:高电平、低电平和高阻抗状态(也称为高阻抗或浮空状态)。这种门在数字电路设计中非常有用,因为它可以实现线与功能,即允许多个门的输出端共享同一信号线,而不会相互干扰。

- 三态输出门的基本概念

三态输出门是一种具有三个输出状态的逻辑门。除了传统的高电平和低电平状态外,它还有一个高阻抗状态。在高阻抗状态下,输出端相当于断开,不会产生任何电流。这种特性使得三态输出门可以在多个门之间共享同一信号线,而不会相互干扰。

- 三态输出门的工作原理

三态输出门的工作原理基于一个额外的控制信号,通常称为使能信号(Enable Signal)。当使能信号为高电平时,三态输出门的输出端将根据输入信号产生高电平或低电平;当使能信号为低电平时,三态输出门的输出端将进入高阻抗状态。

- 三态输出门的类型

三态输出门有多种类型,包括三态缓冲器、三态与门、三态或门等。这些门的基本功能与其他类型的逻辑门相似,但它们具有额外的使能信号输入,以实现高阻抗状态。

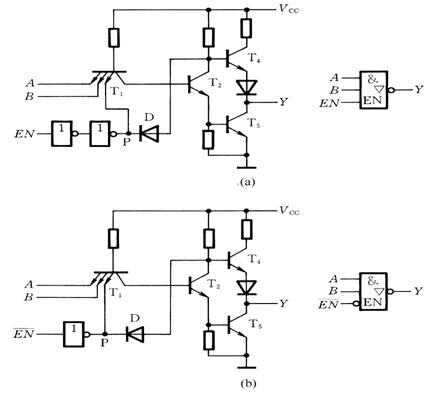

- 三态输出门的实现方式

三态输出门可以通过多种方式实现,包括使用晶体管、MOSFET或其他半导体器件。在实现过程中,关键在于设计一个电路,当使能信号为低电平时,输出端能够进入高阻抗状态。

- 三态输出门的应用

三态输出门在数字电路设计中有广泛的应用,包括:

a. 总线驱动:在多总线系统中,三态输出门可以用于驱动多个设备共享同一信号线,而不会相互干扰。

b. 多路复用器:三态输出门可以用于实现多路复用器,允许多个信号共享同一输出线。

c. 可编程逻辑控制器:在可编程逻辑控制器中,三态输出门可以用于实现复杂的逻辑控制功能。

d. 通信接口:在某些通信接口中,三态输出门可以用于实现数据的双向传输。

- 三态输出门的设计考虑

在设计三态输出门时,需要考虑以下几个关键因素:

a. 使能信号的稳定性:确保使能信号在高电平和低电平之间稳定切换,以避免输出端出现不确定状态。

b. 输出端的驱动能力:在设计三态输出门时,需要确保输出端在高电平和低电平状态下具有足够的驱动能力,以满足负载要求。

c. 高阻抗状态的稳定性:在高阻抗状态下,输出端应该具有足够的稳定性,以避免受到外部干扰的影响。

d. 功耗和速度:在设计三态输出门时,需要权衡功耗和速度之间的关系,以满足特定应用的需求。

- 三态输出门的测试和验证

在设计和实现三态输出门后,需要进行严格的测试和验证,以确保其性能满足预期要求。测试和验证的步骤包括:

a. 功能测试:验证三态输出门在不同输入和使能信号组合下的功能正确性。

b. 时序测试:检查三态输出门的时序特性,确保其在不同频率下的性能稳定。

c. 负载测试:测试三态输出门在不同负载条件下的性能,以确保其驱动能力满足要求。

d. 噪声和干扰测试:评估三态输出门在高阻抗状态下对外部噪声和干扰的抵抗能力。

- 三态输出门的未来发展

随着电子技术的不断发展,三态输出门的设计和应用也在不断进步。未来的发展趋势可能包括:

a. 更高的集成度:随着半导体工艺的不断进步,三态输出门的尺寸将越来越小,集成度将越来越高。

b. 更低的功耗:通过优化设计和工艺,三态输出门的功耗将不断降低,以满足低功耗应用的需求。

c. 更高的性能:通过改进电路设计和材料,三态输出门的性能将不断提高,包括速度、驱动能力和稳定性。

d. 更广泛的应用:随着三态输出门性能的提高,其应用领域将不断扩展,包括物联网、可穿戴设备和智能传感器等新兴领域。

总之,三态输出门是一种具有广泛应用的数字电路元件,它通过实现线与功能,为数字电路设计提供了灵活性和可靠性。

-

逻辑门

+关注

关注

1文章

142浏览量

24232 -

半导体器件

+关注

关注

12文章

773浏览量

32337 -

控制信号

+关注

关注

0文章

169浏览量

12087 -

高电平

+关注

关注

6文章

156浏览量

21597

发布评论请先 登录

相关推荐

三态输出门可以实现线与功能吗

三态输出门可以实现线与功能吗

评论