文章概述

三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对三态逻辑感兴趣,相信这篇内容会让你对其有基础的认识。

三态逻辑输入/输出

在数字电子技术中,三态逻辑(TRIS)允许输入或输出假设为1、0或 高阻抗状态 (开路)。

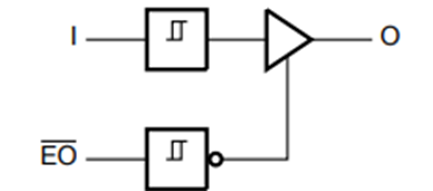

一个缓冲器三态图

三态输入

可以检测引脚是否为逻辑1、0或未连接(开路)。

三态输出

允许多个电路共享相同的输出线。如果有多个设备与另一个设备电连接,则通常会将输出置于Hi-Z态以防止短路,例如当一个设备输出高电平(逻辑1)而另一个设备输出低电平(逻辑0)时。

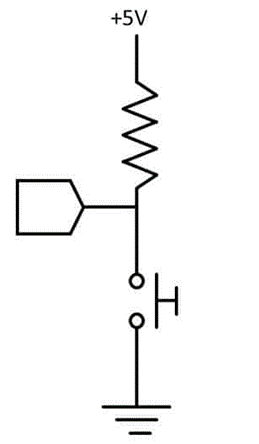

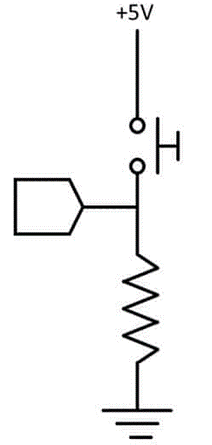

当输出为三态(处于Hi-Z状态)时,它们对电路其余部分的影响将被消除,如果没有其他电路元件能够决定其状态,则电路节点将为“浮动”状态。电路设计人员通常会使用上拉 或 下拉电阻 (通常在1-100kΩ范围内)来影响当输出为三态时的电路。

上拉电阻

下拉电阻

三态逻辑还可以减少驱动一组LED所需的电线数量(三态多路复用或查理复用)。

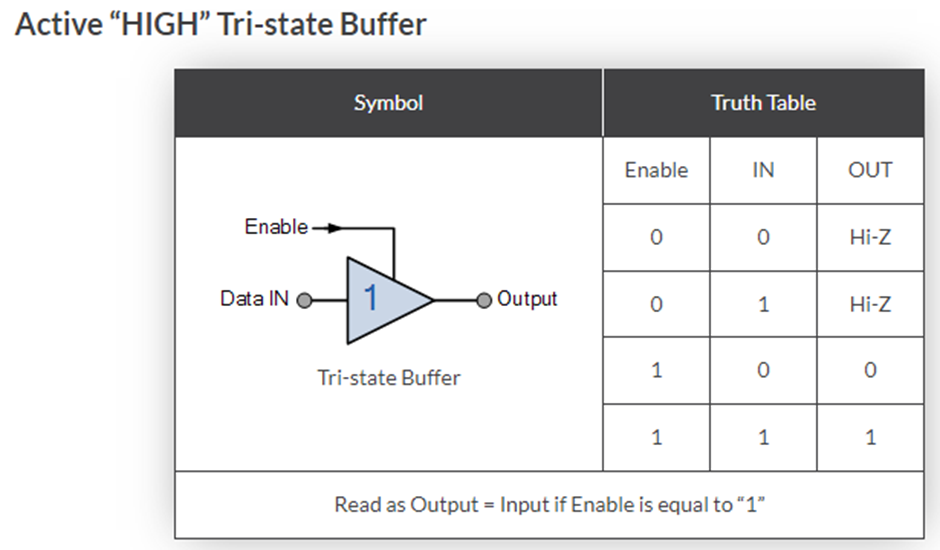

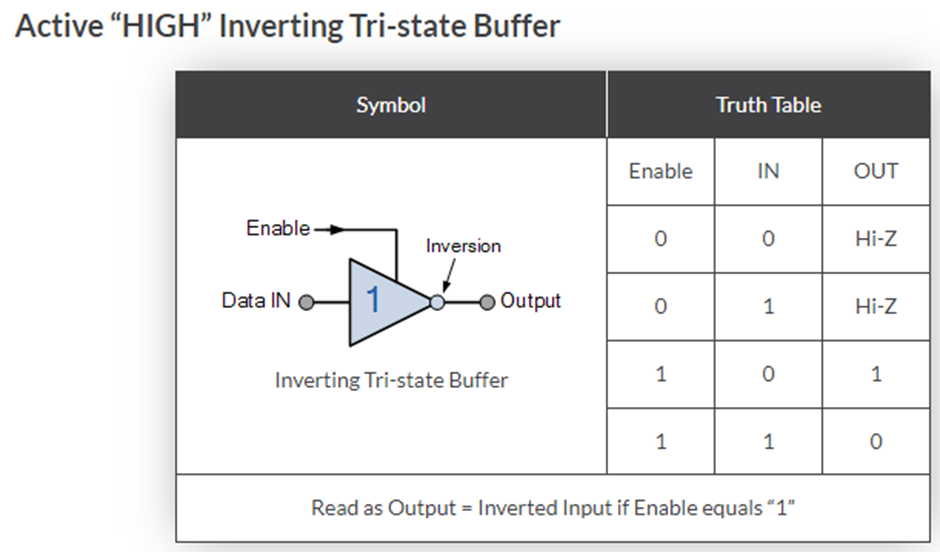

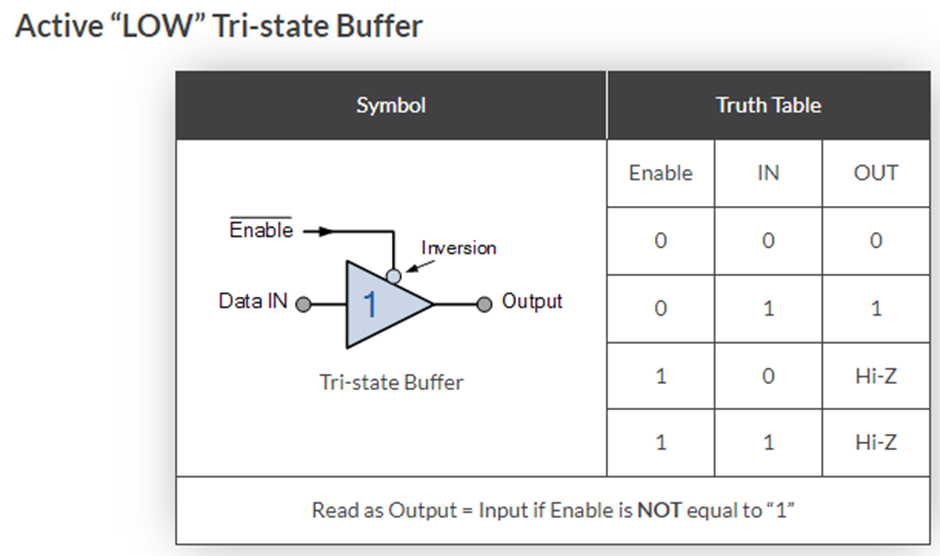

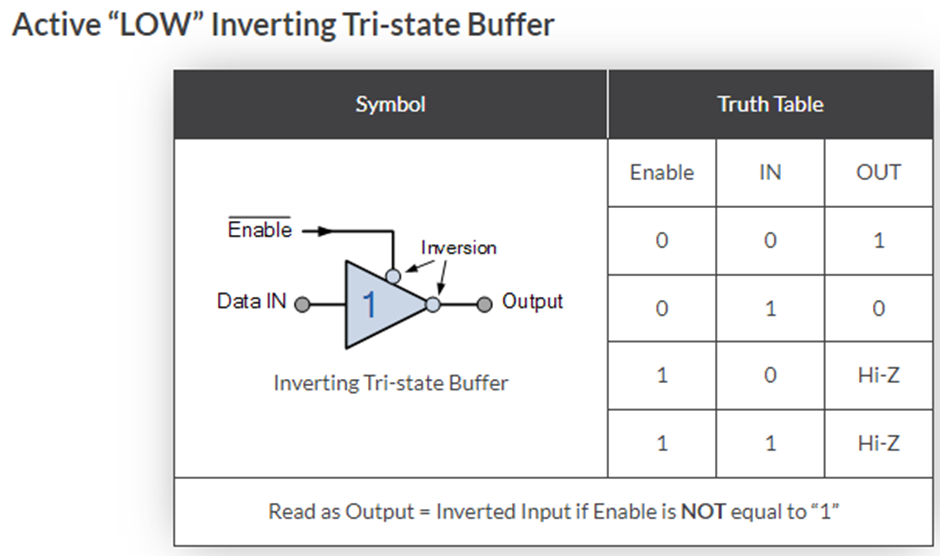

四种三态缓冲器

共四种不同类型的三态缓冲器,一组是通过“高电平有效”控制信号启用或禁用输出,从而产生逆向或非逆向输出,另一组是通过“低电平有效”控制信号来控制缓冲器输出,从而产生逆向或非逆向输出,如下所示。

-

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

电路元件

+关注

关注

0文章

115浏览量

11033 -

三态缓冲器

+关注

关注

1文章

11浏览量

4472

原文标题:三态逻辑电路揭秘:工作原理与其四种缓冲器

文章出处:【微信号:得捷电子DigiKey,微信公众号:得捷电子DigiKey】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三态逻辑电路的工作原理及其四种三态缓冲器介绍

三态逻辑电路的工作原理及其四种三态缓冲器介绍

评论