机器学习和人工智能日益普及,虚拟机和虚拟组件上的工作负载也随之不断增加。为此,行业急需能够确定工作负载优先次序并保障性能的机制。Compute Express Link(CXL)是处理器与加速器、内存缓冲区、智能网络接口卡、持久存储器和固态驱动器等设备之间的开放式行业标准互连接口。CXL基于PCIe灵活的数据带宽提供了缓存一致性和存储语义,同时实现比PCIe低得多的延时。

作为图形处理单元(GPU)、通用图形处理单元(GP-GPU)、现场可编程门阵列(FPGA)的通用设备互连,CXL采用了PCI-Express或PCIe串行接口。同时,CXL也可以用于传统上通过DDR并行接口连接到CPU的内存。

CXL协议的新功能支持增强内存池,并且需要分布式内存管理。此外,在设备连接至虚拟机时,CXL还要求在运行时可以对设备进行动态重组和分配,从而增加了多路复用的机会,进而显著提高了资源利用率并降低成本。

为了满足上述要求,就需要进一步增强和部署CXL,以提供高可靠性、低延迟负载存取,增强对不同服务质量要求的适应性。

CXL 3.1规范特性

当前的CXL 3.0规范特性可总结如下:

链路速度最高达64 GT/s

支持CXL.IO、CXL.Cache和CXL.Mem协议

支持256B和68B FLIT

延迟优化的FLIT

反向无效Snoop

Fabric支持

IDE安全性

当前版本侧重于缓存一致性和交换功能,而3.1版本解决了加速器必须保证缓存一致性访问对等设备时的带宽瓶颈等问题:

CXL 3.1规范特性

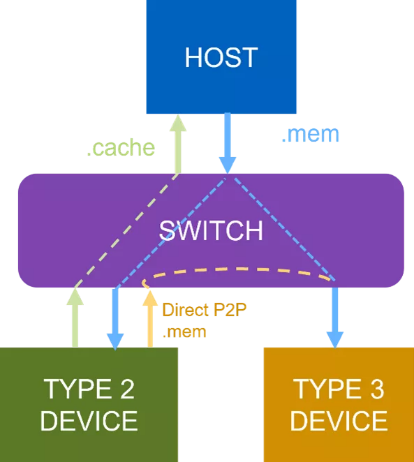

用于加速器的Direct P2P CXL.mem

扩展元数据

CXL fabric中的UIO直接点对点支持

GFAM扩展

可信执行环境安全协议

点对点通信

随着CXL的发展,内存设备和I/O设备都将具备多主机功能,如此一来便可通过CXL将其部分容量动态分配给各个主机。由于多路复用的机会增加,高度可组合的设计得以高效利用资源,进而降低成本。而这有助于利用CXL技术促进共享内存、消息传递和点对点通信,进而加速实现分布式系统。

在访问对等HDM-DB时,如果是通过主机访问对等HDM,设备将付出高昂的代价并会牺牲带宽。如果使用UIO(无序IO),则会牺牲一致性。CXL 3.1引入了一种新的非对称通道来克服此类带宽损失,从而使Type 1-2加速器能够以完整的CXL带宽并保证缓存一致性地访问对等内存。

可信执行环境安全协议

CXL生态系统正不断发展,我们需要一个机制来开发一种严格的方法,用于控制错误并管理CXL的扩展。之前提到过,我们正在设计可组合的系统,其中的组件可随时连接到虚拟机,但这引起了对于机器或硬件安全性的担忧。

每台设备都需要执行相应的功能并进行加密,以便与数据中心的虚拟机交换密钥。但这个过程可能很复杂,且存在诸多问题。

CXL 3.1引入了一种模型,专注于为直连CXL内存提供可信计算支持。直连内存是指内存设备(“目标”)和主机的CXL RP使用CXL协议进行通信,两者之间不需要中间层。

CXL 3.1规范中的扩展元数据是什么?

元数据是通过互连来传输每个缓存行时所需携带的附加信息,不被视为数据,且存储在缓存层次结构和内存子系统中。

例如,内存标记信息可携带作为缓存行的一部分。

256B FLIT模式中引入了Trailer位(最多32位),用于容纳此EMD信息。

CXL 3.1规范中的UIO直接点对点支持是什么?

随着系统的扩展,诸如CXL内存池等概念将引发本地和分布式内存管理的变革。为此,需要一种系统级方法来缓解分布式内存结构中的拥塞和故障问题。CXL标准中的QoS目前仅限于CXL.mem,且无法解决结构拥塞问题。CXL 3.1引入了一种机制,其中UIO请求者/设备可在系统拥塞时访问另一个目标/设备。有时,CXL交换机支持将UIO访问路由至与UIO请求者位于同一虚拟机中的HDM。

CXL 3.1验证所面临的挑战

交换机拓扑层出不穷,由交换机驱动的功能也需要系统级的配置和设置。为确保传输功能正常运行,需对交换机行为展开验证。其中一些行为可在事务和数据链路层验证,但对于较为复杂的交换机行为,就需要在多主机和多设备环境中进行验证。

安全功能涵盖软件、固件和硬件。在设计和验证特定层的实现时,必须了解其将如何满足整体安全要求。

3.1规范新增了许多特性,使得保持先前版本规范的向后兼容性和功能正确性变得愈加困难。但是,善加利用经过验证的设计IP和验证IP却越来越重要。

新思科技CXL 3.1验证解决方案

新思科技一直积极参与开发,并与业内领先企业保持紧密合作,致力于为最新CXL 3.1规范的功能特性和用例提供支持。

针对CXL 3.1,新思科技提供了验证IP(VIP)、测试套件和协议解决方案,由此打造出了一套全面的协议、方法、验证和效率功能,使开发者能够加速实现验证收敛。合作伙伴可利用新思科技广泛的互连产品组合,提前对设计进行验证。

新思科技IP使用独立开发的VIP进行验证,为各大公司提供出色的CXL解决方案。完整的开箱即用解决方案让开发者能够专注于芯片设计特性和差异化,以加快产品上市。

新思科技VIP原生集成了Verdi协议分析器调试解决方案和Verdi性能分析器。为了在SoC上运行系统级有效载荷,需要更快的、基于硬件的流片前解决方案。基于新思科技IP的事务处理器、内存模型、混合和虚拟解决方案可在业界最快的验证硬件、ZeBu硬件加速解决方案和HAPS原型系统上实现各种验证和验证用例。

-

FPGA

+关注

关注

1625文章

21665浏览量

601738 -

新思科技

+关注

关注

5文章

787浏览量

50302 -

机器学习

+关注

关注

66文章

8375浏览量

132398

原文标题:新思科技验证IP(VIP)如何加速验证CXL3.1设计?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

新思科技推出全新原生汽车解决方案,高效实现和验证功能安全机制

新思科技ZeBu Server 4仿真解决方案帮助NEC进行超级计算机验证

什么是思科CleanAir解决方案?

新思科技发布业界首款全栈式AI驱动型EDA解决方案Synopsys.ai

新思科技发布业界首款集成化混合原型验证解决方案

新思科技Synphony HLS解决方案

NEC使用新思科技仿真解决方案来验证超级计算机

DesignWare CXL为SoC提供优化的多芯片IP堆栈

新思科技推出最新IC Validator物理验证解决方案

新思CXL2.0验证IP,加速连接新一代互联技术

新思科技推出新一代开放标准互联技术CXL

三星已认证新思科技PrimeLib统一库表征和验证解决方案

SK hynix公司使用是德科技PCIe测试解决方案验证计算快速链路技术

新思科技设计、验证和IP解决方案助力Arm全面计算战略

新思科技PCIe 7.0验证IP(VIP)的特性

新思科技CXL 3.1验证解决方案

新思科技CXL 3.1验证解决方案

评论