随着集成电路工艺技术的不断发展,为了提高集成电路的集成度,同时提升器件的工作速度和降低它的功耗,集成电路器件的特征尺寸不断按比例缩小,工作电压不断降低。为了有效抑制短沟道效应,除了源漏的结深不断降低和沟道的掺杂浓度也不断增加外,栅氧化层的厚度也不断降低,从而提高栅电极电容,达到提高栅对沟道的控制能力,同时调节阈值电压。栅氧化层的厚度是随着沟道长度的减小而近似线性降低的,每一代大概是前一代的0.7倍左右,从而获得足够的栅控能力。另外,随着栅氧化层厚度的不断降低,MOS 管的驱动能力也会相应提高。

20 世纪60年代,最初的栅极材料是铝金属,氧化层的介质层是纯二氧化硅,栅极叠层结构是由纯二氧化硅和金属栅极组成。后来开发出多晶硅栅极,栅极叠层结构变为由纯二氧化硅和重掺杂的多晶硅栅极组成。因为通过多晶硅栅极可以实现自对准,另外也可通过调节掺杂多晶硅栅的类型调节器件的阈值电压。NMOS 栅极的多晶硅掺杂类型是n 型,PMOS栅极的多晶硅掺杂类型是p 型。对于厚度大于4nm 的栅氧化层,它是理想的绝缘体,因为SiO2的禁带宽度高达9eV,Si的禁带宽度是1.12eV,它们之间会形成巨大的势垒高度,在器件正常的偏置电压的条件下,电子或者空穴不可能越过栅氧化层与硅形成的势垒,所以不会形成栅极漏电流。

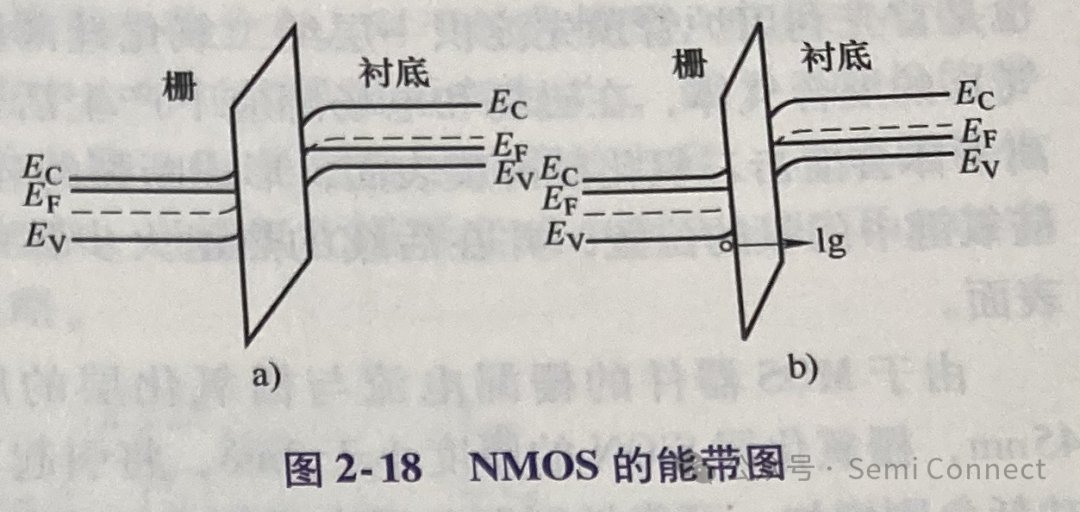

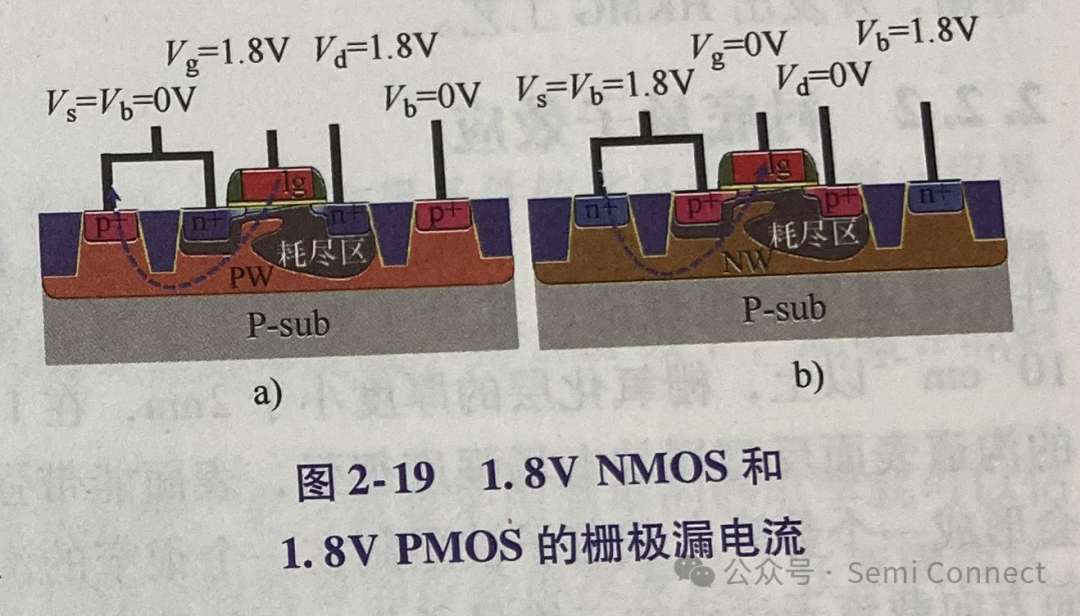

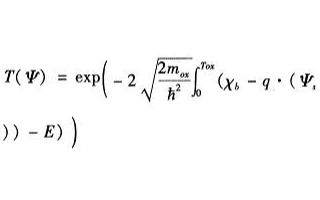

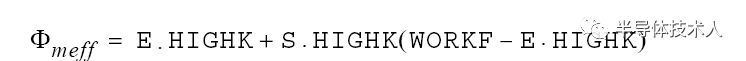

图2-18所示为 NMOS的能带图,图2-18a 是栅氧化层的厚度大于4nm,衬底与栅之间没有形成明显的漏电流。随着栅氧化层厚度的不断降低,当纯二氧化硅的厚度小于3nm 时,它不再是理想的绝缘体,栅极与衬底之间将会出现明显的量子隧穿效应,衬底的电子以量子的形式穿过栅介质层进入栅,形成栅极漏电流。栅极漏电流会随着栅氧化层厚度的减小而呈现指数级增长,栅氧化层物理厚度每减小0.2nm,隧穿电流就增大10倍,栅极漏电流增加会导致集成电路的功耗急剧增加,功耗增加导致集成电路发热从而影响集成电路的可靠性。另外,PMOS多晶硅栅极中的硼离子也会穿过栅介质层进入衬底,导致阈值电压漂移。图2-18b是栅氧化层的厚度小于3nm 时,多晶硅栅极的空穴不再进入栅氧化层的价带,而是表现为波动性,直接以量子的形式隧穿栅氧化层的梯形势垒,进入衬底形成漏电流。图2-19所示为1.8V NMOS 和1.8V PMOS 的栅极漏电流方向。NMOS 的栅极漏电流是由栅极流向衬底,PMOS 的栅极漏电流是由衬底流向栅极。

当集成电路器件的特征尺寸进入0.18μm时,栅氧化层的厚度小于3nm,半导体业界利用SiON 代替纯二氧化硅作为栅氧化层的介质层的材料。SiON 具有三方面的优点:第一点是SiON具有较高的介电常数,在相同等效栅电容的情况下,SiON 会具有更厚的物理氧化层;第二点是 SiON具有较高的电子绝缘特性,在相同物理厚度的情况下,利用SiON 作为栅氧化层的栅极漏电流大大降低;第三点是 SiON 中的氮元素对PMOS 多晶硅栅极掺杂的硼离子具有较好的阻挡作用,SiON可以防止硼离子在热退火处理的过程中扩散并越过栅氧化层到达衬底的沟道中影响器件的阈值电压。

早期生长栅氧化层 SiON 材料是利用炉管预先淀积一层纯二氧化硅薄膜,然后再利用原位和非原位热处理氮化二氧化硅薄膜形成 SiON 薄膜,氮化的气体是N2O、NO 和NH3中的一种或几种。这种工艺技术简单,缺点是掺杂氮元素的含量太少,对硼离子的阻挡作用有限,并且SiON 中的复元素不是均匀分布在栅氧化层中的,它主要分布在靠近SiO2和Si衬底的界面,造成SiO2和Si 衬底之间的界面缺陷,会导致沟道的载流子散射,降低载流子的迁移率。用炉管热处理氮化得到的氮氧化硅(SiON)主要应用于工艺特征尺寸在0.11μm及以上的工艺技术。

随着工艺特征尺寸进入90nm 及以下,栅氧化层厚度缩小到2nm 左右,栅极漏电流和硼离子扩假变得越来越严重,这就要求作力栅氧化层的氮氧化硅的氮元素含量越来越高,同时使它靠近上表面从而改善SiO2和Si衬底之间的界面。更先进的等离子氮化工艺被应用于生长栅氧化层SiON材料,以提高栅介质层中的氮含量,并较好的控制氮的分布。这种技术也是首先利用炉管预先淀积一层纯二氧化硅薄膜,然后利用氮气和惰性气体(如氦气或氩气)的混合气体,在磁场和电场感应下产生活性极强的氮等离子体,同时活性极强的氮等离子体会撞击二氧化硅薄膜表面,形成断裂的硅氧键,活性极强的氮离子会取代部分断裂的硅氧键中的氧的位置,并在后续的热退火步骤中形成稳定的硅氮键,从而使氮元素靠近上表面。

由于MOS器件的栅漏电流与栅氧化层的厚度成指数关系,随着工艺特征尺寸进入45nm,栅氧化层 SiON的厚度小于2nm,将引起不希望的高栅漏电流,导致整个芯片的待机功耗急剧增加、可靠性问题和栅介质层完整性问题,所以用由SiON 和多晶硅组成的栅极叠层结构已经不能满足 MOSPET 器件高性能的要求。另外,NMOS 栅极漏电流是栅氧化层物理厚度缩小的主要制约因素,NMOS的栅漏电流是 PMOS栅漏电流的10 倍,因为栅漏电流主要是由载流子的隧穿引起的,而空穴隧穿要通过更高的势垒。

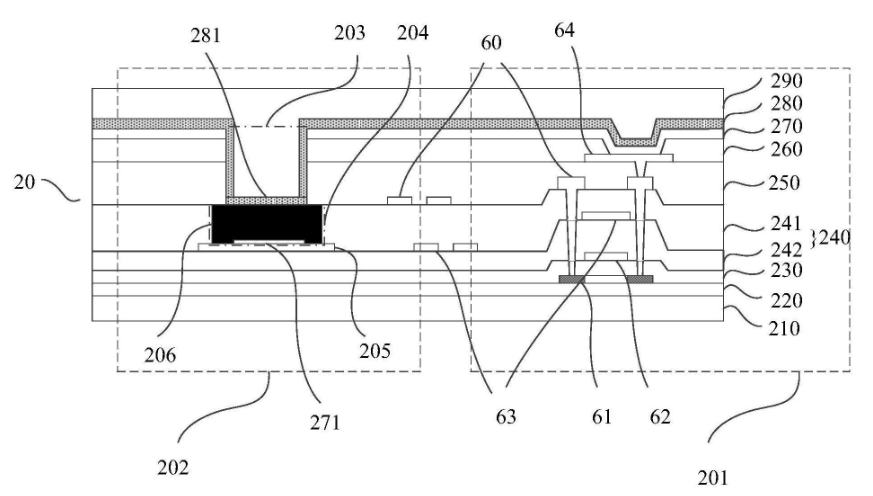

2007年1月,Intel 公司宣布在45nm 技术节点利用新型High-k(高K介电常数)介质材料HfO2,来代替传统 SiON 作为栅介质层来改善栅极漏电流问题,同时利用金属栅代替多晶硅栅,开发出HKMG工艺。

-

集成电路

+关注

关注

5396文章

11643浏览量

363708 -

MOS管

+关注

关注

108文章

2448浏览量

67746 -

NMOS

+关注

关注

3文章

296浏览量

34620

原文标题:栅介质层的发展和面临的挑战

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是MOSFET栅极氧化层?如何测试SiC碳化硅MOSFET的栅氧可靠性?

集成电路的发展趋势与设计挑战

片式叠层陶瓷介质电容器基础介绍

【转】一文看懂MOS器件的发展与面临的挑战

分析MOS管未来发展与面临的挑战

高介电栅介质材料研究进展

MOSFET栅漏电流噪声特性、模型的特性和局限性研究分析

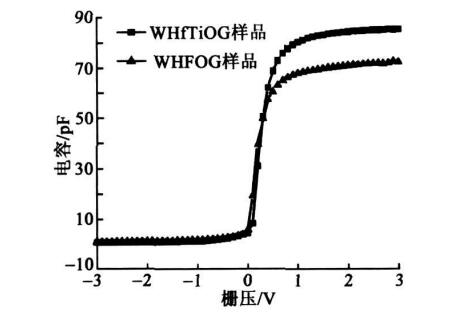

一文读懂HfTiO高栅介质GeMOS电容

高迁移率二维半导体Bi2O2Se的紫外光辅助插层氧化方法

高k栅介质NMOSFET远程声子散射对沟道迁移率的影响

未来是什么材料的世界?探索介质层材料的新趋势和挑战

栅介质层的发展和挑战

栅介质层的发展和挑战

评论