本文要点

超大规模集成电路 (Very large scale integration,VLSI) 是一种主流的集成电路 (IC) 设计模式。

芯片尺寸微型化有助于降低单个晶体管的功耗,但同时也提高了功率密度。

先进封装的低功耗设计趋势势头未减,而更新的技术有助于在不牺牲计算性能的情况下降低器件的功耗。

如今的集成电路 (IC) 与二十多年前的集成电路有着天壤之别。新一代的芯片面积更小,但集成了尽可能多的功能,采用了先进的处理节点和独特的架构,以实现整个芯片的高能效信号传输。摩尔定律所涉及的不仅是晶体管栅极尺寸变小,也涵盖了低功耗架构。

随着电子产品的尺寸不断微型化,芯片设计人员需要考虑采用新的方法来实现和扩展低功耗设计技术。用于数据中心、人工智能、视觉和许多其他应用的处理器性能强大,集成的功能也越来越多,因此预计 VLSI 设计的功率密度也会增加。低功耗设计技术和新技术可以应对总功耗增加的挑战,确保新产品性能可靠,并支持扩展到更小的技术节点。

即使采用了低功耗设计工艺,GPU 仍会严重发热

1

功耗的主要方面

许多先进集成电路(如专用 SoC 和通用处理器)中使用了较新的芯片架构,需要在裸片上集成更多的功能,因此需要增加硬件驱动的电源管理功能。实施低功耗设计技术的目标主要是延长电池寿命(移动设备)、减少发热(所有其他设备)或两者兼顾(智能手机和其他移动设备)。VLSI 设计中的低功耗设计技术一般在两个方面进行功耗优化:

1.动态功耗

动态功耗是指工作过程中消耗的电量。更具体地说,动态功耗是在逻辑电路切换状态时,晶体管结构中电容充放电时消耗的总电量。CMOS 逻辑电路只在开关时消耗电量,因此减少开关事件的次数和导通电压有助于降低设备的总功耗。

2.静态功耗

静态功耗是工作电压和漏电流的乘积。即使晶体管处于关断状态,也会有一些电流通过栅极泄漏,以热量的形式散失。与早期的双极设计相比,CMOS 芯片架构的漏电流更低,但规模扩展给保持低漏电流带来了挑战。

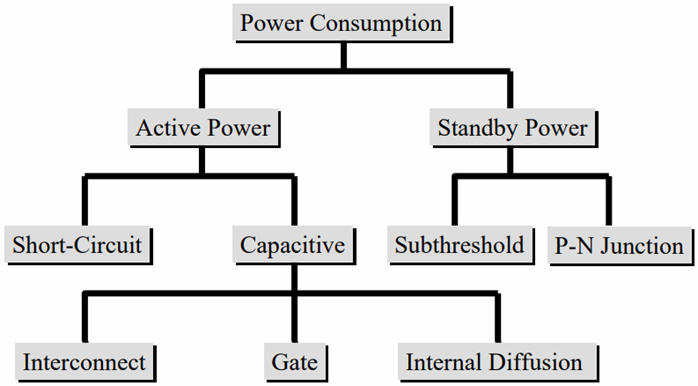

下图展示了集成电路在运行和睡眠/待机模式下产生功耗的一些区域和工作模式:

VLSI 电能耗散和损耗的来源

降低以上功耗主要针对静态和动态功耗,但随着器件规模的扩大,还需要调整晶体管和互连的结构。我们在这方面取得了一些进展,其中最主要的是使用具有高介电常数 (high-k) 的 FinFET,以确保在开关过程中更完整地调制到导通状态,并通过单一解决方案降低漏电流。对于更新的技术,需要利用类似的创新晶体管架构和新材料来实现进一步扩展。除了简单的架构扩展外,一些晶片上硬件方法也可用于降低功耗。

2

主要的低功耗设计技术

经过 30 多年的发展,出现了一些解决方案。最初,扩展带来了更低的功耗和更高的功能密度,但最终,时钟扩展增加了功率密度,因此亟需新的技术。如今,集成电路中使用的低功耗设计技术主要包括:

1

动态电压缩放

逻辑电平的电压可根据需要升高或降低,以控制功耗。降低逻辑电平可降低开关时的功耗。

2

动态频率缩放

系统时钟的时钟频率和边沿速率可根据需要上下调节。

3

时钟门控

用于切断某些逻辑块的系统时钟,防止不处理数据的逻辑电路进行开关操作。

4

基板偏置控制

与电压缩放配合使用,控制构成逻辑电路的 MOSFET 进入线性区或饱和区的阈值。该技术有时也称为反向偏置,即在 CMOS 缓冲器的基板区域施加电压,以提高或降低逻辑状态阈值电压并减少漏电流。

应用这些主动缩放机制时,并不一定需要修改逻辑电路中晶体管的结构,不过为此确实需要添加额外的控制电路,以便根据某些逻辑条件进行缩放。

3

新产品可能需要采用独特的架构

以上列出的低功耗设计技术是设计新型专用集成电路 (ASIC) 的起点,面向人工智能、量子、视觉/图形和异构集成系统等高级应用。对于支持上述应用的通用处理器,也应继续使用同样的技术。然而,特定应用领域的计算工作负载更高,因此功耗更低的高度专业化处理器架构更加受到青睐。这方面的例子包括:

以最少的逻辑运算执行高效张量运算的 AI 优化芯片。

可针对特定的高计算工作量对其逻辑块进行高度定制或并行化的 FPGA。

包含专用 DSP 块的语音和视觉处理器。

异构集成是将这些功能整合到单一封装中的一种设计模式,迫使半导体电源管理工程师采用系统级方法进行低功耗设计。

尤其是,人工智能是当下的计算范式,它推动了一类新型低功耗 ASIC 的高效张量运算。为了让这些先进产品实现低功耗,涉及到的挑战之一是完全重新设计晶体管架构,以减少执行人工智能工作负载所需的开关事件数量和逻辑状态变化。最新的设计采用单晶体管模拟计算方法来实现片上神经网络,完全不需要逻辑块来运行这些计算。其他先进技术、材料平台和混合信号设计方法可在专用集成电路和通用处理器中实现,因而可以随着功能密度的提高,继续推动低功耗计算。

借助业界一流的 VLSI 设计软件和系统分析工具,您可以轻松构建、仿真和评估您的设计,最大限度地降低整个系统——而不仅仅是 CPU 内核——的功耗。如果您需要在物理 layout 中实现低功耗设计,Cadence Sigrity X 工具套件可以助您一臂之力——新一代 Sigrity 解决方案重新定义了 SI 和 PI 分析,将性能提高了 10 倍,同时保持了 Sigrity 工具一贯的准确性;不仅配备了强大的系统级分析仿真引擎,旗舰产品 Cadence Clarity 3D Solver 更采用了创新的大规模分布式架构,同时与 Cadence Allegro X PCB Designer 和 Allegro X Advanced Package Designer 紧密集成。

这一全新特性可以帮助 PCB 和 IC 封装设计师将端到端、multi-fabric和多电路板系统(从发射端到接收端或从电源到耗电端)相结合,确保 SI/PI 成功签核。

-

集成电路

+关注

关注

5388文章

11549浏览量

361897 -

低功耗设计

+关注

关注

0文章

80浏览量

16164 -

电源完整性

+关注

关注

9文章

209浏览量

20731 -

VLSI

+关注

关注

0文章

73浏览量

42917

发布评论请先 登录

相关推荐

超大规模集成电路计算机辅助设计技术

中文版《CMOS超大规模集成电路设计》第4版

超大规模集成电路的生产工艺流程

《炬丰科技-半导体工艺》超大规模集成电路制造技术简介

超大规模集成电路技术

超大规模集成电路电子学

超大规模集成电路及其生产工艺流程

超大规模集成电路设计导论-杨之廉

如何利用低功耗设计技术实现超大规模集成电路(VLSI)的电源完整性?

如何利用低功耗设计技术实现超大规模集成电路(VLSI)的电源完整性?

评论