来源:芝能芯芯

半导体行业的不断进步和技术的发展,3D-IC(三维集成电路)和异构芯片设计已成为提高性能的关键途径。然而,这种技术进步伴随着一系列新的挑战,尤其是在热管理和布局规划方面。

我们探讨3D-IC和Chiplet设计所带来的挑战及其对物理布局工具的影响,并讨论EDA(电子设计自动化)供应商如何应对这些挑战。

Part 1

3D-IC 和异构芯片出现对设计带来的影响

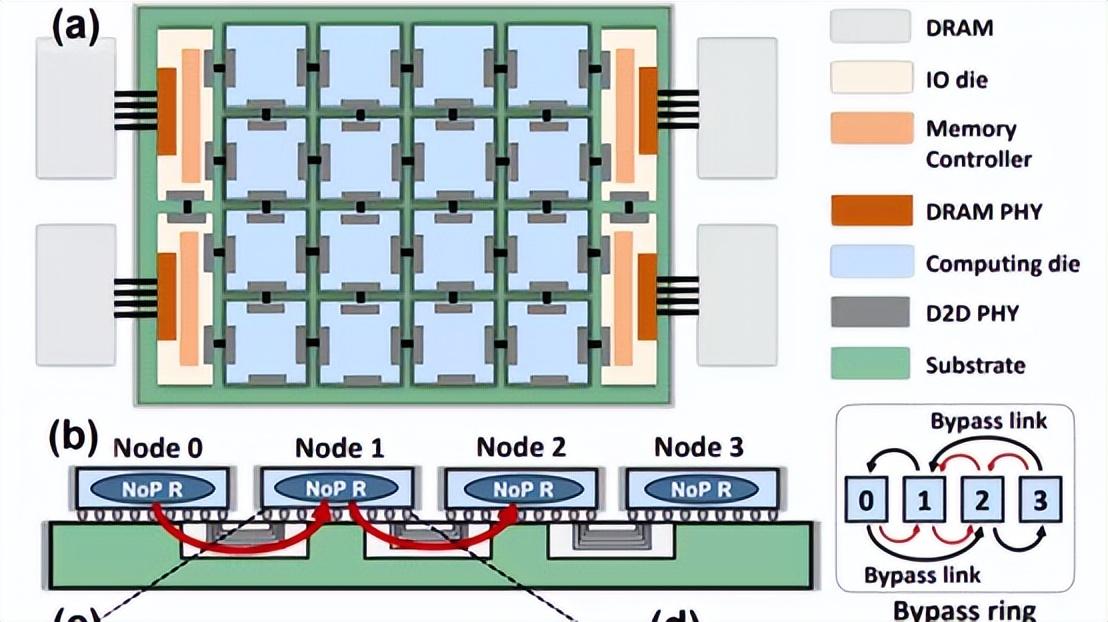

3D-IC 和异构芯片的出现要求对物理布局工具进行重大变革。芯片的放置和信号布线对整体系统性能和可靠性有着至关重要的影响。散热成为 3D-IC 面临的首要难题,逻辑芯片的堆叠导致热量产生增加,而减薄基板虽缩短了信号传输距离,却降低了传热能力,散热器也不再适用。

解决方法在于精心配置芯片层,使热量分散或限制在可有效散热的区域,这需要内置到自动化工具中。例如,在实际应用中,若将高性能计算芯片进行 3D 堆叠,由于其高功率运行产生的大量热量,若布局规划不合理,可能导致局部过热,影响芯片性能和稳定性。

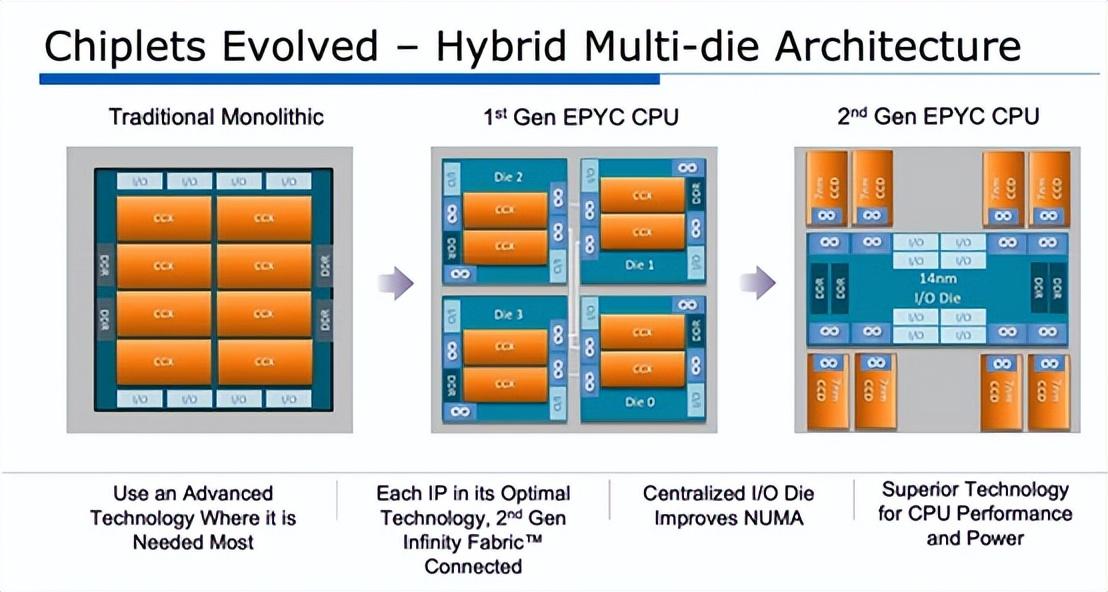

布局规划、布局、时钟和布线是布局布线流程的主要阶段。布局规划探索在流程早期进行,确定功能模块的位置和连接性。随着技术发展,从传统的平面设计转变为 3D 设计,设计变得更为复杂,需要考虑更多维度的因素,如芯片间的耦合效应、电阻率和时序路径等。

在智能手机芯片设计中,不仅要考虑 CPU 和 GPU 的布局,还要考虑它们与内存芯片、通信芯片等在 3D 空间中的交互,以确保性能最优且散热良好。

Part 2

Chiplet设计的影响

Chiplet设计改变了传统的布局布线流程,需要对逻辑分区进行优化,并且在设计流程中必须考虑多芯片集成、异构技术以及高密度芯片间互连的复杂性。这要求EDA工具具备更强的多物理场模拟能力和智能化水平,以便更好地支持设计决策。

热效应在3D结构中尤为重要,因为热串扰可能影响设计的可靠性。为了管理这些效应,设计团队需要打破传统学科间的壁垒,将热模拟等多物理效应更早地引入设计过程。

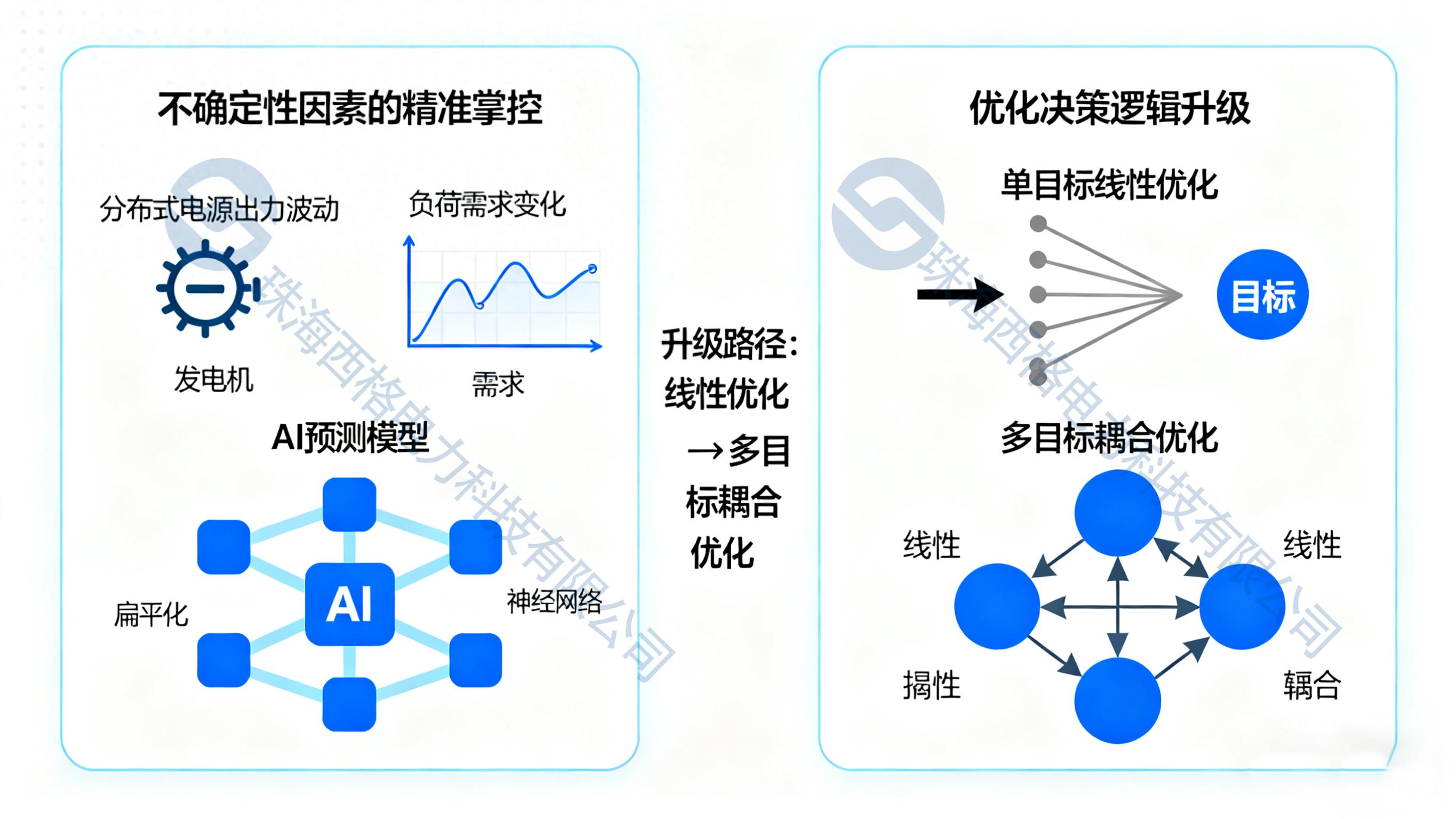

此外,由于电压/频率的动态变化会影响性能和计算吞吐量,因此需要进行瞬态热功率斜坡建模。

EDA供应商正在积极开发新一代工具,这些工具不仅能够处理传统信号完整性和电源完整性分析,还能支持热管理、信号完整性感知布线等高级功能。

此外,随着AI技术的进步,EDA工具正在整合更多的人工智能功能,以实现更高效的设计和优化。

随着Chiplet设计和3D-IC技术的进一步发展,EDA工具将继续进化以满足更高层次的设计要求。未来的设计流程将更加自动化,并利用机器学习和人工智能技术来预测和优化设计结果。

同时,跨领域合作将成为关键,以确保设计符合所有必要的约束条件。

3D-IC和Chiplet设计为半导体行业带来了前所未有的机遇和挑战。为了克服这些挑战,设计工具和流程必须不断发展以支持更先进的技术。EDA供应商正通过创新的方法来应对这些挑战,而随着技术的进步,我们可以期待在未来几年内看到更加高效和自动化的设计流程。

小结

随着行业逐步过渡到Chiplet时代,我们正处于一个转折点,这将对未来的电子产品产生深远影响。EDA工具和设计流程的持续创新将是确保这一转型成功的关键。

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54562浏览量

470361 -

chiplet

+关注

关注

6文章

500浏览量

13667

发布评论请先 登录

Chiplet,正在改变芯片制造

Cadence陈会馨:PCIe技术演进与AI时代的IP解决方案

如何设置HDI PCB布局?

TCP/IP(Socket)协议深度剖析

串口协议的深度剖析

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

从模拟到AI集成:图像采集卡的技术演进与未来三大趋势

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

Chiplet与先进封装全生态首秀即将登场!汇聚产业链核心力量共探生态协同新路径!

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

剖析 Chiplet 时代的布局规划演进

剖析 Chiplet 时代的布局规划演进

评论