前言

我们聊聊芯片设计、流片、验证、制造、成本的那些事;流片对于芯片设计来说就是参加一次大考。

流片的重要性就在于能够检验芯片设计是否成功,是芯片制造的关键环节,也就是将设计好的方案交给芯片制造厂生产出样品。检测设计的芯片是否达到设计要求,或者是否需要进一步优化;如果能够生产出符合要求的芯片,那么就可以大规模生产了。

上图流程的输入是芯片立项设计,输出是做好的芯片晶圆。

一、晶圆术语

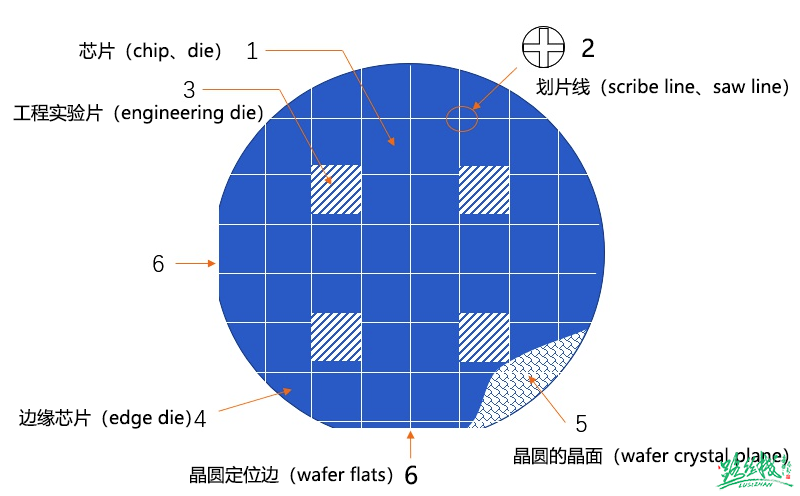

1. 芯片(chip、die)、器件(device)、电路(circuit)、微芯片(microchip)或条码(bar):所有这些名词指的是在晶圆表面占大部分面积的微芯片图形;

2. 划片线(scribe line、saw line)或街区(street、avenue):这些区域是在晶圆上用来分隔不同芯片之间的间隔区。划片线通常是空白的,但有些公司在间隔区内放置对准标记,或测试的结构;

3. 工程实验片(engineering die)和测试芯片(test die):这些芯片与正式芯片或电路芯片不同。它包括特殊的器件和电路模块用于晶圆生产工艺的电性测试;

4. 边缘芯片(edge die):在晶圆边上的一些掩膜残缺不全的芯片而产生的面积损耗。由于单个芯片尺寸增大而造成的更多边缘浪费会由采用更大直径晶圆所弥补。推动半导体工业向更大直径晶圆发展的动力之一就是为了减少边缘芯片所占的面积;

5. 晶圆的晶面(wafer crystal plane):图中的剖面标示了器件下面的晶格构造,此图中显示的器件边缘与晶格构造的方向是确定的;

6. 晶圆定位边(wafer flats)/凹槽(notche):图示的晶圆由注定位边(major flat)和副定位边(minor flat),表示这是一个P型<100>晶向的晶圆。300mm和450mm直径的晶圆都是用凹槽作为晶格导向的标识。这些定位边和凹槽在一些晶圆生产工艺中还辅助晶圆的套准。

二、芯片的流片方式(Full Mask、MPW)

Full Mask和MPW都是集成电路的一种流片(将设计结果交出去进行生产制造)方式。Full Mask是“全掩膜”的意思,即制造流程中的全部掩膜都为某个设计服务;而MPW 全称为Multi Project Wafer,直译为多项目晶圆,即多个项目共享某个晶圆,也即同一次制造流程可以承担多个IC设计的制造任务。

1.Full Mask,“全掩膜”,即制造流程中的全部掩膜都为某个设计服务;Full Mask的芯片,一片晶圆可以产出上千片DIE;然后封装成芯片,可以支撑大批量的客户需求。

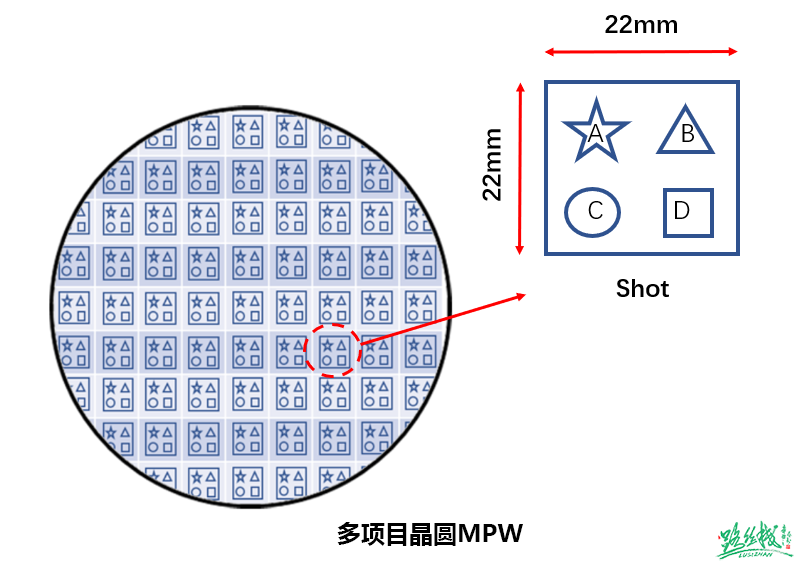

2.MPW全名叫Multi Project Wafer,和电路设计PCB的拼板打样类似,叫多项目晶圆。多项目晶圆就是将多个使用相同工艺的集成电路设计放在同一晶圆片上流片,制造完成后,每个设计可以得到数十片芯片样品,这一数量对于原型(Prototype)设计阶段的实验、测试已经足够。这种操作方式可以让流片费下降90%-95%,也就大幅降低了芯片研发的成本。

晶圆厂每年都会有固定的几次MPW机会,叫Shuttle (班车),到点即发车,是不是非常形象不同公司拼Wafer,得有个规则,MPW按SEAT来锁定面积,一个SEAT一般是3mm*4mm的一块区域,一般晶圆厂为了保障不同芯片公司均能参与MPW,对每家公司预定的SEAT数目会限制(其实SEAT多成本就上去了,MPW意义也没有了)。MPW优势投片成本小,一般就小几十万,可以很好降低风险;需要注意的是MPW从生产角度是一次完整的生产流程,因此其还是一样耗时间,一次MPW一般需要6~9个月,会带来芯片的交付时间后延。

因为是拼Wafer,因此通过MPW拿到的芯片数目就会很有限,主要用于芯片公司内部做验证测试,也可能会提供给极少数的头部客户。从这里大家可能已经了解了,MPW是一个不完整的,不可量产的投片。

3.晶圆生产角度介绍MPW

毕竟芯片加工还是一个相对复杂的过程,我相信很多朋友看完第一和小二之前理解的晶圆结构,是下图的,一个框归属于一个芯片公司。

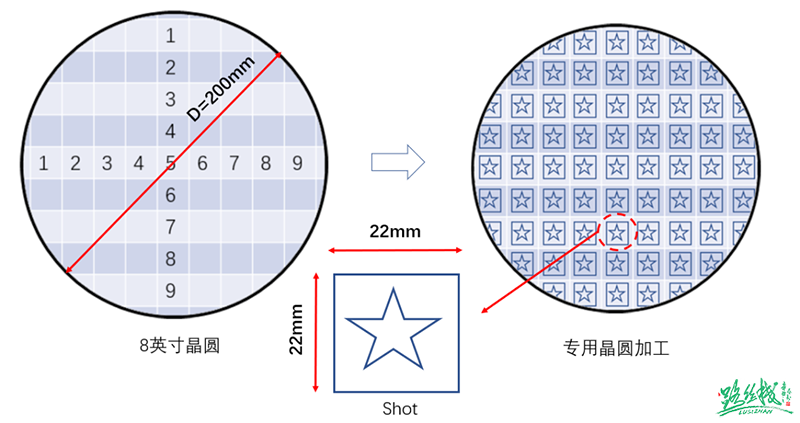

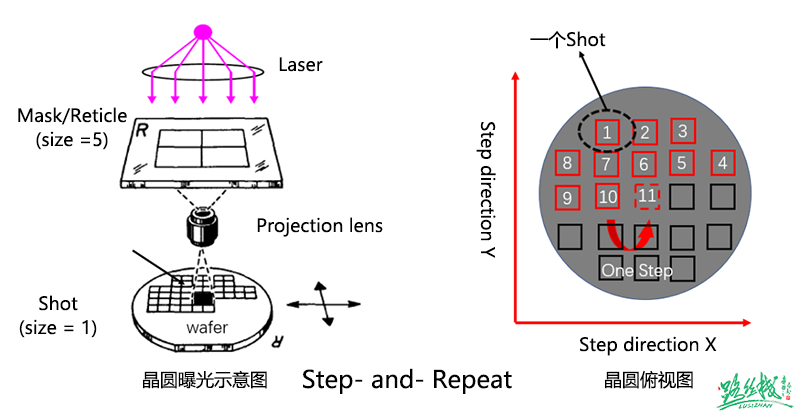

实则不然,这就需要和晶圆的生产流程的光刻技术相关了;现阶段的光刻技术DUV/EUV等,大多采用缩影的方式进行曝光,如下图所示:

采用1:5 放大的mask,对晶圆进行曝光,一次曝光的矩形区域通常称为一个shot,完成曝光后,自动调整晶圆位置,对下个shot进行曝光,如此循环(Step-and-Repeat),直到整个晶圆完成曝光,而这一个Shot的区域,则是大家一起分担SEAT的区域;

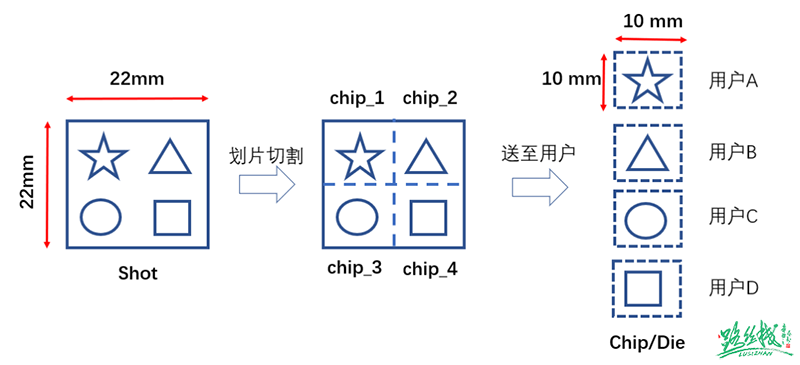

如下示意图中,一个Shot里面划分4个小格,每个格子给到一家厂商的设计,MPW晶圆一般20个以内用户。

三、芯片ECO流程

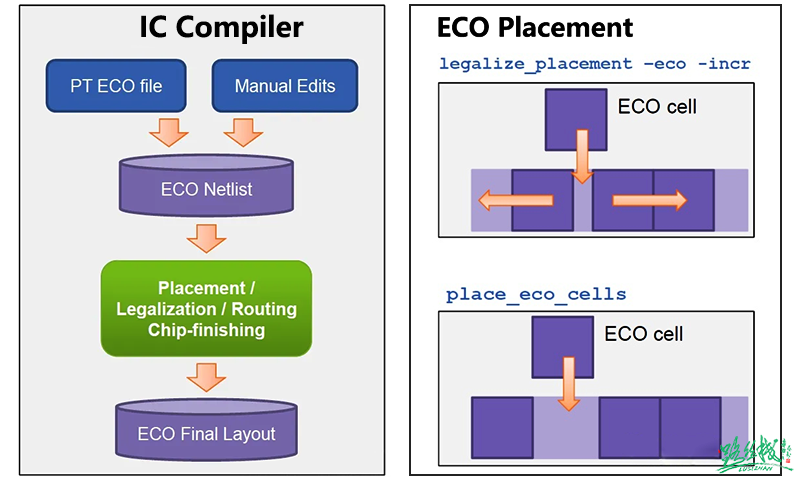

ECO 指的是Engineering Change Order,即工程变更指令。ECO可以发生在Tapeout之前,过程中,或者之后;Tapeout之后的ECO,改动少的可能仅需要改几层Metal layer,改动大可能需要动十几层Metal layer,甚至重新流片。ECO 的实现流程如下图所示:

如果MPW或者FullMask的芯片,验证有功能或者性能缺陷,通过ECO对电路和标准单元布局进行小范围调整,保持原设计布局布线结果基本不变的前提下做小规模优化,修复芯片的剩余违例,最终达到芯片的签核标准。不能通过后端布局布线的流程来修复违例(重新走一遍流程太费时了),而要通过ECO的流程来进行时序、DRC、 DRV以及功耗等优化。

四、流片Corner

1.Corner是芯片制造是一个物理过程,存在着工艺偏差(包括掺杂浓度、扩散深度、刻蚀程度等),导致不同批次之间,同一批次不同晶圆之间,同一晶圆不同芯片之间情况都是不相同的。

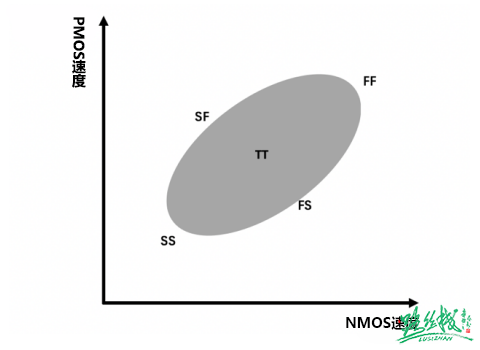

在一片wafer上,不可能每点的载流子平均漂移速度都是一样的,随着电压、温度不同,它们的特性也会不同,把他们分类就有了PVT(Process,Voltage,Temperature),而Process又分为不同的corner:TT:Typical N Typical P FF:Fast N Fast P SS:Slow N Slow P FS:Fast N Slow P SF:Slow N Fast P 第一个字母代表NMOS,第二个字母代表PMOS,都是针对不同浓度的N型和P型掺杂来说的。NMOS和PMOS在工艺上是独立做出来的,彼此之间不会影响,但是对于电路,NMOS和PMOS是同时工作的,会出现NMOS快的同时PMOS也快,或者慢,所以会出现FF、SS、FS、SF四种情况。通过Process注入的调整,模拟器件速度快慢,同时根据偏差大小设定不同等级的FF和SS。正常情况下大部分是TT,而以上5种corner在+/-3sigma可以覆盖约99.73%的范围,这种随机性的发生符合正态分布。

2.Corner wafer的意义在工程片流片的时候,FAB会pirun关键层次调整inline variation,有的还会下backup wafer以保证出货的wafer器件on target,即在TT corner附近。如果单纯是为了做一些样品出来,只进行工程片流片,那可以不验证corner,但如果为了后续量产准备,是必须要考虑corner的。由于工艺在制作过程中会有偏差,而corner是对产线正常波动的预估,FAB也会对量产芯片的corner验证有所要求。所以在设计阶段就要满足corner,在各种corner和极限温度条件下对电路进行仿真,使其在各种corner上都能正常工作,才能使最终生产出的芯片良率高。

3.Corner Split Table策略 对于产品来讲,一般corner做到spec上,正常情况下spec有6个sigma,如FF2(或2FF)表示往快的方向偏2个Sigma,SS3(或3SS)表示往慢的方向偏3个Sigma。Sigma主要表征了Vt的波动,波动大sigma就大,这里3个sigma就是在工艺器件的spec线上,可以允许超出一点点,因为线上波动不可能正正好好做到spec上。

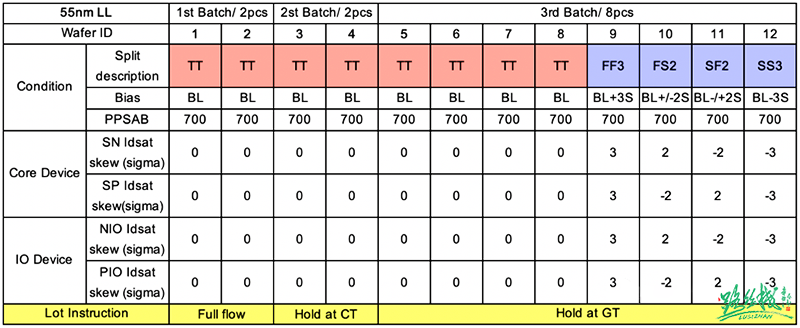

如下是55nm Logic工艺片的例,拟定的corner split table:

①#1 & #2 两片pilot wafer,一片盲封,一片测CP;

②#3 & #4 两片hold在Contact,为后道改版预留工程wafer,可以节省ECO流片时间 ;

③#5~#12 八片hold在Poly,等pilot的结果看是否需要调整器件速度,并验证corner;

④除了留有足够的芯片用于测试验证,Metal Fix,还应根据项目需求,预留尽可能多的wafer作为量产出货。

4.确认Corner结果

首先,大部分都应该落于四个corner决定的window范围内,如果出现大的偏差,那可能是工艺shift。如果各个corner的良率都没影响符合预期,那说明工艺窗口充分。如果有个别条件良率低,那就需要调整工艺窗口。Corner wafer的目的是验证设计余量,考察良率是否有损失。大体上,超出这个corner约束性能范围内的芯片报废。

Corner验证对标的是WAT测试结果,一般由FAB主导,但是corner wafer的费用是由设计公司承担的。一般成熟稳定的工艺,同一片wafer上的芯片,同一批次的wafer甚至不同批次的wafer参数都是很接近的,偏差的范围相对不会很大。工艺角(Process Corner)PVT(Precess Voltage Temperature)工艺误差与双极晶体管不同,在不同的晶片之间以及在不同的批次之间,MOSFETs参数变化很大。

为了在一定程度上减轻电路设计任务的困难,工艺工程师们要保证器件的性能在某个范围内,大体上,他们以报废超出这个性能范围的芯片的措施来严格控制预期的参数变化。

①MOS管的快慢分别指阈值电压的高低,快速对应阈值低,慢速对应阈值高。GBW=GM/CC ,其它条件相同情况下,vth越低,gm值越高,因此GBW越大,速度越快。(具体情况具体分析)

②电阻的快慢。fast对应的是方块电阻小,slow对应的是方块电阻大。

③电容的快慢。fast对应的是电容最小,slow对应的是容值最大。

五、流片成本和晶圆价格

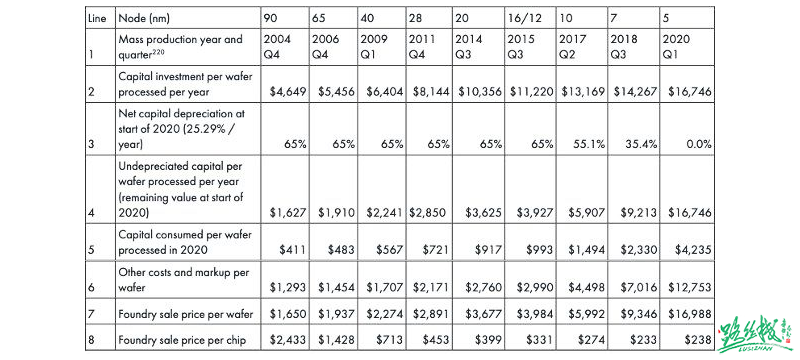

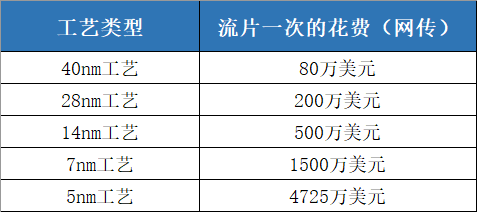

40nm的流片Mask成本大概在80-90万美元,晶圆成本每片在3000-4000美元左右,加上IP merge,七八百万人民币跑不掉了。

28nm工艺流片一次需要200万美元;14nm工艺流片一次需要500万美元;7nm工艺流片一次需要1500万美元;5nm工艺流片一次4725万美元;3nm工艺流片可能要上亿美元;掩膜版、晶圆这两项主要流片成本中,掩膜版最贵。

越先进的工艺节点,所需要的掩膜版层数就越多;因为每一层“掩膜板”对应涂抹一次光刻胶、曝光、显影、刻蚀等操作,涉及材料成本、仪器折旧成本,这些成本都需要fabless客户买单!

28nm大概需要40层,14nm工艺需要60张掩膜版;7nm工艺需要80张甚至上百张掩膜版;一层Mask 8万美金,因此芯片必须量产,拉低成本!

40nm MCU工艺为例:如果生产10片晶圆,每片晶圆成本(90万+ 4000*10)/10=9.4万美元;生产10000片晶圆,每片晶圆成本(90万+4000*10000)/10000=4090美元。(晶圆量越大越便宜,不同产家报价也不一样。)

晶圆代工价格来源于网络

台积电今年给的最新报价:最先进的制程3nm,每片晶圆19865美元,折合人民币大概14.2w左右。

结语

芯片从设计到成品有几个重要环节,分别是设计->流片->封装->测试,但芯片成本构成的比例确大不相同,一般为人力成本20%,流片40%,封装35%,测试5%。

芯片流片是高风险的事情,这个风险有多高,这个概率在15%-35%左右;不同的团队和芯片种类概率也不一样。有模拟芯片公司即使在团队完备、思路清晰的情况下,还是耗了8年时间,历经18次流片,才最终完成了传感器模拟计算IP验证,打造出了理想中的那颗超低功耗、超近传感芯片。

-

晶圆

+关注

关注

52文章

4956浏览量

128176 -

芯片设计

+关注

关注

15文章

1026浏览量

54951 -

芯片验证

+关注

关注

5文章

34浏览量

47250 -

流片

+关注

关注

0文章

28浏览量

9788

发布评论请先 登录

相关推荐

片上网络核心芯片的验证

讲讲芯片的流片制造那些事儿

是德科技使用数字孪生信令实现先进的半导体流片原型设计

国芯科技:正在流片验证chiplet芯片高性能互联IP技术

聊聊芯片设计、流片那些事

芯片设计流片、验证、成本的那些事

芯片设计流片、验证、成本的那些事

评论