边沿触发器(Edge Triggered Flip-Flop)是一种数字电路中的基本存储单元,它能够存储一位二进制信息。边沿触发器的特点是只有在时钟信号的上升沿或下降沿到来时才能改变输出状态。这种触发方式可以有效地减少电路的功耗和提高电路的稳定性。边沿触发器有多种类型,下面介绍几种常见的边沿触发器类型。

- D触发器(Data Flip-Flop)

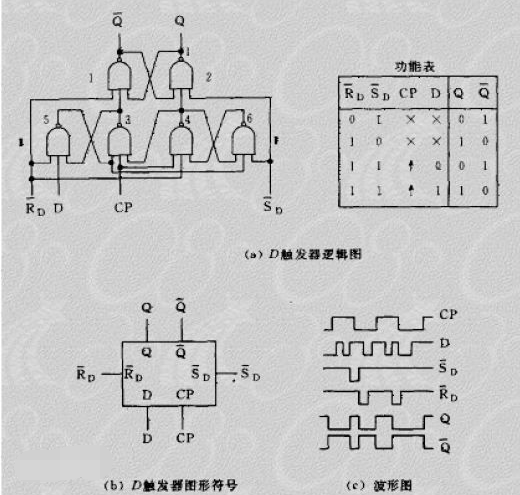

D触发器是一种最基本的边沿触发器,它具有一个数据输入端(D)、一个时钟输入端(CLK)和一个输出端(Q)。D触发器的功能是将数据输入端的二进制信息在时钟信号的上升沿或下降沿到来时存储到触发器中,并在输出端产生相应的二进制信号。

D触发器的工作原理如下:

- 当CLK信号为低电平时,无论D输入端的信号如何变化,Q输出端的信号保持不变。

- 当CLK信号从低电平跳变到高电平时,Q输出端的信号将跟随D输入端的信号变化。

- 当CLK信号从高电平跳变到低电平时,Q输出端的信号保持不变。

D触发器可以用各种逻辑门实现,如与非门、或非门等。D触发器在数字电路设计中应用广泛,如寄存器、计数器、移位寄存器等。

- JK触发器(J-K Flip-Flop)

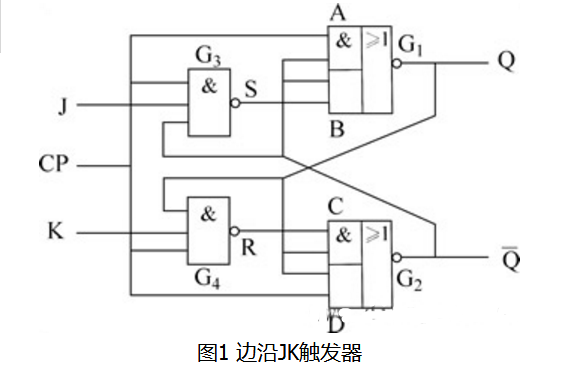

JK触发器是一种具有两个输入端(J和K)的边沿触发器。JK触发器的功能是将J和K输入端的二进制信息在时钟信号的上升沿或下降沿到来时进行逻辑运算,并在输出端产生相应的二进制信号。

JK触发器的工作原理如下:

- 当CLK信号为低电平时,无论J和K输入端的信号如何变化,Q输出端的信号保持不变。

- 当CLK信号从低电平跳变到高电平时,根据J和K输入端的信号,Q输出端的信号将按照以下规则变化:

- 如果J=0,K=0,则Q保持不变。

- 如果J=0,K=1,则Q清零。

- 如果J=1,K=0,则Q置位。

- 如果J=1,K=1,则Q取反。

JK触发器可以用D触发器实现,也可以使用其他逻辑门实现。JK触发器在数字电路设计中应用广泛,如寄存器、计数器、移位寄存器等。

- T触发器(Toggle Flip-Flop)

T触发器是一种具有一个输入端(T)的边沿触发器。T触发器的功能是在时钟信号的上升沿或下降沿到来时,将输出端的二进制信号取反。

T触发器的工作原理如下:

- 当CLK信号为低电平时,无论T输入端的信号如何变化,Q输出端的信号保持不变。

- 当CLK信号从低电平跳变到高电平时,Q输出端的信号将取反。

- 当CLK信号从高电平跳变到低电平时,Q输出端的信号保持不变。

T触发器可以用D触发器和非门实现,也可以使用其他逻辑门实现。T触发器在数字电路设计中应用广泛,如寄存器、计数器、移位寄存器等。

- RS触发器(Set-Reset Flip-Flop)

RS触发器是一种具有两个输入端(S和R)的边沿触发器。RS触发器的功能是将S和R输入端的二进制信息在时钟信号的上升沿或下降沿到来时进行逻辑运算,并在输出端产生相应的二进制信号。

RS触发器的工作原理如下:

- 当CLK信号为低电平时,无论S和R输入端的信号如何变化,Q输出端的信号保持不变。

- 当CLK信号从低电平跳变到高电平时,根据S和R输入端的信号,Q输出端的信号将按照以下规则变化:

- 如果S=0,R=0,则Q保持不变。

- 如果S=0,R=1,则Q清零。

- 如果S=1,R=0,则Q置位。

- 如果S=1,R=1,则Q的输出状态不确定。

RS触发器可以用D触发器和逻辑门实现,也可以使用其他逻辑门实现。RS触发器在数字电路设计中应用广泛,如寄存器、计数器、移位寄存器等。

-

存储单元

+关注

关注

1文章

64浏览量

16229 -

数字电路

+关注

关注

193文章

1631浏览量

81076 -

时钟信号

+关注

关注

4文章

455浏览量

28784 -

边沿触发器

+关注

关注

0文章

34浏览量

4050

发布评论请先 登录

相关推荐

CMOS触发器在CP边沿的工作特性研究

边沿触发SR触发器

什么是边沿触发器_边沿D触发器介绍

常用边沿触发器电路结构和工作原理

脉冲和边沿触发器区别

边沿触发器的类型有哪些

边沿触发器的类型有哪些

评论