主从触发器,也被称为主从同步触发器或主从锁存器触发器,是一种在数字电路设计中广泛使用的触发器类型。它主要用于防止亚稳态现象,提高电路的稳定性和可靠性。

- 主从触发器的工作原理

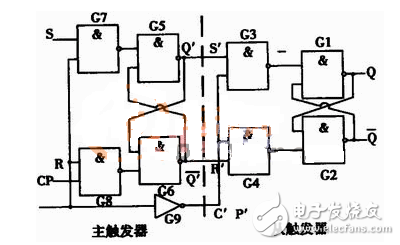

主从触发器由两个触发器组成,一个是主触发器,另一个是从触发器。主触发器负责接收输入信号,从触发器负责存储输出信号。在主触发器接收到输入信号后,它会将信号传递给从触发器,从触发器在接收到信号后,将信号存储起来,并输出给后续电路。

主从触发器的工作原理可以分为以下几个步骤:

1.1 输入信号的接收:主触发器接收输入信号D。

1.2 信号的传递:主触发器将输入信号D传递给从触发器。

1.3 信号的存储:从触发器接收到信号后,将其存储起来。

1.4 信号的输出:从触发器将存储的信号输出给后续电路。

1.5 信号的同步:主触发器和从触发器之间通过同步机制保证信号的一致性。

- 主从触发器的特点

2.1 防止亚稳态现象:主从触发器通过主从结构的设计,可以有效防止亚稳态现象的发生。亚稳态是指触发器在接收到输入信号后,输出信号在一段时间内不稳定,无法确定其状态。主从触发器通过主触发器和从触发器的同步机制,确保输出信号的稳定性。

2.2 提高电路的稳定性:主从触发器通过主从结构的设计,可以提高电路的稳定性。在主触发器接收到输入信号后,从触发器可以在短时间内完成信号的存储和输出,从而减少信号在电路中的传播延迟,提高电路的稳定性。

2.3 降低功耗:主从触发器在设计时,可以采用低功耗技术,降低电路的功耗。例如,可以采用CMOS工艺设计主从触发器,利用CMOS工艺的低功耗特性,降低电路的功耗。

2.4 提高电路的可靠性:主从触发器通过主从结构的设计,可以提高电路的可靠性。在主触发器接收到输入信号后,从触发器可以在短时间内完成信号的存储和输出,从而减少信号在电路中的传播延迟,提高电路的可靠性。

- 主从触发器的应用

主从触发器在数字电路设计中有广泛的应用,主要包括以下几个方面:

3.1 存储器设计:主从触发器可以用于存储器的设计,例如RAM、ROM等。在存储器设计中,主从触发器可以用于存储数据,提高存储器的稳定性和可靠性。

3.2 寄存器设计:主从触发器可以用于寄存器的设计,例如数据寄存器、地址寄存器等。在寄存器设计中,主从触发器可以用于存储数据,提高寄存器的稳定性和可靠性。

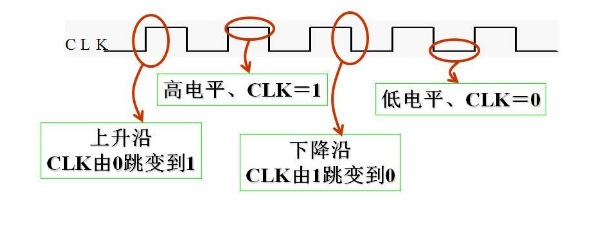

3.3 时钟电路设计:主从触发器可以用于时钟电路的设计,例如分频器、相位锁定环等。在时钟电路设计中,主从触发器可以用于同步信号,提高时钟电路的稳定性和可靠性。

3.4 异步电路设计:主从触发器可以用于异步电路的设计,例如异步计数器、异步寄存器等。在异步电路设计中,主从触发器可以用于同步信号,提高异步电路的稳定性和可靠性。

- 主从触发器的设计

4.1 选择触发器类型:在设计主从触发器时,需要选择合适的触发器类型。常见的触发器类型包括SR触发器、D触发器、JK触发器等。根据电路的需求和性能要求,选择合适的触发器类型。

4.2 设计主触发器:主触发器负责接收输入信号,并将信号传递给从触发器。在设计主触发器时,需要考虑信号的接收、传递和同步机制。

4.3 设计从触发器:从触发器负责存储输出信号,并将其输出给后续电路。在设计从触发器时,需要考虑信号的存储、输出和同步机制。

4.4 设计同步机制:主从触发器的同步机制是保证信号一致性的关键。在设计同步机制时,需要考虑信号的同步方式、同步时间等。

4.5 优化电路性能:在设计主从触发器时,需要考虑电路的性能优化。例如,可以采用低功耗技术、高速设计技术等,提高电路的性能。

-

锁存器

+关注

关注

8文章

906浏览量

41502 -

主从触发器

+关注

关注

0文章

13浏览量

6388 -

数字电路

+关注

关注

193文章

1605浏览量

80605 -

输入信号

+关注

关注

0文章

455浏览量

12554

发布评论请先 登录

相关推荐

主从触发器,主从触发器的原理和特点有哪些?

主从rs触发器波形图介绍

主从触发器是一种能防止什么现象的触发器

主从触发器是一种能防止什么现象的触发器

评论