主从触发器(Master-Slave Flip-Flop)是一种常见的数字逻辑电路,用于存储一位二进制信息。主从触发器通常由两个触发器组成,一个作为主触发器,另一个作为从触发器。主从触发器可以是上升沿触发,也可以是下降沿触发,具体取决于设计和应用需求。

- 主从触发器的原理

主从触发器由两个触发器组成,一个为主触发器,另一个为从触发器。主触发器负责接收输入信号,从触发器负责存储输出信号。当输入信号发生变化时,主触发器会先响应,然后从触发器跟随主触发器的状态变化。

主从触发器的工作原理可以分为以下几个步骤:

1.1 输入信号的接收:主触发器接收输入信号,当输入信号发生变化时,主触发器的状态会发生变化。

1.2 主触发器的状态变化:主触发器的状态变化会通过一定的逻辑关系传递给从触发器。

1.3 从触发器的状态跟随:从触发器接收到主触发器的状态变化信号后,会跟随主触发器的状态变化。

1.4 输出信号的生成:从触发器的状态变化会通过一定的逻辑关系生成输出信号。

- 主从触发器的类型

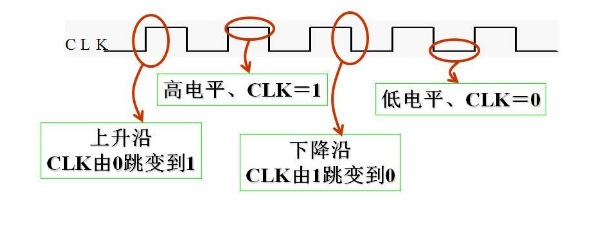

主从触发器按照触发方式的不同,可以分为上升沿触发和下降沿触发两种类型。

2.1 上升沿触发主从触发器:当输入信号从低电平变为高电平时,触发器的状态发生变化。

2.2 下降沿触发主从触发器:当输入信号从高电平变为低电平时,触发器的状态发生变化。

- 主从触发器的特点

主从触发器具有以下特点:

3.1 存储能力强:主从触发器可以存储一位二进制信息,具有较好的存储能力。

3.2 抗干扰能力强:由于主从触发器具有两个触发器,因此在一定程度上可以抵抗外部干扰。

3.3 延迟时间较长:由于主从触发器需要经过两个触发器的状态变化,因此其延迟时间相对较长。

3.4 功耗较大:由于主从触发器包含两个触发器,因此其功耗相对较大。

- 主从触发器的应用

主从触发器广泛应用于数字逻辑电路中,如寄存器、计数器、移位寄存器等。以下是一些常见的应用场景:

4.1 寄存器:寄存器用于存储数据,主从触发器可以作为寄存器的存储单元。

4.2 计数器:计数器用于实现数字计数功能,主从触发器可以作为计数器的存储单元。

4.3 移位寄存器:移位寄存器用于实现数据的移位操作,主从触发器可以作为移位寄存器的存储单元。

4.4 同步电路:同步电路需要同步时钟信号,主从触发器可以用于实现同步功能。

- 主从触发器的设计方法

设计主从触发器需要考虑以下几个方面:

5.1 确定触发方式:根据应用需求,确定主从触发器的触发方式,可以是上升沿触发或下降沿触发。

5.2 选择触发器类型:根据设计要求,选择合适的触发器类型,如D触发器、JK触发器等。

5.3 设计逻辑电路:根据触发方式和触发器类型,设计主从触发器的逻辑电路,包括输入信号的处理、状态传递、输出信号的生成等。

5.4 考虑抗干扰能力:在设计过程中,需要考虑主从触发器的抗干扰能力,可以通过增加冗余设计、采用差分信号等方式提高抗干扰能力。

5.5 优化功耗:在设计过程中,需要考虑主从触发器的功耗问题,可以通过优化电路设计、选择合适的工艺等方式降低功耗。

- 结论

主从触发器是一种常见的数字逻辑电路,具有较好的存储能力和抗干扰能力。根据应用需求,可以选择上升沿触发或下降沿触发的主从触发器。在设计主从触发器时,需要考虑触发方式、触发器类型、逻辑电路设计、抗干扰能力和功耗优化等方面。通过合理的设计,可以提高主从触发器的性能,满足各种应用场景的需求。

-

主从触发器

+关注

关注

0文章

13浏览量

6372 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15800 -

低电平

+关注

关注

1文章

113浏览量

13245 -

输入信号

+关注

关注

0文章

445浏览量

12535

发布评论请先 登录

相关推荐

主从触发器,主从触发器的原理和特点有哪些?

边沿触发器波形图

主从触发器都是下降沿触发吗

主从触发器都是下降沿触发吗

评论