双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的逻辑电路,广泛应用于数字电路设计中。它具有两个基本性质:记忆性和切换性。

一、双稳态触发器的基本概念

1.1 双稳态触发器的定义

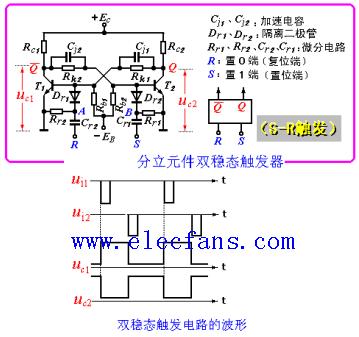

双稳态触发器是一种具有两个稳定状态的逻辑电路,通常由两个交叉耦合的反相器或门电路构成。在没有外部输入信号的情况下,双稳态触发器可以保持在两个稳定状态之一,即“0”状态或“1”状态。

1.2 双稳态触发器的组成

双稳态触发器主要由以下部分组成:

(1)输入端:接收外部输入信号,用于触发双稳态触发器的状态切换。

(2)输出端:输出双稳态触发器的当前状态,可以是“0”或“1”。

(3)存储元件:用于存储双稳态触发器的状态信息,通常由电容、电感或半导体器件构成。

(4)触发电路:根据输入信号控制双稳态触发器的状态切换。

1.3 双稳态触发器的分类

根据触发方式的不同,双稳态触发器可以分为以下几类:

(1)SR触发器(Set-Reset Trigger):通过设置(Set)和复位(Reset)信号来控制状态切换。

(2)JK触发器(Jack-Kilby Trigger):通过同时接收J和K信号来控制状态切换。

(3)D触发器(Data Trigger):通过接收D信号来控制状态切换。

(4)T触发器(Toggle Trigger):通过接收T信号来控制状态切换,每次触发都会使输出状态翻转。

二、双稳态触发器的基本性质

2.1 记忆性

记忆性是双稳态触发器的核心特性之一,它指的是双稳态触发器能够保持其当前状态,直到接收到外部触发信号。具体来说,双稳态触发器的记忆性包括以下几个方面:

(1)稳定性:在没有外部输入信号的情况下,双稳态触发器能够保持其当前状态,不会因为内部噪声或温度变化而发生状态变化。

(2)抗干扰性:双稳态触发器具有较强的抗干扰能力,即使在外部环境变化较大的情况下,也能够保持其状态稳定。

(3)状态保持时间:双稳态触发器能够在接收到触发信号后,保持新状态一定时间,直到下一次触发信号的到来。

2.2 切换性

切换性是双稳态触发器的另一个基本特性,它指的是双稳态触发器能够在接收到外部触发信号后,从当前状态切换到另一个稳定状态。具体来说,双稳态触发器的切换性包括以下几个方面:

(1)触发条件:双稳态触发器需要满足一定的触发条件,才能实现状态切换。例如,SR触发器需要同时满足Set和Reset信号的特定组合才能切换状态。

(2)切换速度:双稳态触发器在接收到触发信号后,能够在较短的时间内完成状态切换,以满足高速数字电路的设计要求。

(3)切换可靠性:双稳态触发器在切换过程中,需要保证状态切换的可靠性,避免因为电路设计不当或外部干扰而导致状态切换失败。

三、双稳态触发器的应用

3.1 存储器设计

双稳态触发器在存储器设计中具有重要应用。例如,静态随机存取存储器(SRAM)就是利用双稳态触发器来存储数据的。每个存储单元由两个交叉耦合的反相器构成,可以存储一位二进制数据。

3.2 计数器设计

双稳态触发器在计数器设计中也发挥着重要作用。通过将多个双稳态触发器级联,可以构成多位计数器,实现对输入信号的计数功能。

3.3 时序控制

双稳态触发器在时序控制中具有广泛应用。例如,在微处理器的指令执行过程中,需要通过双稳态触发器来控制指令的取值、译码和执行等各个阶段的时序。

3.4 信号同步

在数字通信系统中,双稳态触发器可以用于信号同步。通过将接收到的信号与本地时钟信号进行同步,可以消除信号传输过程中的时延和抖动,提高通信系统的稳定性和可靠性。

-

逻辑电路

+关注

关注

13文章

494浏览量

42609 -

反相器

+关注

关注

6文章

311浏览量

43288 -

数字电路

+关注

关注

193文章

1605浏览量

80577

发布评论请先 登录

相关推荐

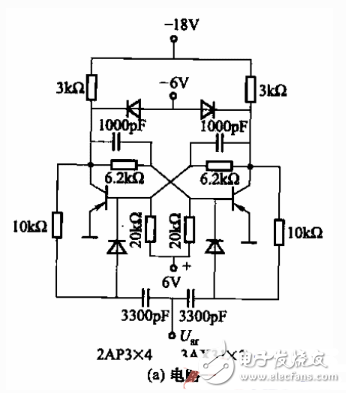

双稳态触发器电路图大全(三极管/CD4017/CD4013双D触发器)

双稳态触发器的两个基本性质是什么

双稳态触发器的两个基本性质是什么

评论