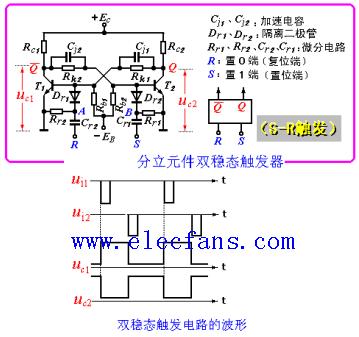

双稳态触发器是一种具有两个稳定状态的数字逻辑电路,它可以在两个状态之间切换,并且能够在没有外部输入信号的情况下保持当前状态。双稳态触发器广泛应用于数字电子系统中,如存储器、计数器、寄存器等。

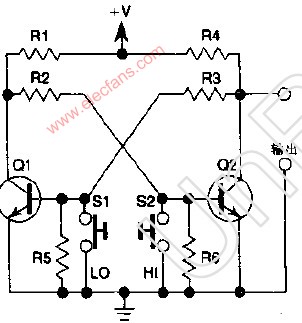

耦合双稳态电路是指两个或多个双稳态触发器通过某种方式连接在一起,以实现特定的功能。耦合方式可以是电耦合、光耦合、磁耦合等,具体取决于应用场景和设计要求。

- 双稳态触发器的基本原理

双稳态触发器是一种具有两个稳定状态的数字逻辑电路。在没有外部输入信号的情况下,双稳态触发器可以保持当前状态不变。当外部输入信号发生变化时,双稳态触发器可以在两个稳定状态之间切换。

双稳态触发器的基本原理是通过正反馈实现的。正反馈是指电路中某个信号的输出会加强该信号的输入,从而使电路达到一个新的稳定状态。在双稳态触发器中,正反馈是通过一个或多个逻辑门实现的。

- 双稳态触发器的分类

根据触发方式的不同,双稳态触发器可以分为以下几种类型:

2.1 基本RS触发器

基本RS触发器是一种最简单的双稳态触发器,由两个与非门(NAND)或两个或非门(NOR)组成。基本RS触发器有两个输入端,分别标记为R(Reset)和S(Set),以及两个输出端,分别为Q和Q'(Q的反相)。

2.2 同步RS触发器

同步RS触发器是一种改进型的基本RS触发器,它在基本RS触发器的基础上增加了一个时钟输入端。同步RS触发器在时钟信号的控制下,可以实现同步切换。

2.3 边沿触发器

边沿触发器是一种特殊的双稳态触发器,它在输入信号的上升沿或下降沿触发切换。边沿触发器通常由D触发器或JK触发器实现。

2.4 主从触发器

主从触发器是一种由两个触发器组成的双稳态触发器,其中一个触发器作为主触发器,另一个触发器作为从触发器。主从触发器可以实现更快的切换速度和更低的功耗。

- 双稳态触发器的设计方法

3.1 设计基本RS触发器

基本RS触发器的设计方法如下:

a) 使用两个与非门(NAND)或两个或非门(NOR)作为基本逻辑门。

b) 将一个逻辑门的输出连接到另一个逻辑门的输入。

c) 将两个逻辑门的输出分别连接到Q和Q'。

3.2 设计同步RS触发器

同步RS触发器的设计方法如下:

a) 在基本RS触发器的基础上增加一个时钟输入端。

b) 使用一个与非门(NAND)或一个或非门(NOR)作为控制门。

c) 将时钟输入端和R、S输入端分别连接到控制门的输入端。

d) 将控制门的输出连接到基本RS触发器的输入端。

3.3 设计边沿触发器

边沿触发器的设计方法如下:

a) 使用D触发器或JK触发器作为基本触发器。

b) 在基本触发器的基础上增加一个时钟输入端。

c) 使用一个与非门(NAND)或一个或非门(NOR)作为控制门。

d) 将时钟输入端的上升沿或下降沿连接到控制门的输入端。

e) 将控制门的输出连接到基本触发器的输入端。

3.4 设计主从触发器

主从触发器的设计方法如下:

a) 选择两个具有相同功能的触发器作为主触发器和从触发器。

b) 将主触发器的输出连接到从触发器的输入端。

c) 使用一个与非门(NAND)或一个或非门(NOR)作为控制门。

d) 将控制门的输出连接到主触发器的输入端。

- 双稳态触发器的应用场景

双稳态触发器广泛应用于数字电子系统中,如存储器、计数器、寄存器等。以下是一些典型的应用场景:

4.1 存储器

双稳态触发器可以用于存储二进制数据。在存储器中,每个存储单元由一个双稳态触发器实现,可以存储0或1。

4.2 计数器

双稳态触发器可以用于实现计数器。计数器是一种数字电路,可以对输入信号进行计数。

-

存储器

+关注

关注

38文章

7484浏览量

163759 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15812 -

输入信号

+关注

关注

0文章

455浏览量

12547

发布评论请先 登录

相关推荐

双稳态触发器是什么耦合双稳态电路

双稳态触发器是什么耦合双稳态电路

评论