人工智能技术日渐普及,广泛运用于解决当今的各种复杂问题,尤其是那些涉及海量数据的分析和相应决策等单靠人力难以应对的棘手难题。换句话说,在应对半导体设计、测试和制造过程中的复杂挑战时,AI堪称理想助手。

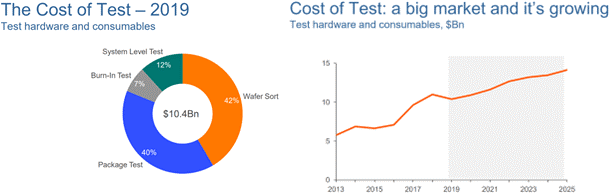

在消费、高性能计算(HPC)和汽车等多个领域,为确保筛选出可靠的器件,需要对所采用的先进节点技术和异构集成展开测试,而这会导致制造测试成本大大飙升。相关测试成本中包含不同阶段的生产测试成本,其中包括晶圆分选测试、封装测试(ATE)、老化测试和系统级测试(SLT)。如图1所示,半导体行业的测试支出高达数十亿美元。2019年的测试总成本为104亿美元,预计到2025年将增至近150亿美元。

制造测试成本与每个阶段花费的测试时间成正比,而其中扫描(ATPG)测试向量等结构测试占用了大部分测试时间。为了进一步降低百万分比缺陷率(DPPM),测试向量的数量和测试向量所占机台内存的大小都呈指数级增长。传统的固定型故障模型 (Stuck at fault model)和跳变延时故障模型(transition delay fault model)已经无法满足期望达到的DPPM目标。为此芯片测试需要更多的测试向量并使用更先进的故障模型(Cell-aware, Power-aware, Slack-based fault mode)来检测更多的制造缺陷。对于大批量制造(HVM)的测试成本来说,省下的每一秒钟都至关重要。同时,可测性设计/诊断/良率团队以及产品和测试开发团队正不断寻找创新型方案来进一步降低测试成本。

▲图1VLSI Research对测试成本的预测。(资料来源:VLSI PP Master (swtest.org))

如何以更少的测试向量实现所需的测试覆盖率和测试质量,这是DFT团队持续面临的挑战,通常不仅需要专家级用户参与,还离不开漫长而繁琐的迭代过程,以微调不同参数,生成更优ATPG向量集。此外,为进一步优化测试向量数量并减少测试总量,还需要优化测试构架配置,也就是调整扫描输入、扫描输出、扫描链的数量。为每个设计核心找到合适的测试配置是一项耗时费力且充满挑战的任务。

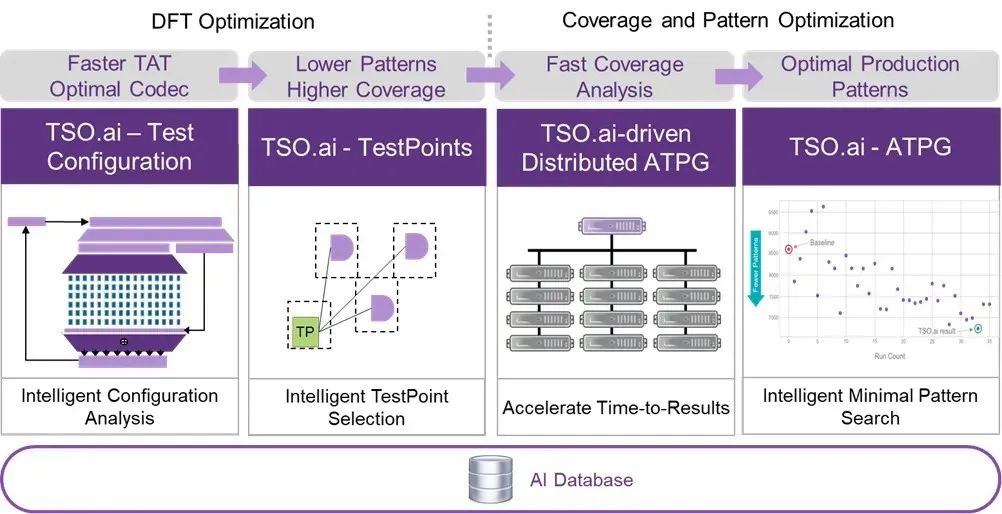

▲图2 新思科技TSO.ai利用AI/ML实现先进的DFT和ATPG。

新思科技TSO.ai是一款AI驱动型测试空间优化解决方案,它利用了AI来优化门级网表上的ATPG向量生成,从而减少生产测试向量,进而降低测试成本。得益于此,在很多客户的设计中,测试向量平均减少了25%。最近,新思科技增强了这个功能,让开发者能够通过集成新思科技TestMAX分布式ATPG功能,将测试运行分配到多台机器和线程并加以管理,从而加速生成测试向量。然而,由于ATPG功能针对的是门级网表,其中的DFT测试构架配置在RTL阶段已经确定,因此只能通过在DFT规划阶段优化测试构架配置来进一步减少向量数量。

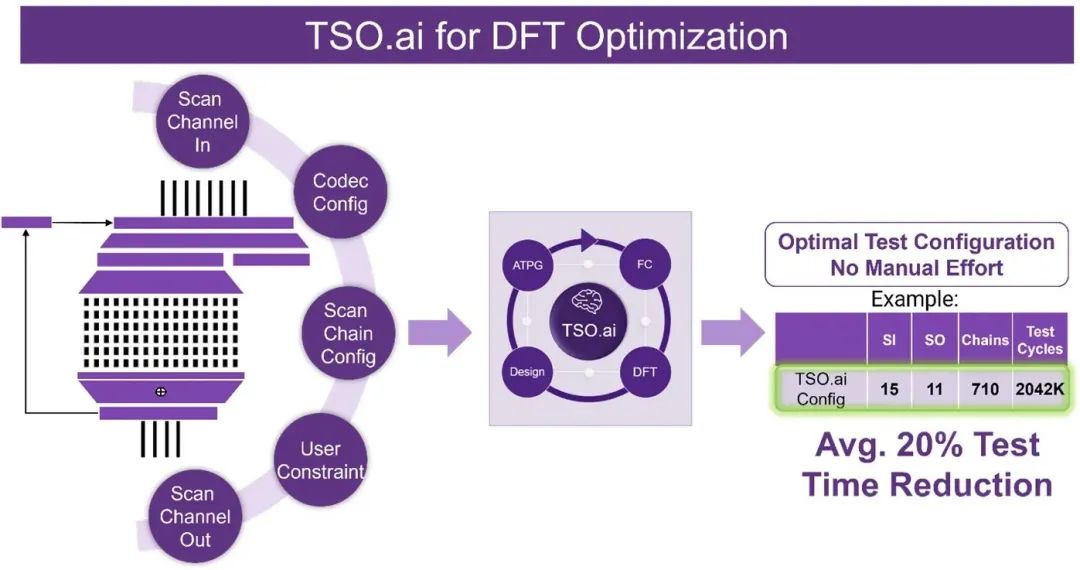

▲图3 新思科技TSO.ai用于DFT规划和优化。

目前,新思科技TSO.ai在早期DFT规划阶段提供了增强功能,能够优化涵盖扫描链数量、扫描输入、扫描输出在内的多个不同参数的测试配置。用户可以在RTL阶段早期快速进行假设分析,以满足其测试覆盖率和测试时间目标,并为综合运行生成更优测试配置,从而在单次综合流程中实现门级网表。在传统流程中,用户必须等待综合后的门级网表,才能评估所选测试配置的覆盖率;然后,为了优化测试配置,用户必须重复扫描拼接和综合流程,以评估其对测试覆盖率和测试向量的影响。这是一个非常漫长的迭代过程。此外,一套测试构架配置不能适用所有设计模块,因为优化方案与模块的功能设计息息相关。而对所有设计模块重复进行试验又非常耗费人力,可能会导致设计进度延误数周乃至数月。

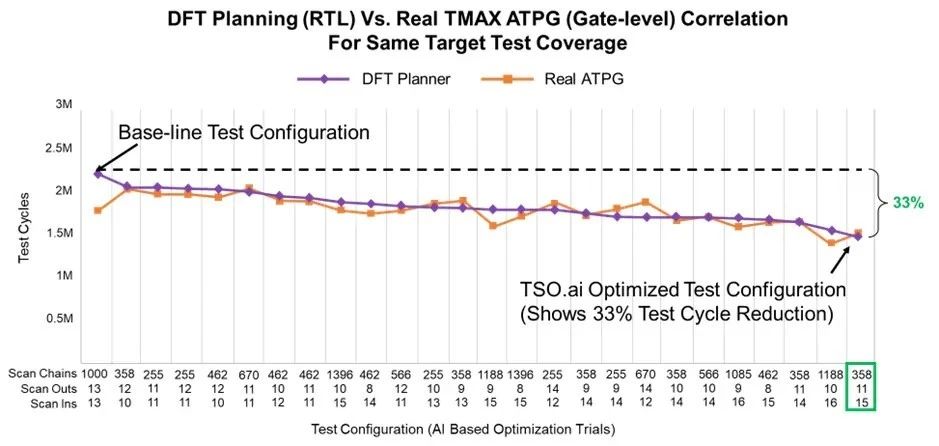

▲图4 TSO.ai基准结果 – DFT规划算法和门级ATPG之间的相关性。

图4着重强调了Tso.ai在一个基准设计上的评估结果,与根据传统经验规划的基准测试构架配置相比,基于Tso.ai规划的DFT构架可以减少33%的测试向量数量。在相同的测试构架配置和测试覆盖率下,新思科技TSO.ai在RTL阶段评估的ATPG测试向量数量,与综合后门级网表上实际运行的新思科技TestMAX ATPG测试数量有很好的一致性。

新思科技TSO.ai的DFT构架规划功能平均可以减少20%的测试向量;若辅以其ATPG参数优化的功能,则平均可以再减少25%测试向量。由此可见,新思科技TSO.ai可以显著缩短测试时间,进而降低测试成本。此外,新思科技TSO.ai的DFT功能可以在RTL阶段优化测试配置,助开发者达到测试覆盖率和测试向量数量目标,因此用户无需进行多次涉及门级综合的长周期迭代,进而能将设计周期从数月大幅缩短为几天。

新思科技始终致力于将AI/ML应用于半导体设计。Synopsys.ai是一个全栈式AI驱动型EDA整体解决方案,可用于优化数字和模拟器件的设计、验证、测试与制造过程。新思科技TSO.ai是Synopsys.ai解决方案的关键组成部分,能够提供更优测试配置和测试向量,帮助开发者应对日益紧迫的设计进度和不断增长的测试成本挑战。新思科技在测试领域的AI应用仍在不断探索和创新,公司计划继续开发关键解决方案,以应对未来测试的挑战。

-

芯片测试

+关注

关注

6文章

138浏览量

20346 -

AI

+关注

关注

87文章

32867浏览量

272332 -

人工智能

+关注

关注

1801文章

48207浏览量

242918 -

新思科技

+关注

关注

5文章

833浏览量

50654

原文标题:AI如何助力芯片测试突破成本和时间的双重挑战?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

加快MIMO测试速度和降低测试成本的方法

什么是测试成本?(如测试测量 设备、自动元器件处理设备等)

新思科技发布业界首款全栈式AI驱动型EDA解决方案Synopsys.ai

利用测试排序仪器降低测试成本

助力AI算法芯片化 新思科技推出ASIP Designer

是德科技推出光测试解决方案,助力收发信机制造商缩短测试时间、降低测试成本

TSO.ai芯片测试空间优化方案:打通AI应用“最后一公里”

本周五|TSO.ai:打通AI应用“最后一公里”,降低芯片测试成本

新思科技TSO.ai助力解决芯片测试成本和时间挑战

新思科技TSO.ai助力解决芯片测试成本和时间挑战

评论