RS触发器是一种常见的数字逻辑门电路元件,其逻辑功能可以描述为存储器元件或双稳态开关。它由两个相互反馈的逻辑门组成,通常是非门或与非门的组合,具有两个输入端(R和S)和两个输出端(Q和Q')。这里的R和S分别代表“Reset”(复位)和“Set”(置位),它们共同控制触发器的输出状态。以下是对RS触发器逻辑功能的详细描述:

一、基本逻辑功能

RS触发器的逻辑功能主要体现在其对输入信号R和S的响应上,根据R和S的不同组合,触发器可以处于四种不同的状态:

- 保持状态(Hold State)

- 当R=0且S=0时,触发器保持其当前状态不变。即,如果Q之前为1,则保持为1;如果Q之前为0,则保持为0。这种状态下,无论输入如何变化,只要R和S同时保持为0,触发器的输出就不会改变。

- 复位状态(Reset State)

- 当R=0且S=1时,触发器被置为复位状态。此时,输出Q被强制为逻辑低电平(0),而Q'被强制为逻辑高电平(1)。这种状态下,触发器将忽略之前的输出状态,直接根据R和S的当前值来设置输出。

- 置位状态(Set State)

- 当R=1且S=0时,触发器被置为置位状态。此时,输出Q被强制为逻辑高电平(1),而Q'被强制为逻辑低电平(0)。与复位状态类似,置位状态也会忽略触发器的先前状态,直接根据R和S的当前值来设置输出。

- 禁止状态(Forbidden State)

- 当R=1且S=1时,触发器进入禁止状态。在这种状态下,触发器的行为是不确定的,因为R和S的同时激活违反了触发器的设计原则。理想情况下,应避免这种情况的发生,因为它可能导致不可预测的结果。然而,在某些情况下,通过添加额外的逻辑电路或使用改进型触发器(如D触发器或JK触发器),可以处理这种禁止状态。

二、输入输出关系

RS触发器的输入输出关系可以通过真值表或状态转换图来清晰地表示。以下是一个典型的RS触发器真值表:

| R | S | Q(next) | Q'(next) |

|---|---|---|---|

| 0 | 0 | Q(prev) | Q'(prev) |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 禁止 | 禁止 |

从真值表中可以看出,除了禁止状态外,触发器的输出Q和Q'完全由输入R和S决定。当R和S都为0时,触发器保持其先前状态;当R为0且S为1时,触发器被复位;当R为1且S为0时,触发器被置位。

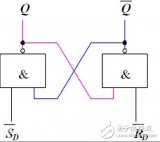

三、工作原理

RS触发器的工作原理基于正反馈机制。当两个逻辑门(如与非门)交叉连接时,它们会形成一个正反馈回路。这种回路使得触发器能够保持其当前状态不变,直到接收到新的触发信号。具体来说,当触发器处于某一稳定状态时(如Q=1),如果R和S保持不变(即R=0且S=0),那么触发器的输出将维持在该状态上。如果R变为0且S变为1,则触发器的输出将被强制置为复位状态(Q=0);反之,如果R变为1且S变为0,则触发器的输出将被强制置为置位状态(Q=1)。

四、应用场景

RS触发器由于其双稳态特性和简单的逻辑功能,在数字电路设计中有着广泛的应用。以下是一些典型的应用场景:

- 计数器 :RS触发器可以级联成计数器电路,用于实现数字系统的时钟节拍、频率分频等功能。通过级联多个RS触发器,可以构建出能够计数到更高数值的计数器。

- 状态机 :在数字系统中,状态机是一种用于处理序列逻辑和控制电路的电路。RS触发器可以用作状态机的存储单元,用于存储和转换系统的当前状态。

- 寄存器 :寄存器是一种存储器件,用于保存一组位的二进制数据。RS触发器可以组合成寄存器电路,用于在数字系统中存储和操作数据。

- 帧同步电路 :在串行数据传输中,帧同步是非常重要的。RS触发器可以用于构建帧同步电路,通过检测特定的数据模式来同步传输的数据。

- 脉冲生成器 :RS触发器还可以用于构建脉冲生成器,特别是在需要精确控制脉冲宽度和频率的场合。通过巧妙地设置R和S输入,并利用触发器的翻转和保持特性,可以生成具有特定时间间隔和持续时间的脉冲信号。这种脉冲信号在数字信号处理、定时控制以及波形发生器等应用中非常有用。

五、触发器类型与实现

RS触发器根据实现方式的不同,可以分为基本RS触发器、同步RS触发器(也称为钟控RS触发器)和主从RS触发器等多种类型。

- 基本RS触发器 :

基本RS触发器通常由两个与非门或两个或非门交叉反馈连接而成。它直接根据R和S的输入电平来决定输出Q和Q'的状态。然而,由于存在竞争冒险和不定态的问题(即当R和S同时为1时),基本RS触发器在实际应用中较少直接使用。 - 同步RS触发器 :

同步RS触发器在基本RS触发器的基础上增加了一个时钟信号(CLK)来控制触发器的翻转。只有当时钟信号处于有效状态(如高电平或上升沿)时,R和S的输入才会被触发器接收并产生相应的输出变化。这种方式有效地避免了不定态的问题,并使得触发器的操作更加可靠和可控。 - 主从RS触发器 :

主从RS触发器由两个基本RS触发器构成,其中一个作为主触发器,另一个作为从触发器。在时钟信号的控制下,主触发器首先根据R和S的输入状态进行翻转,并将结果传递给从触发器。然后,在从触发器中,这些结果会被再次锁存,以确保在时钟信号的下一个周期到来之前,触发器的输出状态保持不变。主从RS触发器结合了同步触发和锁存功能,提高了触发器的性能和稳定性。

六、触发器的性能考虑

在设计和使用RS触发器时,需要考虑以下性能因素:

- 传播延迟 :触发器从接收到输入信号到产生稳定输出信号所需的时间称为传播延迟。这个延迟时间对于高速数字系统设计来说至关重要,因为它会影响系统的整体响应速度和性能。

- 功耗 :触发器的功耗包括静态功耗和动态功耗两部分。静态功耗是触发器在保持状态时消耗的功率,而动态功耗则是触发器在翻转过程中消耗的功率。为了降低功耗,需要优化触发器的电路设计和制造工艺。

- 稳定性 :触发器的稳定性是指其在不同工作环境和条件下保持正确工作状态的能力。为了提高稳定性,需要确保触发器电路具有足够的噪声容限和抗干扰能力。

- 可靠性 :触发器的可靠性是指其在长期使用过程中保持正常工作状态的能力。为了提高可靠性,需要采用高质量的元器件和合理的电路设计,并进行充分的测试和验证。

七、结论

RS触发器作为数字电路中的基本元件之一,具有双稳态特性和简单的逻辑功能。它能够在特定的输入条件下改变并保持其输出状态,从而实现数据的存储和转换。通过合理设计和使用RS触发器,可以构建出各种复杂的数字系统,并满足各种实际应用需求。然而,在设计和使用RS触发器时,需要充分考虑其性能因素,以确保系统的稳定性和可靠性。随着集成电路技术的不断发展,新型触发器的出现和应用将进一步推动数字电路技术的进步和发展。

-

逻辑门

+关注

关注

1文章

142浏览量

24060 -

RS触发器

+关注

关注

3文章

101浏览量

17947 -

触发器

+关注

关注

14文章

2000浏览量

61165

发布评论请先 登录

相关推荐

RS触发器工作原理_RS触发器逻辑功能_RS触发器和SR触发器的区别

RS触发器的基本逻辑功能

RS触发器的基本逻辑功能

评论