1. 时钟资源概述

时钟设施提供了一系列的低电容、低抖动的互联线,这些互联线非常适合于传输高频信号、最大量减小时钟抖动。这些连线资源可以和DCM、PLL等实现连接。

每一种Spartan-6芯片提供16个高速、低抖动的全局时钟资源用于优化性能;这些资源可以背Xilinx工具自动地使用,即使时钟频率相对较低,使用时钟资源来消除潜在的时序冒险仍然是十分重要的,每一个Spartan-6 FPGA提供40个超高速、低抖动的IO局部时钟资源(32个BUFIO2S和8个BUFPLL)这些IO局部时钟资源是为IO Serializer和de-serializer电路服务的。

Spartan-6 FPGA的时钟资源主要由四种类型的连接器构成:

全局时钟输入引脚(GCLK)

全局时钟多路复用器(BUFG、BUFGMUX)

IO时钟缓冲器(BUFIO2、BUFIO2_2CLK、BUFPLL)

水平方向时钟布线缓冲器(BUFH)

有两种类型的时钟网络:

为FPGA内部逻辑资源提供低抖动时钟资源的全局时钟网络

为SelectIIO逻辑资源提供高性能低抖动时钟资源的IO局部时钟网络

BUFGMUX能够在两个全局时钟资源之间进行复用,也可以当做普通的BUFG时钟缓冲使用,这个时钟缓冲只能够直接驱动全局时钟布线资源,只能够驱动时钟输入;当然,FPGA内部逻辑触发器的时钟输入也可以来自那些普通的布线资源,不过那些普通的布线资源会具有较大的时钟抖动。

BUFPLL和BUFIO2用来驱动IO局部时钟网络的时钟资源,这一特性限定了它们的使用目的,他们只能用于ISERDES或OSERDES这资源的输入时钟资源;

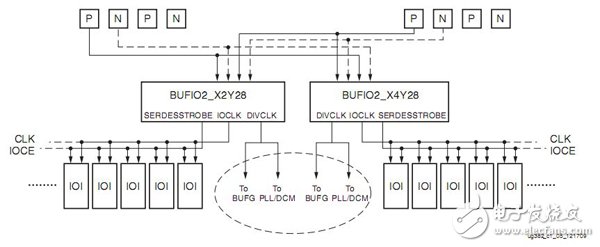

BUFIO2能够驱动SDR和DDR的ISERDES2和OSERDES2的时钟,BUFIO2能够把GCLK或GTP_DUAL Tile的输入时钟布线到BUFG、DCM、PLL时钟输入。BUFIO2_2CLK能够用来代替BUFIO2s使用在DDR的ISERDES2和OSERDES2的设计时钟。

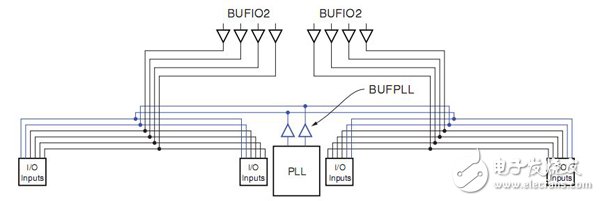

类似地,BUFPLL可以驱动SDR时钟的IO时钟网络,BUFPLL将PLL的CLKOUT0或CLKOUT1和IO局部时钟网络连接起来。

BUFH通过提供逻辑资源与全局时钟布线水平区域的连接,使得芯片总体的低抖动时钟资源更为丰富。

1.1. 全局时钟结构

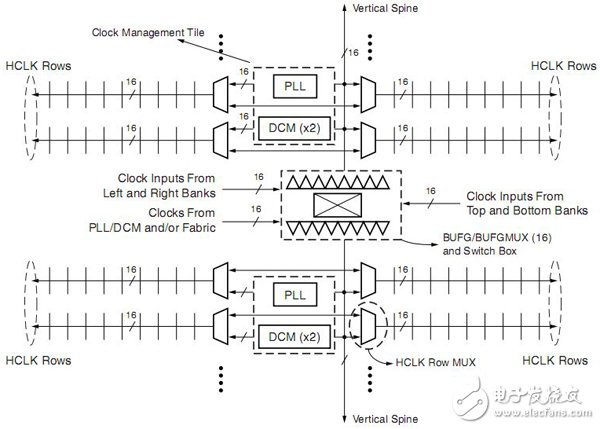

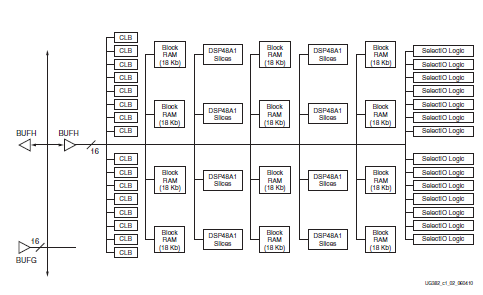

图 1.1全局时钟结构

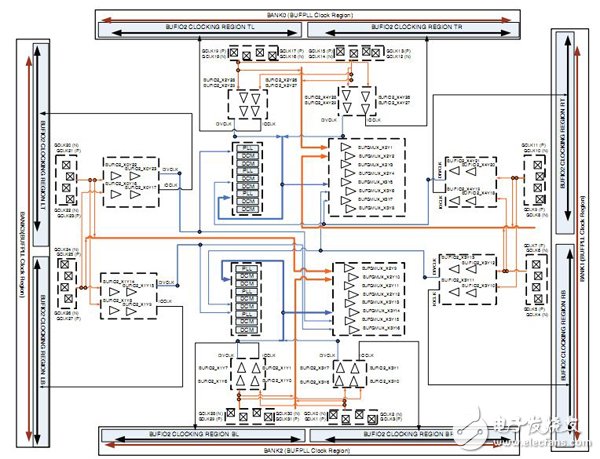

Spartan-6 FPGA的全局时钟网络由16个位于器件中心位置的BUFGMUX驱动,时钟的输入可以来自FPGA的上、下、左、右的bank,也可以来自PLL或DCM;16个BUFGMUX驱动vertical spine并经vertical spine 往南北方向传播,根据这条线路,时钟水平延伸至HCLK时钟列并经HCLK时钟列提供了访问局部逻辑原语的路径;每一个HCLK列左右两边各有16个水平时钟缓冲BUFH驱动左右逻辑资源。

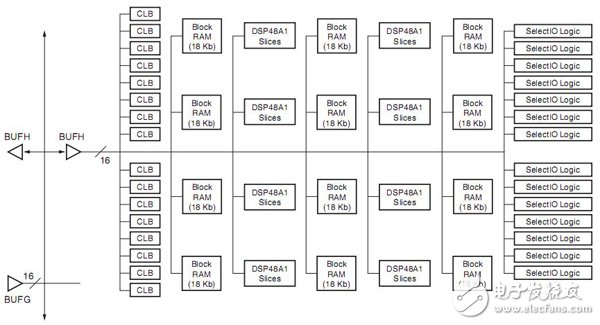

图 1.2BUFH时钟布线路径

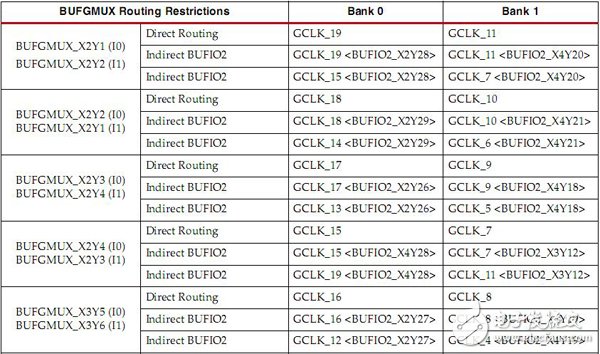

在Spartan-6 FPGA器件上,有32个GCLK输入,但是只有16个全局时钟缓冲,也就是说每一个全局时钟缓冲只能被2个GCLK中的一个驱动,在两个GCLK(假设为GCLK_A和GCLK_B共享BUFGMX_C)都需要使用的情况下,为了为用户提供更多的灵活性,可以让GCLK_A引脚布线到BUFGMUX_C,而GCLK_B使用BUFIO2间接地布线到另一个BUFGMUX_D。但是经过BUFIO2布线的时钟会出现延时。

表格 1.1 Bank0和Bank1共享全局时钟资源不完全统计情况表

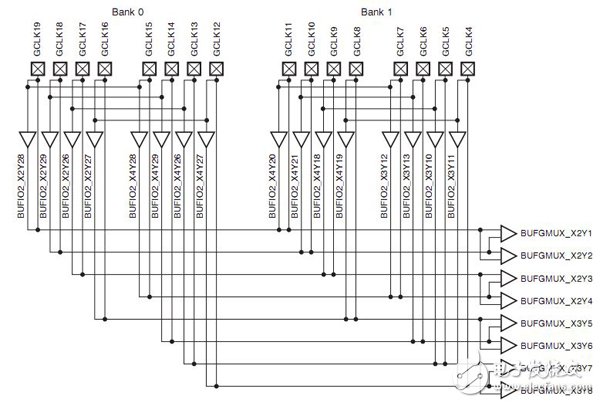

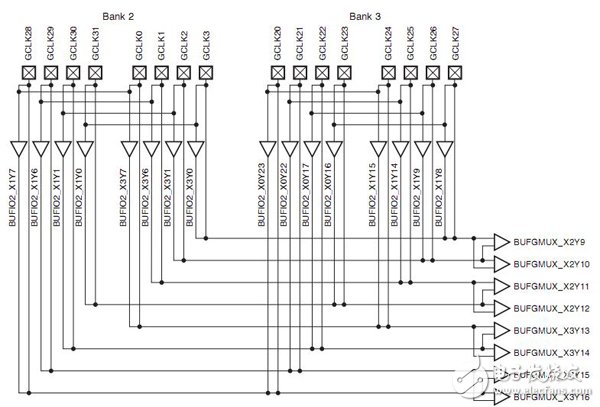

图 1.3Bank0和Bank1的BUFGMUX的连接情况

图 1.4Bank2和Bank3的BUFGMUX的连接情况

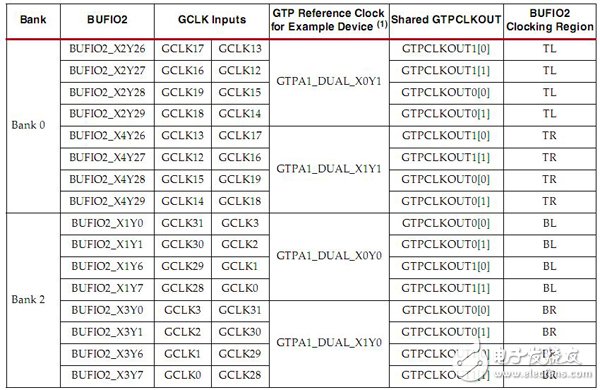

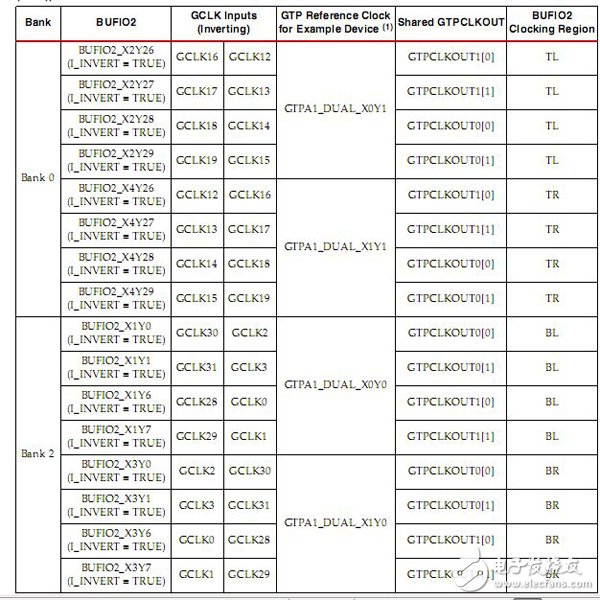

对于使用GTP Transceiver的设计来说,每一个GTP参考时钟是和一个BUFIO2关联在一起的,这可能影响Bank0和Bank2上的全局时钟引脚的使用;对SDR接口来说,GCLK的引脚输入与的冲突如表格 1.2所示,对DDR接口来说,GTP需要两个BUFIO2,因为DDR的需要将时钟反转,DDR接口对GCLK引脚输入的冲突如表格 1.3所示。

表格 1.2SDR接口使用中BUFIO2的输入冲突

表格 1.3DDR接口使用中BUFIO2的输入冲突

1.2. IO时钟结构

1.5IO时钟结构

所有的SelectIOn的逻辑资源(输入寄存器、输出寄存器、IDDR2、ODDR2、ISERDES2、OSERDES2)必须被来自BUFIO2的时钟驱动;每个BUFIO2时钟域有4个高速I时钟,由4个专用BUFIO2 缓冲驱动;Spartan6 FPGA有4个BUFIO2时钟域共32BUFIO2.

1.6BUFIO2时钟域

2. 时钟输入

时钟输入引脚接受外部时钟信号并且直接将其连接至BUFGMUX或者BUFIO2原语。当然,时钟引脚也可以用作普通IO。BUFIO2除了能将时钟输入到IO时钟网络,BUFIO2也提供了专用的接往PLL/DCM或BUFG的时钟路线

2.1经BUFIO2布线的专用时钟输入

对Spartan-6 FPGA而言,专用的时钟输入引脚位于芯片边沿的中心位置,下图例举了4Bank的Spartan-6 FPGA的时钟引脚布局。

2.2四Bank Spartan-6 FPGA 时钟引脚布局

3. 时钟管理技术

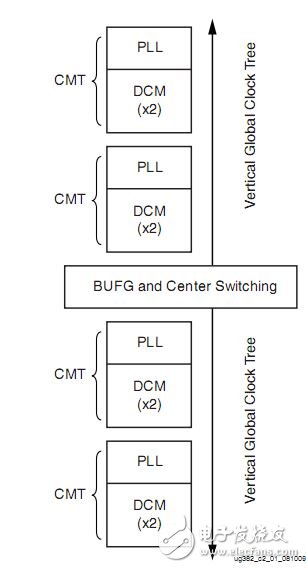

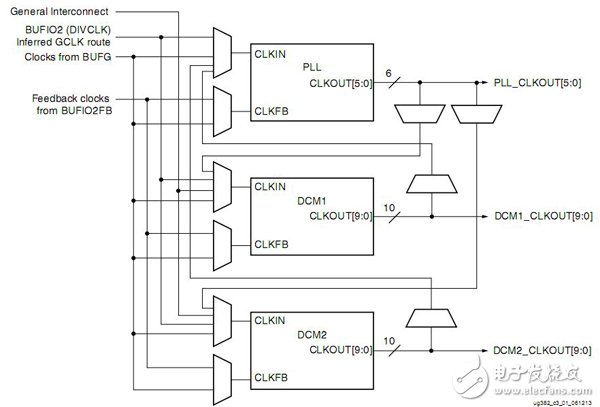

Spartan-6 FPGA的CMT(时钟管理单元)提供了非常灵活、高性能的时钟;Spartan-6 FPGA的CMT模块位于竖直的全局时钟树的中间列位置,每个CMT包含2个DCM、1个PLL。

3.1Spartan-6 FPGA CMT位置图

3.2CMT结构框图

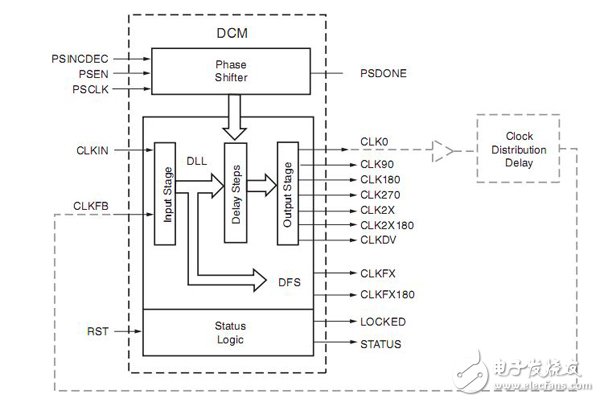

3.1. DCM的功能

DCM:Digital Clock Management,数字时钟管理单元的英文缩写。DCM拥有先进的时钟能力可将时钟直接导入全局时钟分布网络,DCM可以解决各种各样的时钟问题,尤其是在高性能、高频率领域。

消除了时钟抖动,提升了整个系统的性能

调节一个时钟信号的相位

对输入时钟进行倍频或分频,也能够通过动态或静态的提供乘除因子产生新的时钟频率。

使时钟信号更健康,占空比稳定在50%

镜像、转发、重缓冲一个时钟信号,对输入时钟信号进行去抖斜或转换成差分IO电平。

时钟输入抖动过滤

扩频时钟产生

振荡器工作模式

3.3DCM结构框图

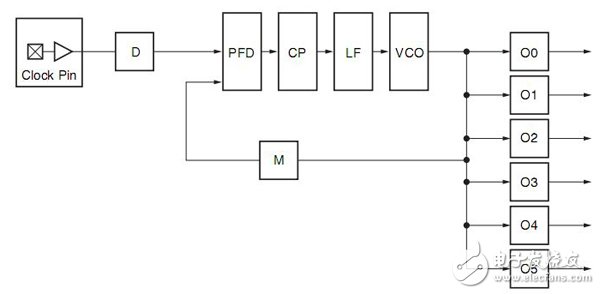

3.2. PLL的功能

PLL:Phase-Locked Loop,锁相环的英文缩写。Spartan-6 FPGA器件包含6个CMT Tile。PLL的主要目的是作为外部时钟或内部时钟的抖动过滤器或频率合成器。

3.4PLL结构框图

-

FPGA

+关注

关注

1629文章

21735浏览量

603154 -

Spartan-6

+关注

关注

4文章

38浏览量

17536

发布评论请先 登录

相关推荐

Spartan-6 FPGA工业影像目标设计平台(Xilin

基于Spartan-6的FPGA SP601开发设计方案

一文详解Spartan-6系列IO Tile结构

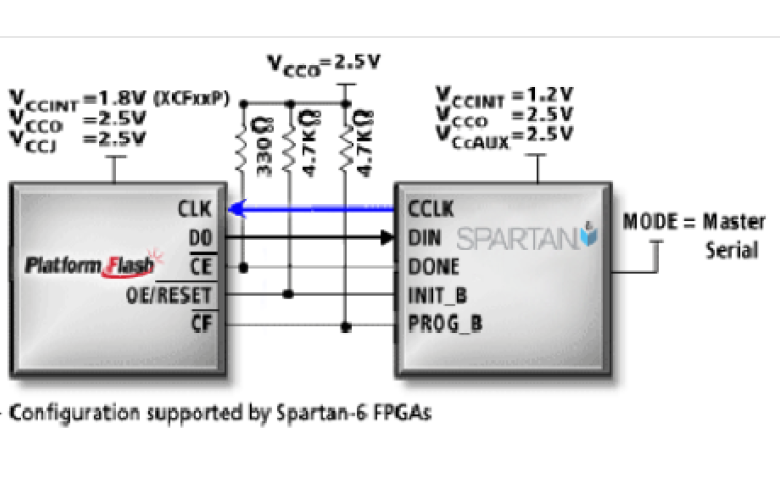

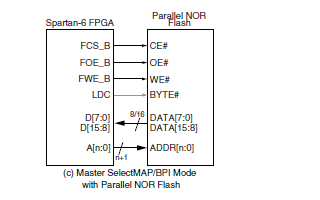

Spartan-6 FPGA Configuration User Guide

Spartan-6 FPGA视频平台的演示介绍

ISE 14.7 for Spartan-6 FPGA的使用

Spartan-6 FPGA中的DCM功能介绍

spartan-6 FPGA可配置逻辑块的用户指南资料免费下载

Spartan-6 FPGA的配置教程说明

Spartan-6 FPGA的时钟资源及结构介绍

Spartan-6 FPGA的时钟资源及结构介绍

评论