Electro-Static discharge

ESD(Electro-Static discharge)意为静止电荷放电。静止电荷简称静电,作为一种客观自然的现象,表现为电子的过多或不足。当静电荷积聚在某一物体上时,该物体的分子会处于电失衡状态。在两个平面之间或者一个平面与地之间,带有多余电子的表面呈现负电性,而电子缺失的表面则呈现正电性。静电放电则是这些电荷在不同静电势的物体或表面之间转移的过程。

静电的特点在于其高电压、低电量、小电流以及作用时间短。尽管对人体可能只造成轻微冲击,但对于微电子元件而言却是致命的。在IC行业中,ESD是主要的可靠性威胁之一,是导致约三分之一IC失效的原因。

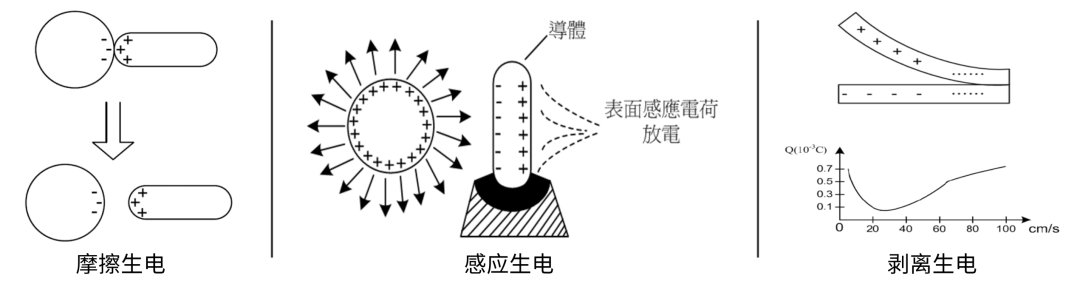

静电产生的常见原因包括接触、剥离、摩擦和感应,其中摩擦生电是最典型且常见的现象。静电可能来源于人体,也可能来自仪器设备或电子元器件本身。根据静电源头的不同,ESD测试可分为人体模型(HBM)、机器模型(MM)和充电器件模型(CDM)。其中,人体是最重要的静电来源,因此HBM模拟测试在ESD防护设计中尤为重要。

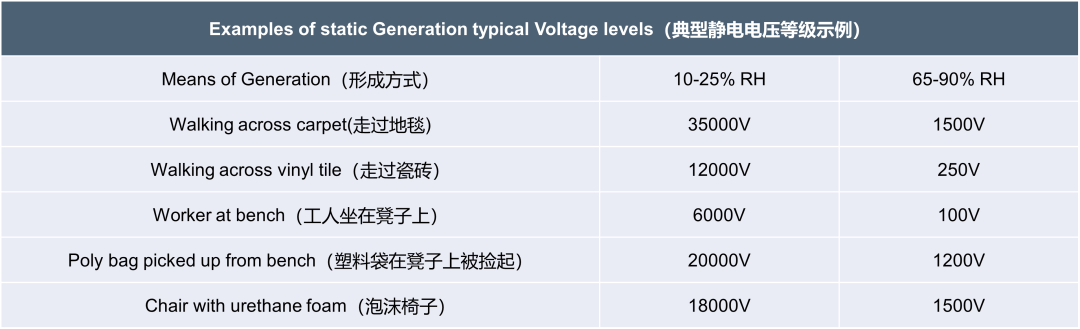

不同情形下的静电电压等级示例

HBM模型的提出

人体模型(Human Body Model,简称HBM)是ESD防护研究中建立最早且最主要的模型之一。当人体因摩擦等原因积聚静电荷后,若与集成电路的某些引脚接触,同时集成电路的另一部分引脚接触到地面,人体上的静电荷便会通过集成电路流入大地。

人体能够储存一定量的电荷,因此具有明显的电容特性。同时,人体也具备一定的电阻,这取决于人体的肌肉弹性、水分含量以及接触电阻等因素。大部分研究人员认为电容器串联一个电阻是较为合理的电气模型。

早在1962年,美国国家矿务局进行了大量实验,测得人体电容范围在95~398PF之间,平均电容值为240PF。同时,手与手之间的平均电阻测得为4000Ω。这些数据为建立人体模型提供了宝贵的依据,经过一些修正后,被用于电子工业中早期的模拟电路设计。

后续研究中,Kirk等人进一步测得人体电容值的范围为132-190PF,而人体电阻值则在87-190Ω之间。为了统一标准,美国海军在1980年提出了一个被广泛接受的人体模型参数,即电容值为100PF,电阻为1.5kΩ的“标准人体模型”。这一模型为后续的ESD防护研究和测试提供了重要的参考依据。

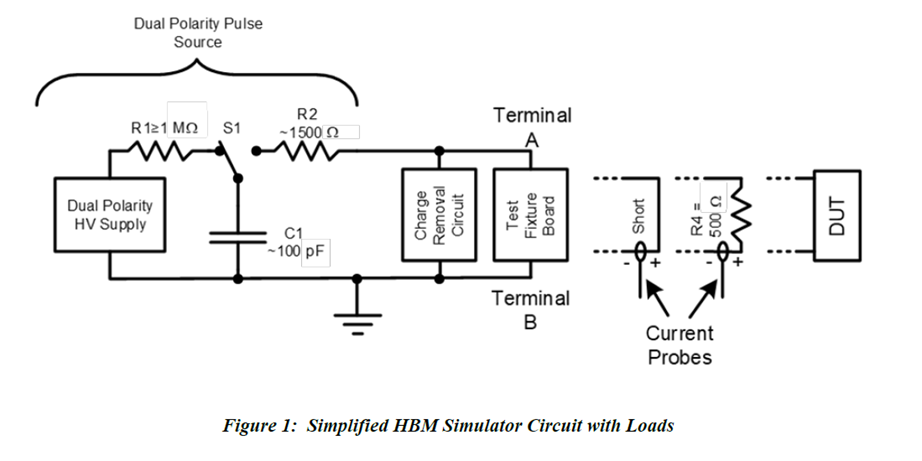

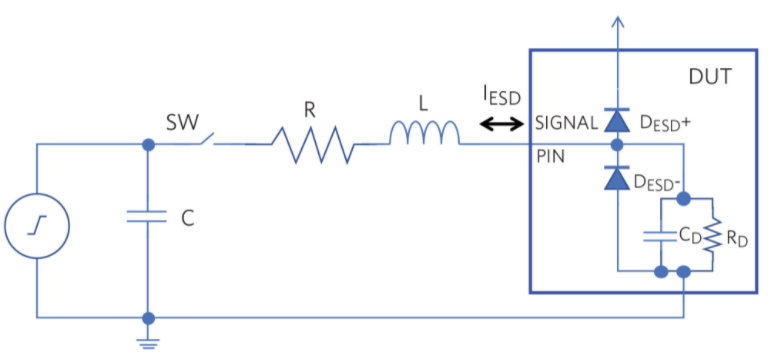

HBM模拟测试的等效电路原理图

以下是HBM标准中描述的HBM模拟器的等效电路图。在这个等效电路图中,Terminal A作为静电测试端,负责模拟人体带有的静电荷,并与待测设备进行接触。而Terminal B则作为接地端,用于模拟集成电路的另一部分引脚与地面接触的情况。

此外,等效电路图中还包括了短路负载(Short)和500欧姆电阻器(R4)。这两个元件是根据JS 001标准规定的,用于评估设备放电波形所要求的负载。

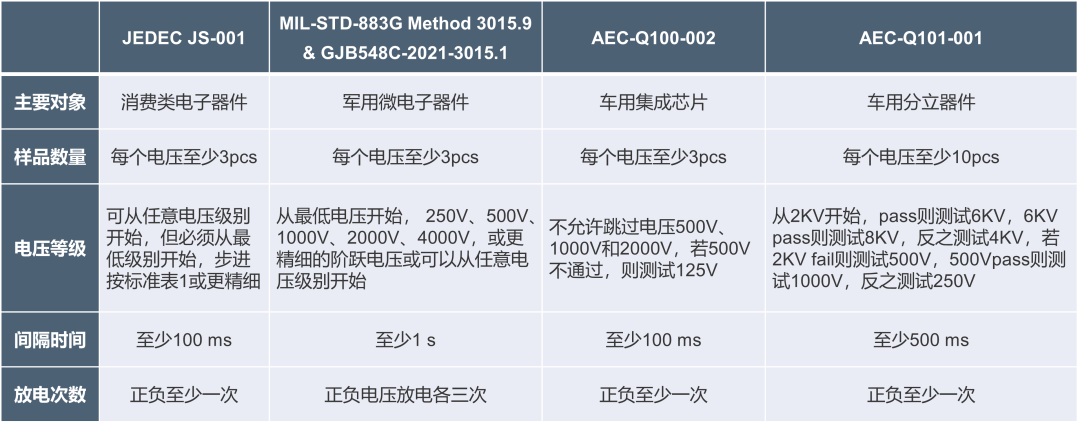

常用的测试标准及其对应的测试条件

HBM测试的静电放电组合

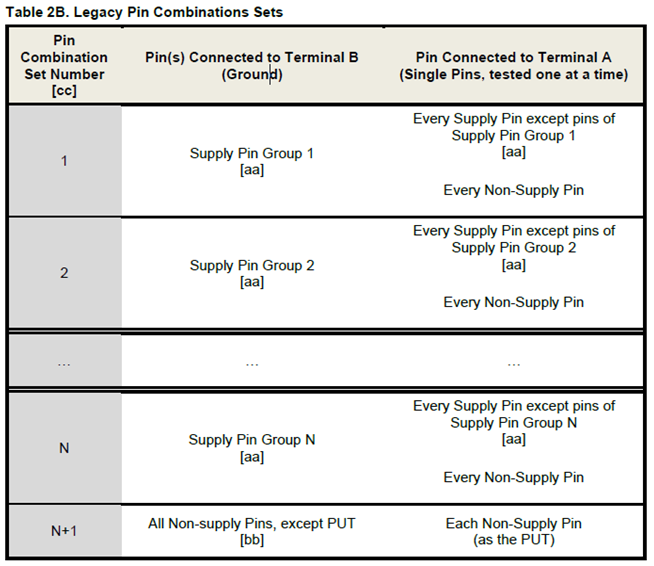

测试放电组合可以选择标准内的table 2A或table 2B中的任意组合,但实践中更常选择table 2B的组合方案进行测试。如下图是table 2B的测试方案,即测试No.1: supply pin Group 1~No.N: supply pin Group N和No.N+1: non-supply pin group组合。

其中需要注意以下事项:首先,如果两个电源引脚是通过die内金属互连,或通过封装打线短接,那么这两个引脚则可以划分为同一个电源引脚组别,但必须严格确认这两个引脚之间的电阻值是否小于或等于3欧姆,如果测量结果显示电阻值大于3欧姆,那么这两个引脚应当作为独立的电源引脚分别进行测试,以防止ESD保护较为薄弱的点被忽视。

其次,对于非电源引脚组别来说,如果在这一组别内的引脚之间存在封装打线短接或die内金属互连,并且这些连接的阻值小于1欧姆,那么在实际测试时,可以选择其中的一个引脚作为代表进行测试。而与之相连的其他引脚则无需参与测试,但在整个测试过程中需要保持浮接状态(JS 001)。

测试结果的判定

实验室通常以IV曲线的偏移作为判定测试是否pass或fail的标准。具体来说,SGS选择以±15%的偏移量作为参考范围,且标准中明确规定,在ESD测试前后都需要对引脚的功能进行确认。因此,在进行ESD测试前,建议客户首先量测引脚的功能以确保其处于正常状态,完成ESD测试后,再次量测引脚的功能。

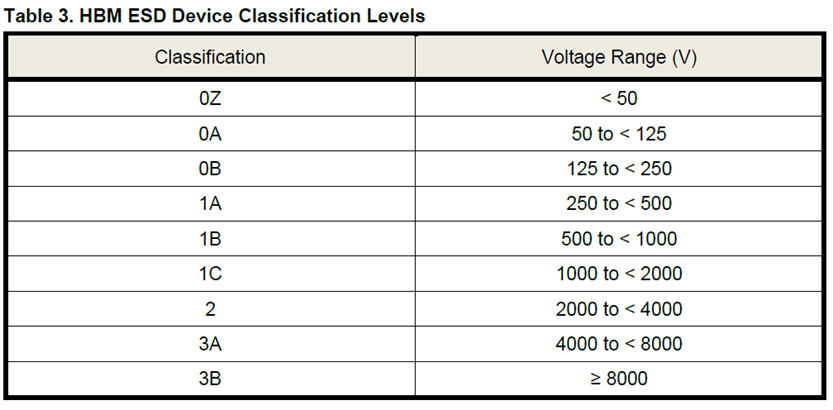

由于每个器件的引脚在ESD能力上存在差异,标准要求在进行ESD测试时,必须依据器件中结果最差的引脚来确定整个器件所能通过的电压水平,测试结果还需按照以下等级分类表格进行分级(JS 001):

影响测试结果判定的几种效应

1静电累积效应

新型的机台MK2和MK4基本都配备了测试后释放静电(discharge pins after zap)的选项,并且在每次测量IV曲线时也能起到释放静电的作用,但这些措施并不能完全保证将socket或测试板上的所有静电完全释放。如果待测器件对静电累积的影响较为敏感,那么静电的累积可能会对其性能造成显著影响。为了应对这一问题,相关标准允许对于每个不同的电压或引脚组合,使用全新的样本组进行测试。这样的做法旨在消除由于阶跃电压累积效应可能带来的不良影响,从而降低因静电累积应力导致的早期失效风险。

2故障窗口效应

Failure Window

故障窗口效应指的是器件在高电压和低电压水平下都能顺利通过测试,但在某个中间电压范围内却会出现失效的情况。例如,如果一个器件在500V和2000V的ESD测试中都表现正常,但在1000V的测试中却失效了,那么这个器件的故障窗口范围大致在500V至2000V之间,并且该器件的ESD水平应被认定为500V。针对这种故障窗口效应,我们建议客户在进行ESD测试时选择合适的电压阶跃水平,以避免部分失效情况被忽略。

3阶跃应力硬化效应

step-stress-test hardening

阶跃应力硬化效应指的是:从低电压水平开始,逐步增加电压水平并使用相同的样品组进行测试时,最终的测试结果可能会高于实际芯片的耐受水平。

以步进电压测试为例,虽然器件在测试中通过了2500V的电压,但如果每个电压水平都使用全新的样品组进行测试,那么器件可能只能承受2000V的电压。这说明,在没有阶跃应力硬化效应的影响下,器件的真实ESD能力可能远低于之前测试的结果。因此,应以每个电压水平使用新的样品组的测试结果为准。在上述例子中,器件被认定只能承受2000V的电压水平。

-

集成电路

+关注

关注

5400文章

11690浏览量

364531 -

ESD

+关注

关注

49文章

2139浏览量

173814 -

半导体

+关注

关注

335文章

27970浏览量

225146 -

人体静电

+关注

关注

0文章

6浏览量

1776

原文标题:技术干货 | 集成电路如何应对人体静电冲击?HBM测试告诉你!

文章出处:【微信号:SGS半导体服务,微信公众号:SGS半导体服务】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HBM模拟测试在ESD防护设计中的应用方案

HBM模拟测试在ESD防护设计中的应用方案

评论