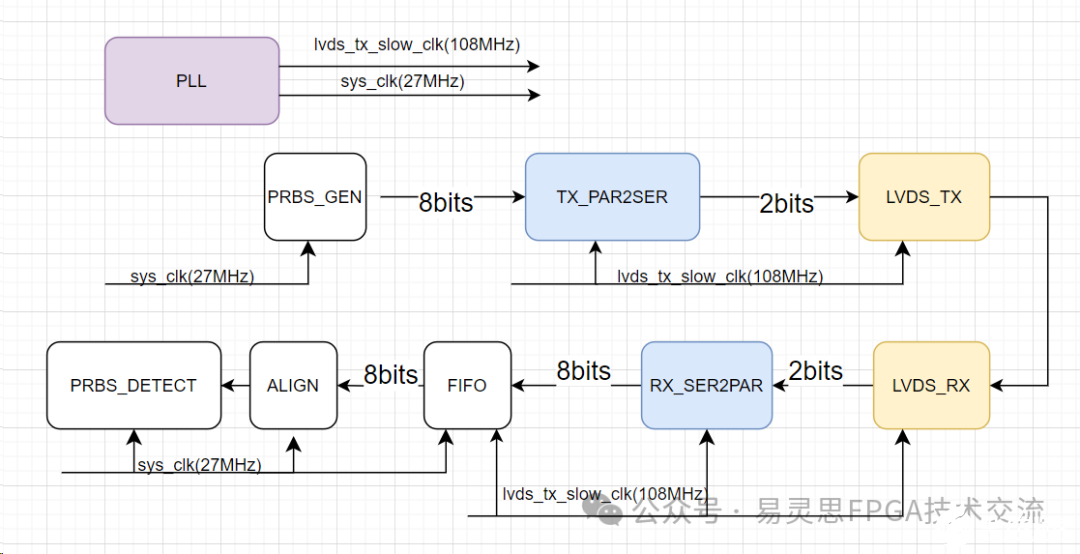

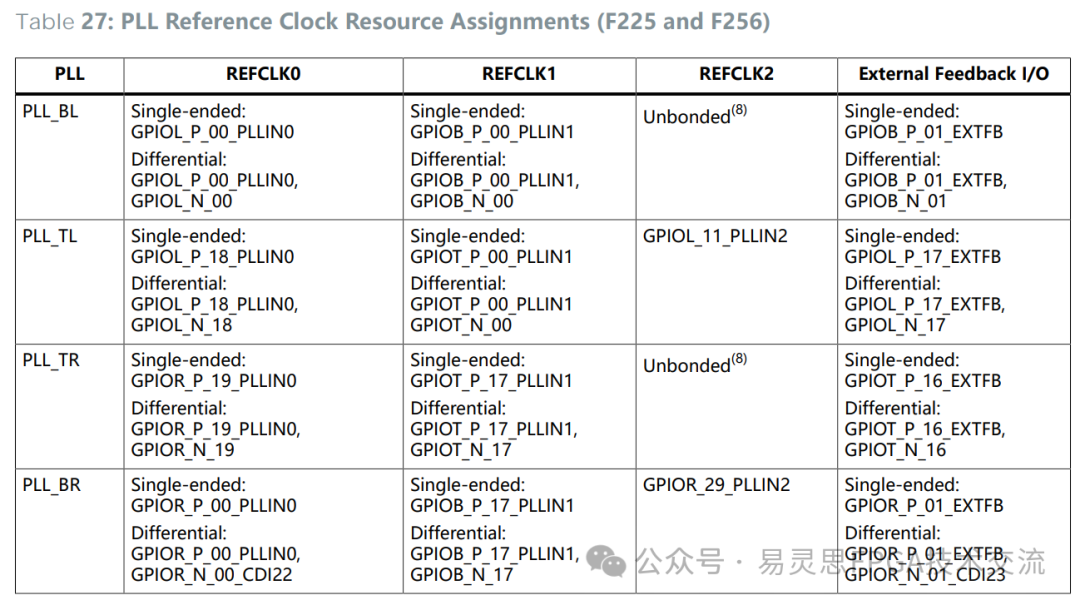

在易灵思的器件上接收LVDS一般采用PLL接收,通过PLL产生两个时钟,一个是fast_clk,一个是slow_clk,分别用于处理串行数据和并行数据。

但是如果LVDS的速率比较低时,另外想通过去掉PLL来节省功耗时,也可以直接用lvds_rx_clk直接走GCLK的方式来处理。下面我们来说明一下:

硬件环境如下:

打开interface在里面设置LVDS

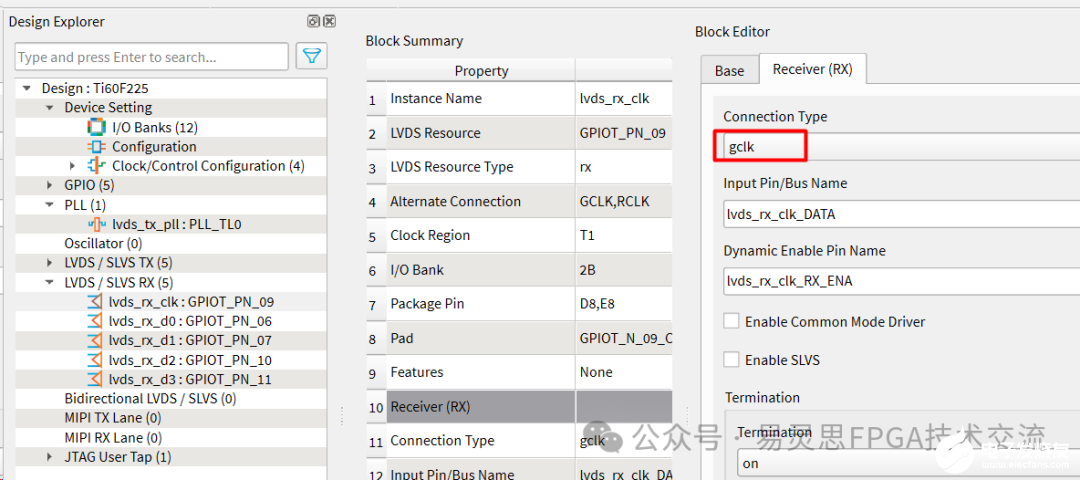

LVDS的时钟接收Connection Type选择gclk。

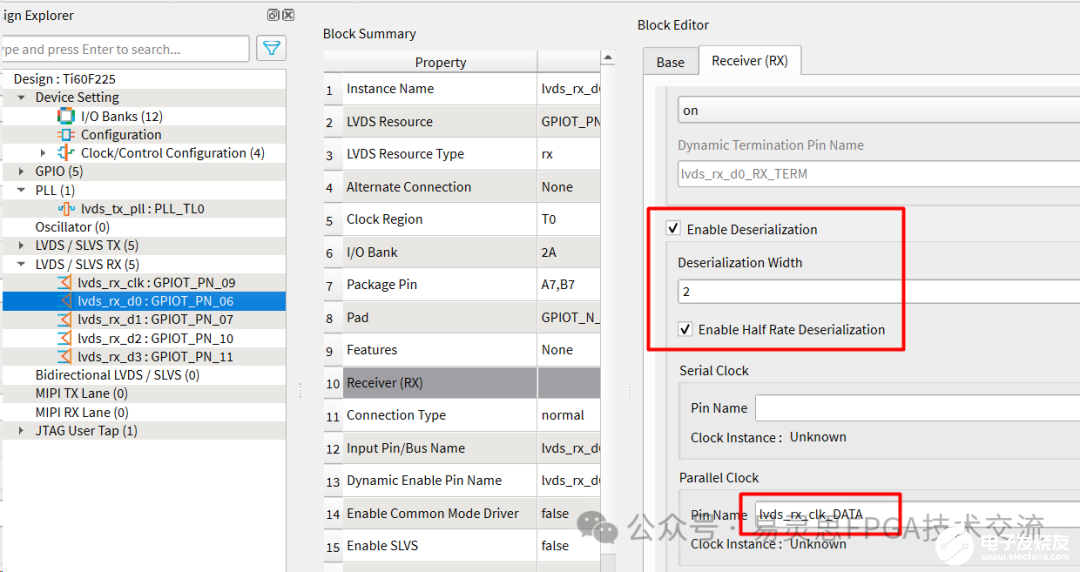

对于数据设置串化因子为2,并输入Parallel Clock名字为上面定义的时钟。

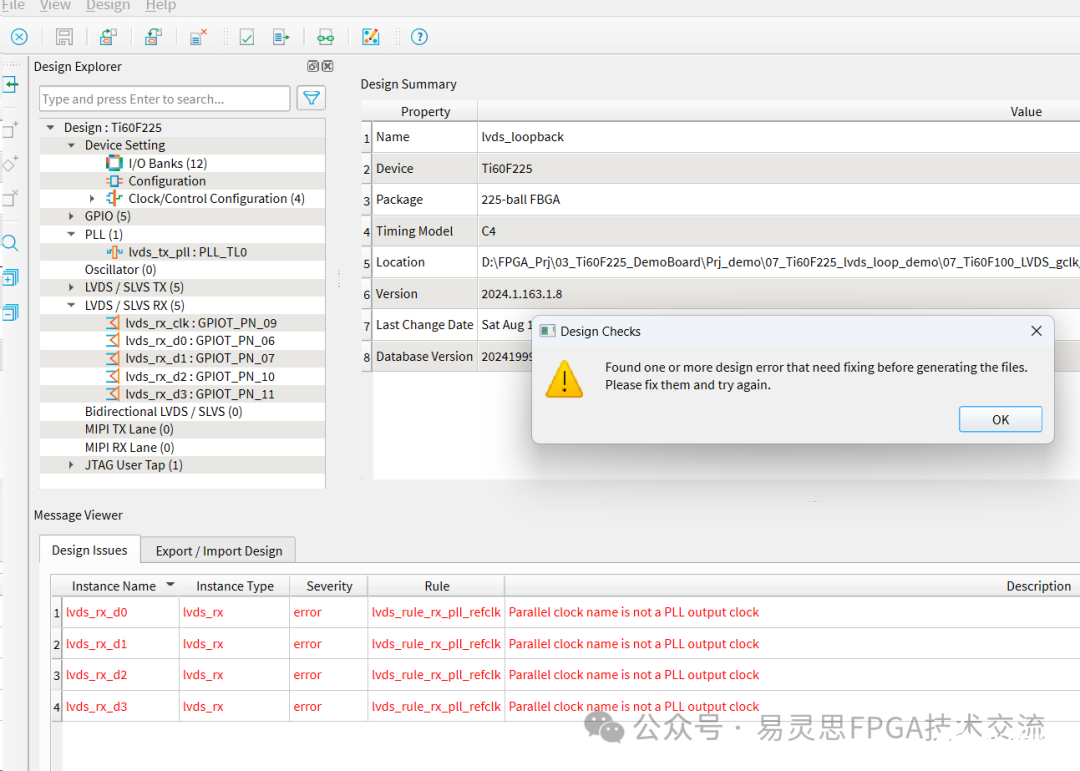

在一切都设置好之后需要生成约束。但是会报以下错误。

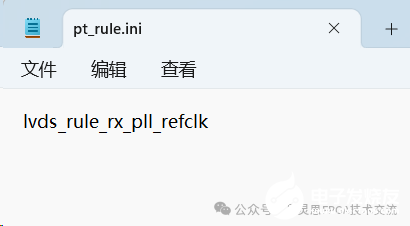

但是解决办法是有的。在工程目录下新建pt_rule.ini文件,输入lvds_rule_rx_pll_refclk,再次生成结束可以正常。

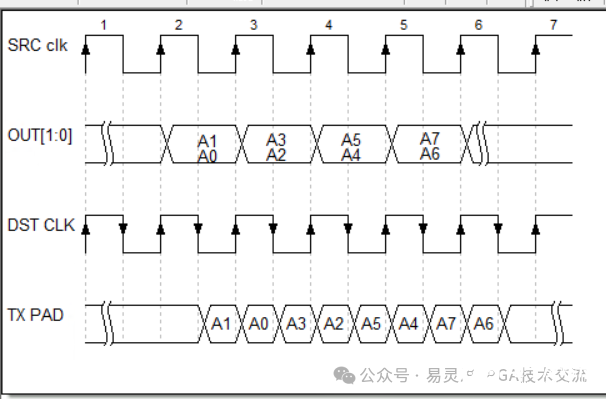

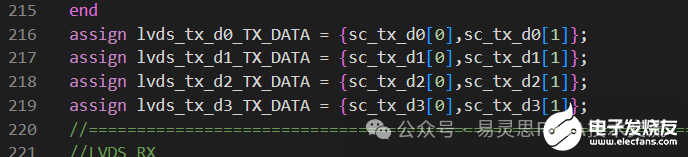

另外注意在发送过程中发送的数据存在高低位需要顺序取反的问题。

程序框图如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21813浏览量

606908 -

lvds

+关注

关注

2文章

1050浏览量

66126 -

易灵思

+关注

关注

5文章

48浏览量

4965

发布评论请先 登录

相关推荐

Freescale V1 ColdFire处理器

Freescale V1 ColdFire处理器,在Cyclone III FPGA上通过FPGA结构来实现V1 ColdFire内核,拓展了ColdFire在新领域的应用优势

发表于 11-30 16:39

•1703次阅读

请问有办法将LVDS时钟信号应用于GCLK时钟输入吗?

嗨,是否有可能以某种方式将LVDS时钟信号应用于GCLK时钟输入?以上来自于谷歌翻译以下为原文Hi, is it possible to apply LVDS clock signals to the

发表于 06-25 07:17

Arm Neoverse V1 PMU指南

本文档描述了不同性能监视器单元(PMU)事件的行为在Neoverse V1。

Neoverse V1有六个可编程的32位计数器(计数器0-5),每个计数器计数器可以编程为在本文档中描述的PMU

发表于 08-09 07:30

基于串口通讯的打包数据的接收方案

串口通讯是上微机与下微机通讯过程中一个较为常见的问题。本文提出了一个串口通讯中打包数据的接收方案,并用VB 语言对此方案进行了实现。经过实际测试,该方案不仅能满

发表于 09-17 10:47

•51次下载

HAPS通信中基于MIMO的信号协作接收方案性能分析

分析了在HAPS中应用协作通信的需求,研究了HAPS通信信道在不同仰角区域的特性,在此基础上提出一种HAPS通信中基于MIMO的信号协作接收方案,并在不同仰角区域中对该协作接收方案进行

发表于 01-10 16:45

•18次下载

LVDS的GCLK接收方案-v1

LVDS的GCLK接收方案-v1

评论