获得高频输出的方法(第一部:锁相环电路)

锁相环电路概略与爱普生产品阵容

【序文】

近年,伴随影像传输等普及,骨干网中流过的通信量有增无减,通信的高速、大容量化进展迅速。在这种情况下,高速化通信基础设施对高频且输出信号稳定的基准信号源的需求十分强烈。

通常,从 MHz 频带的 AT 型石英晶体获得高频振荡时需要将石英片加工得很薄(理由是 AT 型石英晶体的频率因其厚度而定),这造成在加工方法、机械性强度和容易起振等方面存在局限。虽然将受加工精度的影响,但石英晶体以基波起振高频时的上限一般为 60MHz 左右。因此,本公司把 60MHz 以上定为高频领域。稳定输出高频基准信号并不简单,爱普生拥有四种方法(技术)实现高频领域:第一种方法是使用有较易处理的 20MHz 频带起振频率的AT 型石英晶体单元,利用倍频电路或锁相环(PLL)电路输出稳定的高频基准信号;第二种方法是使用表面声波SAW 谐振器输出高频基准信号,表面声波 SAW 谐振器利用弹性表面声波(SAW/Surface Acoustic Wave)以基波直接起振高频;第三种方法是应用爱普生所持有的 QMEMS 技术,制造出仅将振动部分加工变薄的反向台型 AT 型石英晶体单元,以此产生稳定的高频基准信号;第四种方法是使用 AT 型石英晶体单元的高频振动的振动模式(谐波)输出稳定的高频基准信号。本次就第一种方法、即倍频电路(这里所称的倍频电路是指抽出高次谐波的模拟倍频)和锁相环电路的概略进行解说。

【1】输出 n 倍高频的倍频电路

倍频电路是指把某一频率的电气信号转换为 n 倍高频的电路。一般的振荡电路输出信号具有一定的 Tr、Tf、Voh和 Vol 时,其波形中将包含高谐波成份。倍频电路利用这些高谐波产生有意加强了 n 次成份的信号,并用滤波器抽出 n 次成份。由于使用高谐波,因此可以获得抖动小于锁相环电路的输出频率。然而,若欲只抽出 n 次高谐波,则要求在选择石英晶体单元和设计起振电路时加以注意。例如需要使用频带窄、高衰减的带通滤波器(BPF),把n/2 次以下的分谐波衰减掉,以便抑制抖动;还要使输入信号在 n 次高谐波附近不带噪音(失真)等。因此,为了得到高频,产品中大多使用锁相环电路。在下一章中,我们将说明锁相环电路。

【2】锁相环电路

这里说明产生稳定高频的另一项技术――锁相环电路。

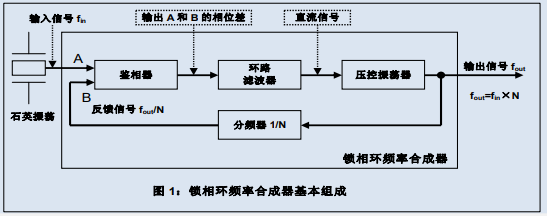

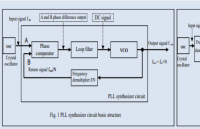

伴随搭载无线通信仪器的设备的普及,用于无线通信的半导体集成电路技术有了飞跃性的进展。其中,锁相环电路技术的进步尤为突出。锁相环电路产生与输入的基准信号相同步的输出信号。该电路的基本组成是鉴相器、环路滤波器和压控振荡器(VCO)。它将正确地产生与输入信号相同步的信号。与倍频电路不同的是,锁相环电路不直接使用输入信号制作输出信号。在锁相环电路中,由压控振荡器(VCO)产生与输入信号相同频率的同步信号。

在锁相环电路的压控振荡器输出和鉴相器的输入之间连接分频器,通过使输入信号与分频后的信号相同步,从而将压控振荡器的输出频率控制在分频倍数的频率。使用石英晶体振荡器等能够产生稳定频率,并转换分频器的分频数,就能使压控振荡器的输出达到石英晶体振荡器同等精度且等于分频倍数频率的信号。这就是频率合成器的原理。

应用该原理,把 AT 型石英晶体单元输出的 MHz 频带频率输入到锁相环频率合成器,就能够产生用于无线通信的 GHz 频带载波信号。

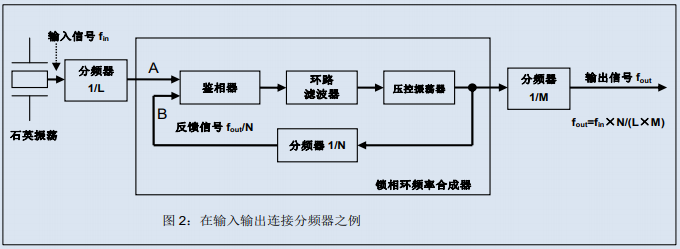

使用锁相环频率合成器获得大于输入频率几倍的频率时,分频器的使用方法是关键。获得输入频率的 N 倍输出的电路结构如图 1 所示。为了对输出频率进行精密设定,还可以如图 2 所示,在锁相环频率合成器的输入前及输出后设置分频电路。

为了提高锁相环频率合成器的频率设定分辨率,通常把分频器直接连接在石英晶体振荡单元之后。但是,若为了提高频率设定分辨率而取较大的分频数,则将造成用于比较相位的频率变小,引发锁相环响应慢、环路增益下降的情况,并对输出波形的抖动和相位噪音特性造成不良影响。为解决上述问题,也可使用小数分频锁相环。

【3】整数分频锁相环与小数分频锁相环的特征

锁相环电路可分为整数分频和小数分频的两大类。双方均利用波源输出高频,在此说明大特征。

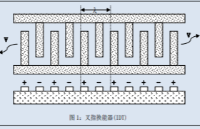

整数分频锁相环可以名副其实地产生输入频率整数倍的输出频率。例如,希望从 1MHz 的波源获得 100MHz 的输出时,分频器的计数器设定值为 100。

与此相对,小数分频锁相环可以产生输入频率小数倍的输出频率。这事实上意味着可以任意选择频率,即能够获得微小的频率设定分辨率。它可以获得微小的频率分辨率,发挥这个特征可以对初始频率公差进行精密控制。

然而,与上述优点相反,小数分频的电路设计复杂,集成电路面积也比整数分频大,因此容易产生特有的失真,致使小数分频的相位噪音与整数分频相比较差。随着近几年技术的发展,小数分频锁相环的缺点被不断改进,失真逐渐减少。

【4】爱普生的产品阵容与特征

以上说明了为获得高频输出而采用的锁相环电路。锁相环电路的最大特征是能够获得任意的频率,即可以获得包括高频在内的所需频率。

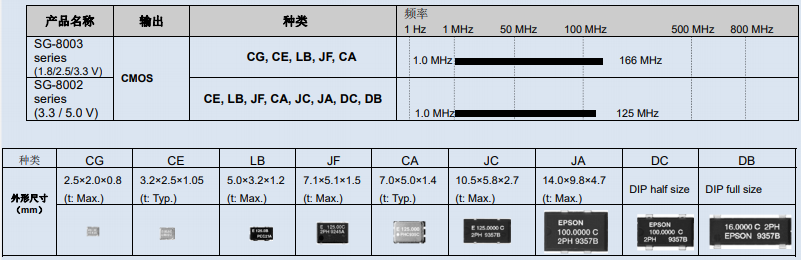

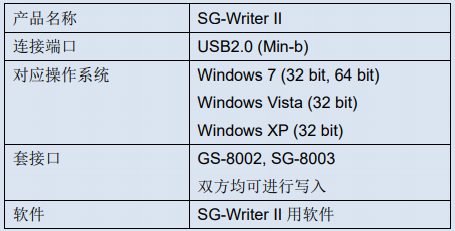

爱普生 SG-8000 系列采用先前介绍的整数分频锁相环电路,为用户准备了尺寸及形状极为丰富的产品阵容(表 1)。我们还为用户准备了 SG-8000 系列的编程工具――ROM Writer(SG-Writer II),用于写入频率(表 2)。

SG-8000系列使用AT型石英晶体单元。AT型石英晶体单元具有呈三次曲线的温度特性,能够保持一定的温度稳定度。因此,SG-8000系列在常温条件下不需要温度补偿电路就能够实现针对温度变化而相对稳定的温度特性,即不出现频率间断性跳动的情况。温度特性呈线形的全硅MEMS等振荡器需要使用温度补偿电路使温度保持稳定,导致有可能出现频率的间断性跳动。

这些石英晶体所具有的高精度特性以及通过锁相环电路技术而实现的可获得任意频率的方便性,希望能够得到多方惠顾。

最后说明上述获得高频输出的倍频和锁相环电路的注意之处。

倍频电路:应注意分谐波混入电路以及因 n/2 以下成份而引起的抖动。

锁相环电路:应注意环路频带,在锁相环电路之后串联其它锁相环电路时应注意抖动增幅和跟踪。

表 1:程控石英晶体振荡器的产品阵容

表 2:SG-8000 系列用编程工具

-

pll

+关注

关注

6文章

992浏览量

138476 -

锁相环电路

+关注

关注

0文章

15浏览量

12313 -

高频输出

+关注

关注

0文章

6浏览量

1054

发布评论请先 登录

PLL设计的简易方法介绍

请问我能从PLL,DCM或级联PLL DCM获得多大的输出频率限制?

使用pll的时钟输出的正确方法是什么?

怎么使用PLL来获得更高的电平?

可以用MMCM替换PLL,然后获得适合驱动这个ISERDES代码的差分时钟输出吗?

PLL知识

Mouser备货Analog Devices公司最高频率PLL

锁相环PLL的设计方法和调试说明

获得高频输出的方法PLL技术

获得高频输出的方法PLL技术

评论