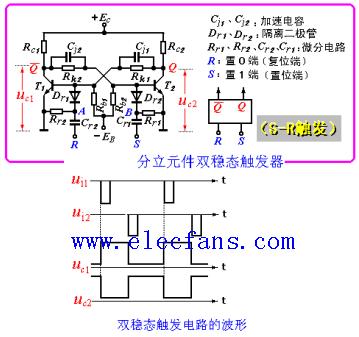

双稳态触发器(Bistable Trigger)是一种具有两个稳定状态的数字电路,常用于存储一位二进制信息。它在数字电路设计中具有重要应用,如存储器、计数器、寄存器等。

一、双稳态触发器的类型

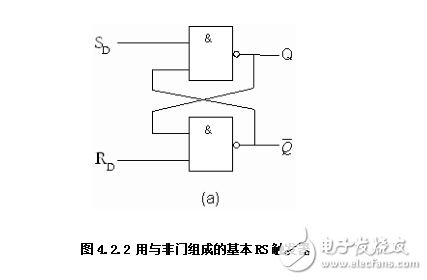

基本RS触发器是一种最简单的双稳态触发器,由两个交叉耦合的反相器组成。它有两个输入端:置位(Set)端和复位(Reset)端。当置位端为高电平时,触发器输出为高电平;当复位端为高电平时,触发器输出为低电平。基本RS触发器存在竞争冒险问题,因此需要改进。

- 钟控RS触发器(Clocked RS Flip-Flop)

钟控RS触发器在基本RS触发器的基础上增加了一个时钟输入端,通过时钟信号控制触发器的状态转换。当置位端和复位端同时为高电平时,触发器保持当前状态不变。钟控RS触发器可以有效避免竞争冒险问题。

- D触发器(D Flip-Flop)

D触发器是一种具有数据输入端的双稳态触发器,其输出与数据输入端相同。D触发器在时钟信号的上升沿或下降沿触发,将数据输入端的电平存储到触发器中。D触发器广泛应用于数据传输和同步。

- JK触发器(JK Flip-Flop)

JK触发器是一种具有两个输入端的双稳态触发器,分别称为J端和K端。JK触发器具有多种工作模式,如置位、复位、保持和翻转。JK触发器可以通过组合实现其他类型的触发器,如T触发器和T'触发器。

- T触发器(T Flip-Flop)

T触发器是一种具有一个输入端的双稳态触发器,其输出在输入端为高电平时翻转。T触发器常用于实现移位寄存器和计数器。

- 同步RS触发器(Synchronous RS Flip-Flop)

同步RS触发器是一种具有同步特性的双稳态触发器,其状态转换由时钟信号和置位端、复位端共同控制。同步RS触发器可以有效避免亚稳态问题,提高电路的稳定性。

- 边沿触发器(Edge-Triggered Flip-Flop)

边沿触发器是一种在时钟信号的上升沿或下降沿触发的双稳态触发器。边沿触发器具有较高的抗干扰能力,常用于高速数字电路设计。

- 负边沿触发器(Negative-Edge Triggered Flip-Flop)

负边沿触发器是一种在时钟信号的下降沿触发的双稳态触发器。负边沿触发器在某些特定应用中具有优势,如实现负边沿触发的计数器。

- 正边沿触发器(Positive-Edge Triggered Flip-Flop)

正边沿触发器是一种在时钟信号的上升沿触发的双稳态触发器。正边沿触发器在大多数数字电路设计中得到广泛应用。

- 双稳态触发器的变体

除了上述基本类型外,双稳态触发器还有许多变体,如带使能端的触发器、带清零端的触发器、带预置端的触发器等。这些变体在特定应用中具有优势,可以根据实际需求进行选择。

二、双稳态触发器的工作原理

双稳态触发器的工作原理主要基于逻辑门和反馈回路。以下是几种常见触发器的工作原理:

- 基本RS触发器

基本RS触发器由两个交叉耦合的反相器组成,其输出端分别连接到输入端。当置位端为高电平时,触发器输出为高电平;当复位端为高电平时,触发器输出为低电平。基本RS触发器存在竞争冒险问题,需要改进。

- 钟控RS触发器

钟控RS触发器在基本RS触发器的基础上增加了一个时钟输入端。当置位端和复位端同时为高电平时,触发器保持当前状态不变。时钟信号控制触发器的状态转换,有效避免竞争冒险问题。

- D触发器

D触发器具有数据输入端,其输出与数据输入端相同。在时钟信号的上升沿或下降沿触发时,D触发器将数据输入端的电平存储到触发器中。

-

存储

+关注

关注

13文章

4202浏览量

85533 -

二进制

+关注

关注

2文章

772浏览量

41549 -

数字电路

+关注

关注

193文章

1592浏览量

80356

发布评论请先 登录

相关推荐

双稳态触发器可分为什么类型

双稳态触发器可分为什么类型

评论