Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

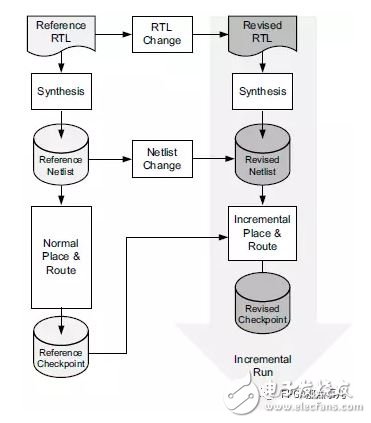

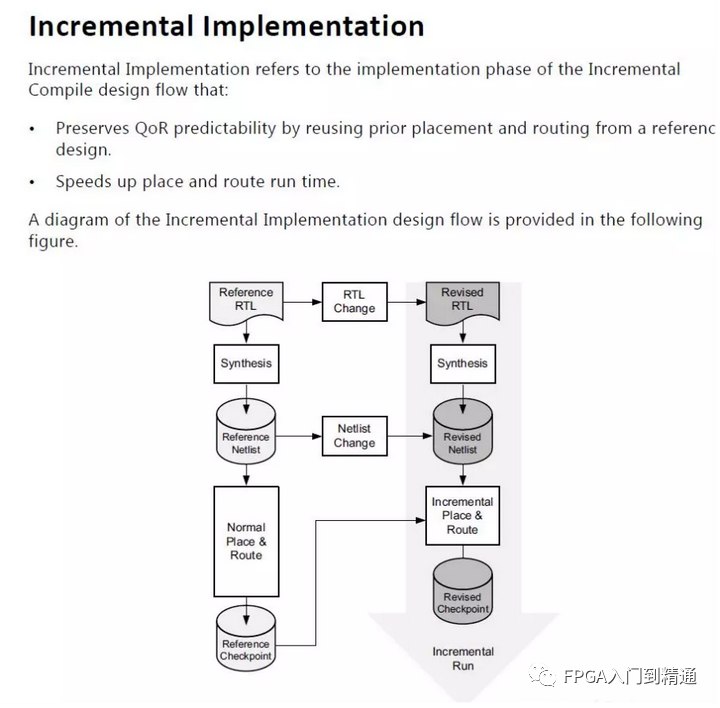

下图是增量编译的流程:

增量编译需要已经编译完成的原始设计的dcp文件作为参考,当我们在原始设计上做微小的改动时,就可以使用增量编译的流程。这些改动包括:

- RTL代码的微小修改

- 网表的微小修改,比如增加或者改变ILA

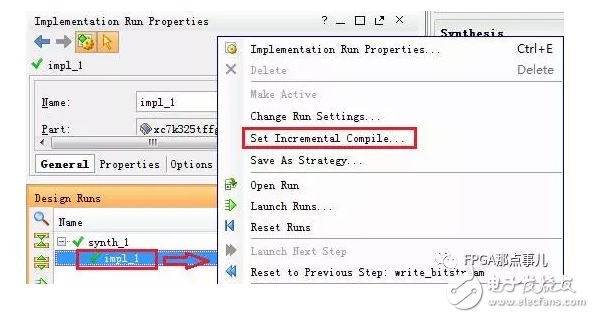

在Vivado里面,使能IncrementalCompile的方式非常简洁,在Impl run上右键选择“Set Incremental Compile…”,然后设置相应的参考dcp文件即可:

Tips:

1. 当参考设计和当前设计的相似度大于95%的时候,最适合用增量编译技术

相似度低于75%时,工具会关闭增量编译

2. 有些时候,即使很小的RTL改动,也会造成网表的巨大差异。比如

a) 改变HDL中的某些全局常量

b) 增加总线的位宽

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Vivado

+关注

关注

19文章

803浏览量

66194

发布评论请先 登录

相关推荐

Altium如何放置compile mask(编译屏蔽)

方法步骤如下:原理图界面上place(放置)-->directives(指示)-->compile mask(编译屏蔽),拖动鼠标,框住不需编译的电路。 取消的方法:不需要删除,之需要在编译

发表于 09-17 14:08

谁能缩短大容量FPGA的编译时间?增量式编译QIC!

增量式编译(Incremental Compilation)是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!在本文中我们将阐述QIC在缩短

发表于 12-25 11:26

•4897次阅读

Vivado Design Suite 2015.3的新功能介绍

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量

Vivado Design Suite 2015.3新增量编译功能介绍

了解Vivado实现中2015.3中的新增量编译功能,包括更好地处理物理优化和自动增量

Vivado综合引擎的增量综合流程

从 Vivado 2019.1 版本开始,Vivado 综合引擎就已经可以支持增量流程了。这使用户能够在设计变化较小时减少总的综合运行时间。

发表于 07-21 11:02

•1622次阅读

Vivadoz中增量编译与设计锁定

关于增量编译所谓增量实现,更严格地讲是增量布局和增量布线。它是在设计改动较小的情形下参考原始设计的布局、布线结果,将其中未改动的模块、引脚和

发表于 12-20 19:11

•6次下载

Vivado增量编译的基本概念、优点、使用方法以及注意事项

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado

Xilinx Vivado使用增量实现

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。它解决了实现阶段针对快速迭代的需求,显著节省了编译时间,还能确保所得结果和性能的可预测性

Vivado中的Incremental Compile增量编译技术详解

Vivado中的Incremental Compile增量编译技术详解

评论