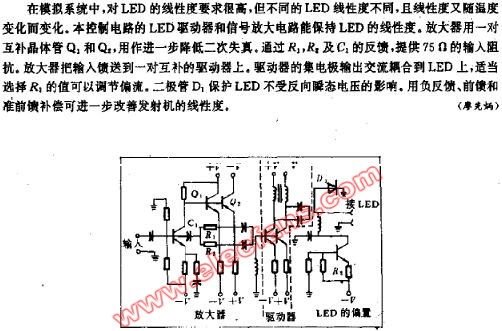

新兴的射频数据转换器——即RF DAC和RF ADC,就架构意义而言,使小型多频段收发器的创建变成了一种可能。但这些新设备固有的非线性却是绊脚石。例如,RF设备的非线性在频域有两面:带内和带外。带内非线性指的是TX带内不必要的频率,而带外非线性则指的是TX带外的寄生频率。

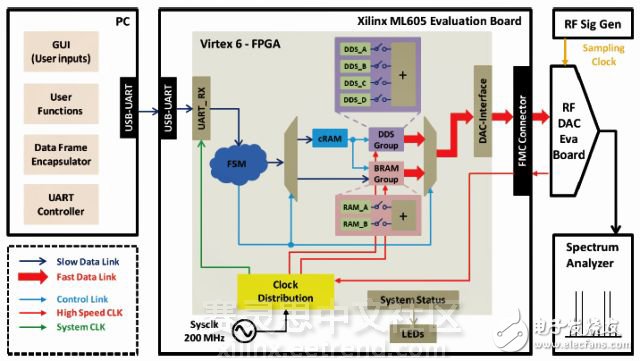

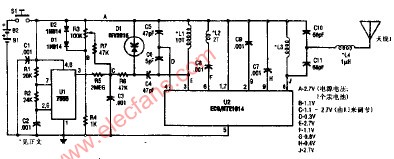

在爱尔兰贝尔实验室,我们创建了一个灵活的软硬件平台,用以对下一代无线系统的潜力股RF DAC进行快速评估。这个研发项目有三大关键元素:高性能的Xilinx FPGA,Xilinx知识产权IP及MATLAB。我们在试图尽量少使用FPGA资源的同时,又尽可能保持系统的灵活性。以下为系统框图:

我们挑选了Analog Devices公司最新的RF-DAC评估板(AD9129和AD9739a)和Xilinx ML605评估板。ML605评估板配有Virtex-6XC6VLX240T-1FFG1156 FPGA器件,使用快速开关I/O (高达710 MHz)和串并收发器单元(高达5 Gbps)来联接RF DAC。

设计有关FPGA的部分中涵括了时钟分配单元、基于状态机的系统控制单元和DDS基于内核的多频声生成单元。另还包含了两个建立在块RAM的单元:基于BRAM的小型控制消息存储单元(cRAM内核)和基于BRAM数组的用户数据存储单元(dRAM 内核)。

设计有关FPGA的部分中涵括了时钟分配单元、基于状态机的系统控制单元和DDS基于内核的多频声生成单元。另还包含了两个建立在块RAM的单元:基于BRAM的小型控制消息存储单元(cRAM内核)和基于BRAM数组的用户数据存储单元(dRAM 内核)。

时钟就是FPGA的生命。为确保多个时钟在FPGA内存库内的合理分布,我们筛选了Xilinx时钟管理内核,该内核能以简单互动的方式对时钟进行定义和说明。状态机周围还建立了紧凑的指令内核,用以充当系统控制单元。

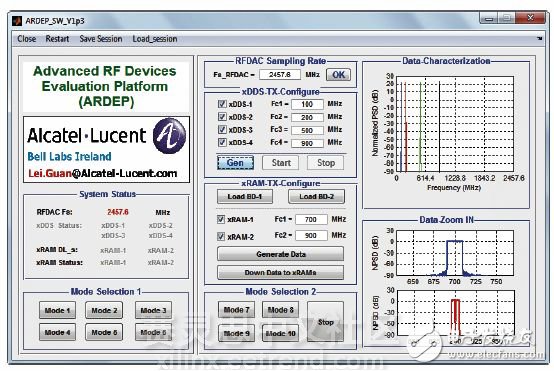

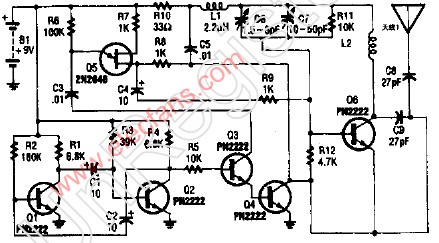

我们设计了两款测试方案:连续波(CW)信号测试(xDDS)和带宽信号测试(xRAM)。多频连续波测试一直是射频工程师测试射频组件非线性特征的首选。秉承相同的测试理念,我们又创建了一个基于直接数字合成器(DDS)的可调四频段逻辑内核,该内核可以在两个独立的频带中,使用一对深浅不一的信号来刺激RF DAC。通过单独调整四频段,便可以评估RF DAC的线性性能——即,在频域的位置及互调刺激的功率。CW信号测试则是一个固有的窄带操作。为进一步评估RF DAC的宽带性能,则必须使用并发多波段、多模信号,如:双模UMTS和LTE2.1 GHz和2.6 GHz信号。

选择MATLAB作为主机软件的原因是,其在数字信号处理(DSP)方面具有诸多优势。并且,MATLAB也可以提供一个名为GUIDE的实用工具,用于布局为平台创建的图形用户界面(GUI)。以下图表对GUI进行了说明:

-

转换器

+关注

关注

27文章

8755浏览量

148308 -

dac

+关注

关注

43文章

2315浏览量

191727

发布评论请先 登录

相关推荐

RF DAC多频带发射器线性性能怎么评估?

一个针对多频段应用的直接RF发射机例子

雷达发射机的任务和基本组成

多标准无线电基站发射机测试

实验用雷达发射机的系统设计

UG-1432:ADF5902 24 GHz、ISM波段多通道FMCW雷达发射机评估

一文详解DAC多频段发射机的线性评估

一文详解DAC多频段发射机的线性评估

评论