随着大数据中心、云计算服务的不断增长,对于系统性能、功能和带宽的要求也是越来越高,同时也驱动通信总线技术不断取得新的进步。由英特尔提出的第三代高性能I/O总线技术—PCIE总线解决了PCI总线的不足,它的发展将取代PCI成为新型的数据总线,其提供了更加完善的性能,更多的功能,更强的可扩展性和更低的成本。

PCI总线协议采用的是并行结构,也就是说总线上所有扩展设备都是共享总线带宽,而PCIe总线协议则有所不同,采用的是高速差分总线规格,并采用端到端的连接方式,即每一条PCIe通信链路中只能连接两台设备,除此之外PCIe还采用了网络通信中的一些技术,比如支持多种数据路由方式、基于多通路的数据传输方式以及基于报文的数据传输,并且充分考虑并优化了数据传输过程中的服务质量(QoS,Quality of Service)问题。

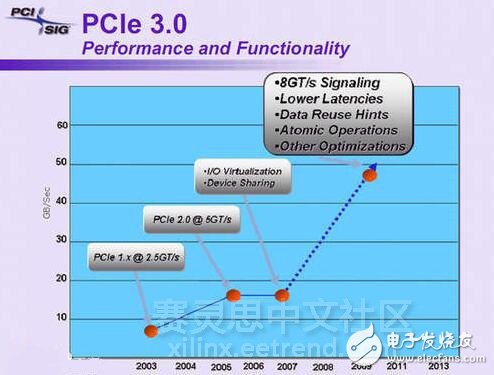

图1:PCIe高速通信总线标准的发展历程

在每个实际应用中如何最大限度的发挥PCIe总线的通信速度至关重要,Xilinx推出了一个基于高级FPGA器件和DMA(Direct Memory Access,直接内存存取)的参考解决方案:

提升PCIe总线通信速度主要从以下几方面考虑:

根据应用需求选择合适的链路速度和数据带宽

合理设定最大有效载荷

通信过程中最大可能的传输数据包大小

启用最大数量的DMA通道

轮询操作和中断操作的选择(一般轮询操作效率更高、速度更快)

除此之外我们还要选择高性能的硬件平台,Xilinx推出的参考设计采用的是KCU105 Kintex UltraScale FPGA开发套件,它采用的是最高端的Kintex UltraScale All Programmable FPGA器件,具有ASIC级别的系统性能,集成了时钟管理和电源管理等丰富特性,这款开发套件非常适合中高端类应用的系统原型开发,如数据中心、无线通信基础设施等。

图2:Xilinx推出的KCU105 Kintex UltraScale FPGA开发套件

Xilinx推出的Vivado开发工具也大大方便了系统的开发,其集成了丰富的IP模块,如AXI DMA、PCIe Block core等,同时还提供了IP集成器功能,实现基于Tcl、图形化的开发流程,通过IP集成器实现的模块接口通常采用业界标准的AXI4接口,支持关键IP接口的智能化自动连接,从而不管是在系统设计还是在开发效率上都带来了很大提高。

-

通信

+关注

关注

18文章

6090浏览量

136574 -

PCIe

+关注

关注

15文章

1271浏览量

83369

发布评论请先 登录

相关推荐

进一步提升PCIe总线通信速度的方法

进一步提升PCIe总线通信速度的方法

评论