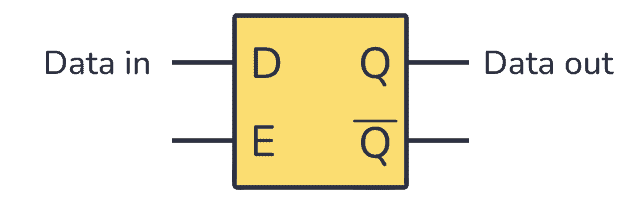

D锁存器是一种常见的数字逻辑电路,用于存储一个二进制位的状态。以下是一些常用的D锁存器型号及其特点:

- 74LS74:这是一种低功耗的正触发D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HC74:这是一种高速CMOS D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74F74:这是一种高速的正触发D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HCT74:这是一种高速CMOS D锁存器,具有4个独立的锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74LS174:这是一种具有4个独立的D锁存器的六进制同步计数器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HC174:这是一种高速CMOS六进制同步计数器,具有4个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74F174:这是一种高速的六进制同步计数器,具有4个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HCT174:这是一种高速CMOS六进制同步计数器,具有4个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74LS373:这是一种具有8个独立的D锁存器的三态输出寄存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HC373:这是一种高速CMOS三态输出寄存器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74F373:这是一种高速的三态输出寄存器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HCT373:这是一种高速CMOS三态输出寄存器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74LS574:这是一种具有8个独立的D锁存器的八进制同步计数器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HC574:这是一种高速CMOS八进制同步计数器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74F574:这是一种高速的八进制同步计数器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HCT574:这是一种高速CMOS八进制同步计数器,具有8个独立的D锁存器。它具有数据输入、时钟输入、输出使能和复位功能。

- 74LS688:这是一种具有8个独立的D锁存器的八进制同步计数器,具有三态输出。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HC688:这是一种高速CMOS八进制同步计数器,具有8个独立的D锁存器和三态输出。它具有数据输入、时钟输入、输出使能和复位功能。

- 74F688:这是一种高速的八进制同步计数器,具有8个独立的D锁存器和三态输出。它具有数据输入、时钟输入、输出使能和复位功能。

- 74HCT688:这是一种高速CMOS八进制同步计数器,具有8个独立的D锁存器和三态输出。它具有数据输入、时钟输入、输出使能和复位功能。

以上是一些常用的D锁存器型号,每种型号都有其特定的应用场景和特点。在选择D锁存器时,需要根据具体的应用需求和电路设计来选择合适的型号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

二进制

+关注

关注

2文章

801浏览量

41779 -

计数器

+关注

关注

32文章

2276浏览量

95106 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15889 -

D锁存器

+关注

关注

0文章

13浏览量

3735

发布评论请先 登录

相关推荐

锁存器与寄存器有哪些区别

一组输出,当前什么输入就根据函数得到什么输出,实时跟踪变化,这样也就容易有冒险、竞争之类的问题产生毛刺。 锁存器:电平敏感 always @ (enable) ??if (enable

D锁存器的基本实现

在Verilog HDL中实现锁存器(Latch)通常涉及对硬件描述语言的基本理解,特别是关于信号如何根据控制信号的变化而保持或更新其值。锁存

常用的d锁存器型号有哪些

常用的d锁存器型号有哪些

评论