D锁存器(Data Latch)和SR锁存器(Set-Reset Latch)是数字电路中常见的两种存储元件。它们在数字系统中扮演着重要的角色,用于存储和传递信息。然而,这两种锁存器在设计和应用上存在一些差异,D锁存器在一定程度上解决了SR锁存器的一些问题。

- 引言

在数字电路设计中,锁存器是一种基本的存储元件,用于存储一位二进制信息。锁存器的种类有很多,其中D锁存器和SR锁存器是最常见的两种。这两种锁存器在功能和应用上有一定的差异,D锁存器在某些方面解决了SR锁存器的一些问题。

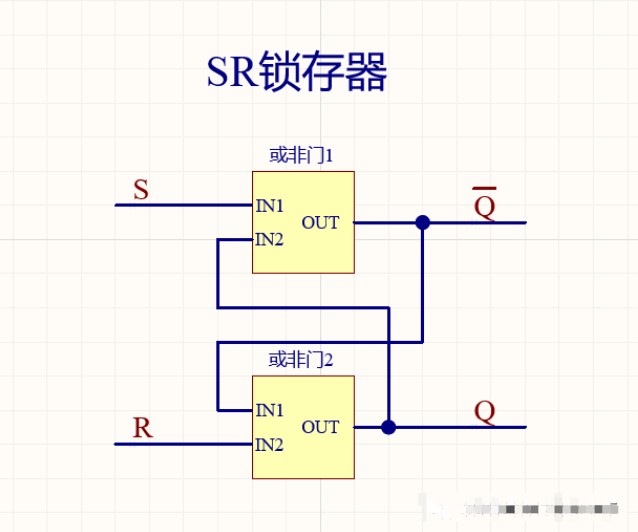

- SR锁存器的基本概念

SR锁存器是一种基本的存储元件,由两个晶体管、两个电阻和两个二进制输入信号组成。它具有两个输入端:置位端(Set)和复位端(Reset)。当置位端接收到高电平信号时,锁存器的输出端将被置为高电平;当复位端接收到高电平信号时,锁存器的输出端将被置为低电平。SR锁存器的工作原理如下:

- 当Set端为高电平,Reset端为低电平时,晶体管T1导通,T2截止,输出端Q为高电平。

- 当Reset端为高电平,Set端为低电平时,晶体管T2导通,T1截止,输出端Q为低电平。

- 当Set端和Reset端都为高电平时,锁存器进入不确定状态,输出端Q的电平不确定。

- SR锁存器存在的问题

尽管SR锁存器在某些应用中具有优势,但它也存在一些问题:

- 不确定状态:当Set端和Reset端都为高电平时,锁存器进入不确定状态,输出端Q的电平不确定。这可能导致电路的不稳定和错误。

- 竞争冒险:在某些情况下,Set端和Reset端的信号可能同时发生变化,导致锁存器的输出端出现竞争冒险现象,即输出端Q的电平在短时间内发生多次变化。

- 功耗问题:SR锁存器在工作过程中,晶体管的导通和截止会导致一定的功耗。

- D锁存器的基本概念

D锁存器是一种改进型的存储元件,它在SR锁存器的基础上增加了一个数据输入端(Data)。D锁存器的工作原理如下:

- 当数据输入端D为高电平时,锁存器的输出端Q将被置为高电平。

- 当数据输入端D为低电平时,锁存器的输出端Q将被置为低电平。

- D锁存器如何解决SR锁存器的问题

D锁存器在设计上解决了SR锁存器的一些问题,具体表现在以下几个方面:

5.1 解决不确定状态问题

在D锁存器中,通过引入数据输入端D,消除了SR锁存器中的不确定状态。当数据输入端D为高电平时,输出端Q被置为高电平;当数据输入端D为低电平时,输出端Q被置为低电平。这样,D锁存器的输出端Q始终处于确定状态,避免了SR锁存器中的不确定状态问题。

5.2 减少竞争冒险现象

由于D锁存器只有一个数据输入端,不存在Set端和Reset端同时变化的情况,因此减少了竞争冒险现象的发生。在D锁存器中,输出端Q的电平变化完全取决于数据输入端D的电平,不会出现短时间内多次变化的情况。

5.3 降低功耗

D锁存器在工作过程中,晶体管的导通和截止次数相对较少,因此功耗相对较低。与SR锁存器相比,D锁存器在功耗方面具有一定的优势。

- D锁存器的应用

D锁存器在数字电路设计中具有广泛的应用,例如:

- 数据缓冲:D锁存器可以用于数据缓冲,将输入端的数据暂存起来,以便在需要时进行读取。

- 数据同步:在数字系统中,D锁存器可以用于实现数据同步,确保数据在不同的时钟域之间正确传输。

- 数据选择:D锁存器可以用于实现数据选择功能,根据控制信号选择不同的数据输入。

- 结论

D锁存器在设计上解决了SR锁存器的一些问题,如不确定状态、竞争冒险现象和功耗问题。D锁存器具有广泛的应用,如数据缓冲、数据同步和数据选择等。

-

存储

+关注

关注

13文章

4353浏览量

86113 -

数字电路

+关注

关注

193文章

1629浏览量

80780 -

SR

+关注

关注

1文章

35浏览量

23457 -

D锁存器

+关注

关注

0文章

13浏览量

3729

发布评论请先 登录

相关推荐

d锁存器解决了sr锁存器的什么问题

d锁存器解决了sr锁存器的什么问题

评论