SR锁存器是一种重要的数字电路元件,用于存储和锁定一个比特的信息。其输出端口Q的值是根据输入端口S(置位)和R(复位)的信号来确定的。

一、SR锁存器的基本结构和工作原理

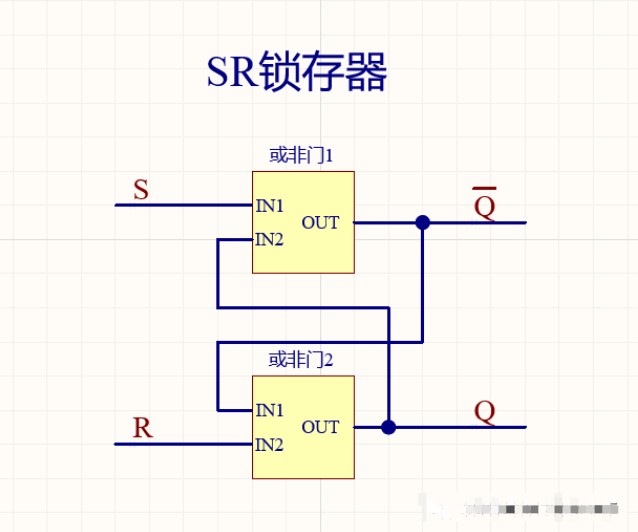

SR锁存器由两个互补的可控开关(通常是由逻辑门电路构成)组成,可以将输入信号锁存为输出信号。其基本结构通常包括两个或非门(NOR gate)或与非门(NAND gate)交叉连接而成,形成两个相互依赖的存储单元。

工作原理简述 :

- 当S=1且R=0时,无论Q的初始状态如何,通过逻辑门的运算,Q将被置为1,实现置位功能。

- 当S=0且R=1时,无论Q的初始状态如何,Q将被置为0,实现复位功能。

- 当S=0且R=0时,锁存器保持当前状态不变。

- 当S=1且R=1时,锁存器处于非法状态,Q的值无法确定,应避免这种情况。

二、SR锁存器确定Q值的详细过程

1. 初始化状态

在SR锁存器开始工作时,通常会有一个初始化过程。在大多数情况下,初始状态下Q的值被设置为0(或根据具体设计而定)。这个初始状态是锁存器工作的起点。

2. 输入信号分析

SR锁存器的Q值是根据S和R端口的输入信号来确定的。具体来说:

- **S=1, R=0** :此时,无论Q的初始状态如何,由于S端口的置位信号有效,锁存器将Q置为1。这是置位操作,表示将锁存器设置为高电平状态。

- **S=0, R=1** :此时,无论Q的初始状态如何,由于R端口的复位信号有效,锁存器将Q置为0。这是复位操作,表示将锁存器设置为低电平状态。

- **S=0, R=0** :当S和R端口都为0时,锁存器将保持其当前状态不变。即如果Q为1,则保持为1;如果Q为0,则保持为0。

- **S=1, R=1** :这是一个非法状态,因为S和R端口同时有效会导致锁存器的输出不确定。在实际应用中,应通过逻辑设计来避免这种情况的发生。

3. 时钟信号的影响(对于带时钟的SR锁存器)

在某些设计中,SR锁存器可能包含时钟信号输入。时钟信号用于控制锁存器何时读取S和R端口的输入信号,并将其锁定在Q端口上。当时钟信号为高电平时,锁存器将读取S和R端口的输入信号,并根据上述规则确定Q的值。当时钟信号为低电平时,锁存器将保持其当前状态不变,不会读取新的输入信号。

因此,在使用带时钟的SR锁存器时,需要正确设置时钟信号的频率和占空比,以确保锁存器能够正确读取输入信号并锁定输出状态。

三、实际应用中的注意事项

- 避免非法状态 :在实际应用中,应确保S和R端口不会同时为1,以避免锁存器进入非法状态。这可以通过添加额外的逻辑电路来实现,如使用与门来检测S和R端口的状态,并在它们同时为1时产生一个禁止信号来阻止锁存器的操作。

- 稳定性与可靠性 :SR锁存器的稳定性和可靠性对于整个数字电路的性能至关重要。因此,在设计时应考虑使用高质量的元件和合理的布局布线来减少噪声和干扰的影响。

- 时钟信号的同步 :对于带时钟的SR锁存器,应确保时钟信号的同步性以避免数据丢失或错误。这通常要求时钟信号的频率和相位与其他相关信号保持一致。

四、结论

SR锁存器通过S和R端口的输入信号来确定Q的值。其工作原理简单而有效,能够在数字电路中实现数据的存储和锁定功能。在实际应用中,需要注意避免非法状态的发生,并确保时钟信号的同步性和稳定性以提高整个电路的性能和可靠性。通过合理的设计和使用,SR锁存器可以在各种数字电路中发挥重要作用。

-

元件

+关注

关注

4文章

968浏览量

36974 -

锁存器

+关注

关注

8文章

918浏览量

41773 -

数字电路

+关注

关注

193文章

1631浏览量

81075 -

SR

+关注

关注

1文章

35浏览量

23505

发布评论请先 登录

相关推荐

sr锁存器如何确定q的值

sr锁存器如何确定q的值

评论