在数字逻辑电路中,D触发器(Data Flip-Flop)和RS触发器(Reset-Set Flip-Flop)是两种常用的存储单元。它们在功能上有一定的相似性,但也存在一些差异。

一、D触发器与RS触发器的基本概念

- D触发器

D触发器是一种具有数据输入(D)、时钟输入(CLK)和输出(Q)的存储单元。当CLK信号的上升沿或下降沿到来时,D触发器将输入端的数据D存储到输出端Q。D触发器具有以下特点:

(1)数据传输:D触发器可以实现数据的同步传输,即在时钟信号的控制下,数据从输入端D传输到输出端Q。

(2)存储功能:D触发器具有存储功能,可以将输入端的数据D存储在输出端Q,实现数据的保持。

(3)时钟控制:D触发器的存储功能受到时钟信号的控制,只有在时钟信号的上升沿或下降沿到来时,数据才会被存储。

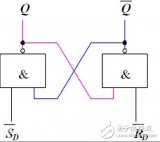

- RS触发器

RS触发器是一种具有置位(Set)输入(S)、复位(Reset)输入(R)和输出(Q)的存储单元。RS触发器可以实现数据的置位和复位操作。RS触发器具有以下特点:

(1)置位操作:当S=1且R=0时,RS触发器将输出端Q置为1。

(2)复位操作:当R=1且S=0时,RS触发器将输出端Q置为0。

(3)保持操作:当S=0且R=0时,RS触发器保持输出端Q的当前状态不变。

(4)无效状态:当S=1且R=1时,RS触发器的状态不确定,可能导致输出端Q的不稳定。

二、D触发器与RS触发器的功能转换

- 利用D触发器实现RS触发器

通过将D触发器的输入端D与RS触发器的置位输入S相连接,可以实现RS触发器的置位功能。同时,通过将D触发器的时钟输入CLK与RS触发器的复位输入R相连接,可以实现RS触发器的复位功能。具体实现方法如下:

(1)置位功能:将D触发器的输入端D与RS触发器的置位输入S相连接,当S=1时,D触发器的输出端Q将被置为1。

(2)复位功能:将D触发器的时钟输入CLK与RS触发器的复位输入R相连接,当R=1时,D触发器的输出端Q将被复位为0。

(3)保持功能:当S=0且R=0时,D触发器的输出端Q将保持当前状态不变。

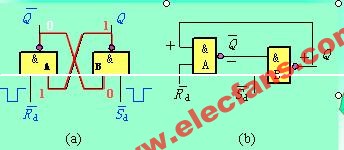

- 利用RS触发器实现D触发器

通过将RS触发器的置位输入S与复位输入R分别与D触发器的数据输入D和时钟输入CLK相连接,可以实现D触发器的功能。具体实现方法如下:

(1)数据传输:将RS触发器的置位输入S与D触发器的数据输入D相连接,当S=1时,RS触发器的输出端Q将存储D触发器的数据输入D。

(2)时钟控制:将RS触发器的复位输入R与D触发器的时钟输入CLK相连接,当R=1时,RS触发器的输出端Q将被复位为0,从而实现时钟信号的控制。

(3)保持功能:当S=0且R=0时,RS触发器的输出端Q将保持当前状态不变,实现数据的保持。

三、D触发器与RS触发器在数字电路设计中的应用

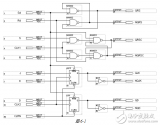

- 寄存器设计

在数字电路设计中,寄存器是一种常见的存储单元,用于存储数据和指令。D触发器和RS触发器都可以用于寄存器的设计。通过将多个D触发器或RS触发器级联,可以实现多位的数据存储。

- 计数器设计

计数器是一种用于实现数字计数功能的电路。D触发器和RS触发器都可以用于计数器的设计。通过将多个D触发器或RS触发器级联,并设置适当的置位和复位逻辑,可以实现不同进制的计数器。

- 同步时序电路设计

在同步时序电路设计中,D触发器和RS触发器都可以用于实现数据的同步传输和存储。通过合理选择D触发器或RS触发器,并设置适当的时钟信号,可以实现同步时序电路的设计。

-

数据

+关注

关注

8文章

7048浏览量

89068 -

存储

+关注

关注

13文章

4317浏览量

85867 -

RS触发器

+关注

关注

3文章

101浏览量

17947 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15823

发布评论请先 登录

相关推荐

RS触发器工作原理_RS触发器逻辑功能_RS触发器和SR触发器的区别

d与rs触发器间功能的转换

d与rs触发器间功能的转换

评论