R-S锁存器(Reset-Set Latch)是一种基本的数字逻辑电路,用于存储一位二进制信息。它由两个交叉耦合的反相器(NOT gate)和两个晶体管组成。R-S锁存器在数字电路设计中具有广泛的应用,如存储数据、实现同步等。

- R-S锁存器的基本概念

R-S锁存器是一种存储一位二进制数据的电路,它有两个稳定状态:Set状态(S)和Reset状态(R)。在Set状态下,输出Q为高电平,输出Q'(Q的反相)为低电平;在Reset状态下,输出Q为低电平,输出Q'为高电平。R-S锁存器具有两个输入端:Set输入(S)和Reset输入(R),分别用于将锁存器置为Set状态和Reset状态。

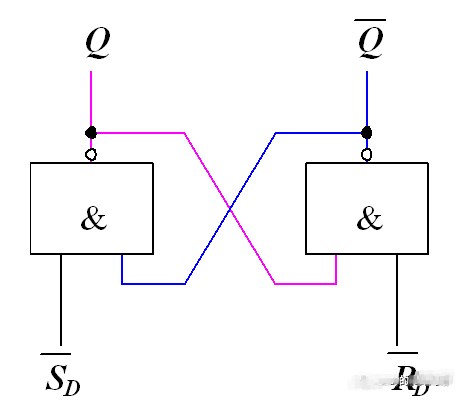

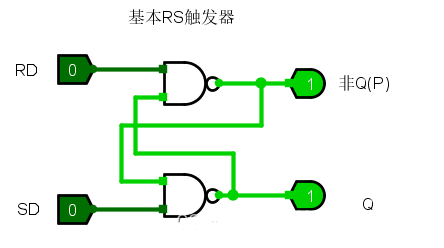

- R-S锁存器的电路结构

R-S锁存器的基本电路结构由四个晶体管组成,具体如下:

- 两个NPN晶体管:Q1和Q2,分别连接到输出Q和Q'。

- 两个PNP晶体管:Q3和Q4,分别连接到输出Q'和Q。

晶体管Q1和Q2的基极分别连接到输入S和R,晶体管Q3和Q4的基极分别连接到输出Q和Q'。这种交叉耦合的结构使得R-S锁存器具有两个稳定状态。

- R-S锁存器的工作原理

R-S锁存器的工作原理可以分为以下几个步骤:

(1)初始状态:假设R-S锁存器处于Reset状态,即输出Q为低电平,输出Q'为高电平。此时,晶体管Q1处于截止状态,晶体管Q2处于饱和状态;晶体管Q3处于饱和状态,晶体管Q4处于截止状态。

(2)Set操作:当输入S为高电平时,晶体管Q1导通,输出Q变为高电平。由于晶体管Q1和Q4的交叉耦合,晶体管Q4截止,输出Q'变为低电平。此时,R-S锁存器进入Set状态。

(3)Reset操作:当输入R为高电平时,晶体管Q2导通,输出Q'变为高电平。由于晶体管Q2和Q3的交叉耦合,晶体管Q3截止,输出Q变为低电平。此时,R-S锁存器进入Reset状态。

(4)保持状态:当输入S和R都为低电平时,R-S锁存器保持当前状态不变。

- R-S锁存器的优缺点

优点:

- 结构简单:R-S锁存器由四个晶体管组成,结构简单,易于实现。

- 存储能力强:R-S锁存器可以存储一位二进制数据,具有基本的存储功能。

缺点:

- 存在竞争冒险:当输入S和R同时为高电平时,R-S锁存器可能进入不稳定状态,导致输出不确定。

- 功耗较高:由于晶体管的导通和截止,R-S锁存器的功耗相对较高。

- R-S锁存器的应用

R-S锁存器在数字电路设计中具有广泛的应用,如:

- 数据存储:R-S锁存器可以用于存储数据,实现数据的暂存和传递。

- 同步控制:R-S锁存器可以用于实现同步控制,确保数据在不同时钟域之间的正确传输。

- 寄存器设计:R-S锁存器可以作为寄存器的基本单元,用于实现更复杂的寄存器结构。

- R-S锁存器的改进

为了解决R-S锁存器的竞争冒险问题,可以采用以下改进措施:

- 使用D锁存器:D锁存器是一种改进的R-S锁存器,它通过引入一个使能端(Enable),在使能端为高电平时,D锁存器的输出跟随输入D,避免了竞争冒险问题。

- 使用JK锁存器:JK锁存器是一种更高级的锁存器,它通过引入两个输入J和K,可以实现更灵活的控制逻辑,避免了竞争冒险问题。

-

RS

+关注

关注

3文章

140浏览量

109986 -

二进制

+关注

关注

2文章

796浏览量

41746 -

锁存器

+关注

关注

8文章

908浏览量

41620 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15865

发布评论请先 登录

相关推荐

RS锁存器的工作原理和应用实例

Rs锁存器的工作原理、优缺点及应用

Rs锁存器的工作原理、优缺点及应用

评论