RS锁存器(Reset-Set Latch)中的不定状态,是指在特定输入条件下,锁存器的输出状态变得不确定或不可预测的现象。这种不定状态主要源于RS锁存器的输入逻辑和电路特性,具体含义可以从以下几个方面来理解:

一、输入条件

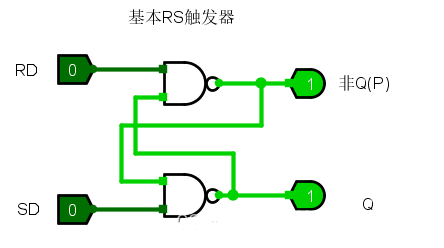

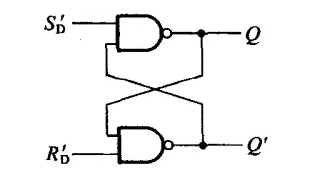

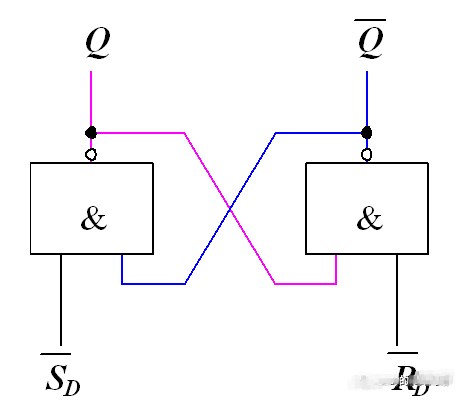

RS锁存器有两个主要的输入端:S(Set,置位端)和R(Reset,复位端)。根据锁存器的设计,当S和R同时为高电平时(在某些设计中为低电平,具体取决于门电路的类型和逻辑约定),锁存器会进入一种不确定的状态。这是因为S和R的同时有效违反了锁存器的正常操作条件,导致输出Q和Q'(Q的反相)无法稳定地保持在一个明确的状态。

二、电路特性

RS锁存器通常由两个交叉耦合的逻辑门(如或非门或非门)组成,这些逻辑门通过正反馈机制来维持锁存器的状态。然而,当S和R同时有效时,这种正反馈机制会受到干扰,因为两个输入信号都在试图改变锁存器的状态。由于信号传输的延迟和电路中的其他非理想因素(如噪声、器件差异等),这种竞争关系可能导致输出状态在0和1之间快速切换或停留在某个不确定的中间状态。

三、不定状态的影响

不定状态对RS锁存器的稳定性和可靠性构成了威胁。在数字电路中,不定状态可能导致数据错误、逻辑混乱甚至系统崩溃。因此,在设计电路时,必须避免RS锁存器进入不定状态。这通常通过确保S和R不会同时有效来实现,例如使用互斥的逻辑电路来防止这种情况的发生。

四、解决方法

为了避免RS锁存器进入不定状态,可以采取以下措施:

- 设计约束 :在电路设计阶段就明确S和R不能同时为有效状态的约束条件,并在实际电路中通过逻辑门电路或其他控制元件来确保这一约束得到遵守。

- 时序控制 :在信号传输过程中加入适当的时序控制机制,以确保S和R信号的变化是顺序发生的,而不是同时发生的。这可以通过使用时钟信号或其他同步信号来实现。

- 电路优化 :通过优化电路布局、减少信号传输延迟和降低噪声干扰等措施来提高RS锁存器的稳定性和可靠性。

综上所述,RS锁存器的不定状态是指在特定输入条件下输出状态变得不确定或不可预测的现象。这种现象主要源于RS锁存器的输入逻辑和电路特性以及信号传输的延迟和电路中的非理想因素。为了避免不定状态的发生,需要在电路设计和实现过程中采取一系列措施来确保S和R不会同时有效,并优化电路的稳定性和可靠性。

-

非门

+关注

关注

1文章

32浏览量

33880 -

低电平

+关注

关注

1文章

113浏览量

13268 -

高电平

+关注

关注

6文章

148浏览量

21366

发布评论请先 登录

相关推荐

rs锁存器不定状态的含义是什么

rs锁存器不定状态的含义是什么

评论