SR锁存器是一种常见的数字逻辑电路,它具有保持信号状态的功能。在设计和分析SR锁存器时,我们需要了解其约束条件。

一、引言

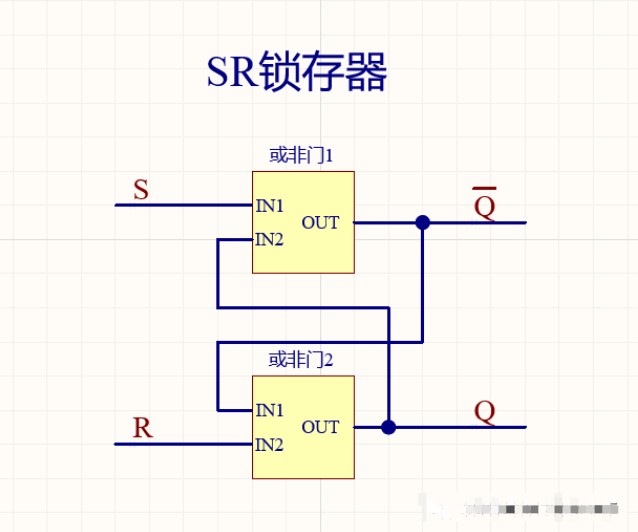

在数字逻辑电路设计中,锁存器是一种非常重要的组件。它能够存储一位二进制信息,并且能够在输入信号发生变化时保持其输出状态。SR锁存器(Set-Reset Latch)是一种基本的锁存器类型,它由两个交叉耦合的反相器和一个S(Set)输入和一个R(Reset)输入组成。本文将详细介绍SR锁存器的约束条件,以及如何根据这些条件进行设计和分析。

二、SR锁存器的基本结构

- 反相器

反相器是一种基本的数字逻辑门,它的作用是将输入信号取反。反相器的逻辑表达式为:

Q = NOT(D)

其中,Q是输出,D是输入。

- 交叉耦合

在SR锁存器中,两个反相器的输出分别连接到另一个反相器的输入,形成交叉耦合。这种结构使得SR锁存器具有存储一位二进制信息的能力。

- S输入和R输入

S输入和R输入是SR锁存器的两个控制输入。当S输入为高电平时,锁存器的输出Q被设置为高电平;当R输入为高电平时,锁存器的输出Q被重置为低电平。

三、SR锁存器的约束条件

- 竞争条件

竞争条件是SR锁存器设计中需要特别注意的问题。当S输入和R输入同时为高电平时,锁存器的输出Q将处于不确定状态。这是因为两个反相器的输出相互影响,导致它们无法稳定在一个确定的状态。为了避免竞争条件,我们需要确保S输入和R输入不会同时为高电平。

- 建立时间和保持时间

建立时间和保持时间是锁存器设计中的重要参数。建立时间是指在时钟信号的上升沿之前,输入信号需要保持稳定的最小时间。保持时间是指在时钟信号的上升沿之后,输入信号需要保持稳定的最小时间。为了保证锁存器的正常工作,我们需要确保输入信号满足建立时间和保持时间的要求。

阈值电压是SR锁存器中的一个重要参数,它决定了锁存器在不同输入条件下的输出状态。当S输入或R输入的电平高于阈值电压时,锁存器的输出Q将被设置或重置。为了保证锁存器的稳定工作,我们需要选择合适的阈值电压。

- 噪声容限

噪声容限是衡量锁存器对噪声干扰的抵抗能力的一个重要参数。在实际应用中,输入信号可能会受到噪声干扰,导致锁存器的输出Q出现错误。为了提高锁存器的可靠性,我们需要设计具有较高噪声容限的锁存器。

- 功耗

功耗是锁存器设计中需要考虑的另一个重要因素。在现代电子系统中,功耗是一个关键的指标,因为它直接影响到系统的能效和寿命。为了降低功耗,我们可以采用低功耗设计技术,如使用CMOS工艺、优化电路结构等。

四、SR锁存器的设计方法

- 选择合适的工艺

选择合适的工艺是设计SR锁存器的第一步。不同的工艺具有不同的特性,如阈值电压、噪声容限等。我们需要根据实际应用需求,选择最适合的工艺。

- 设计电路结构

在设计SR锁存器的电路结构时,我们需要考虑竞争条件、建立时间和保持时间等因素。通过合理布局和优化电路结构,我们可以提高锁存器的性能和可靠性。

- 仿真和验证

在设计过程中,仿真和验证是非常重要的环节。通过仿真,我们可以预测锁存器在不同条件下的性能,如功耗、噪声容限等。验证则是确保锁存器满足设计要求的关键步骤。

- 优化设计

根据仿真和验证的结果,我们可以对设计进行优化。优化的目标是提高锁存器的性能,降低功耗,提高可靠性等。

五、SR锁存器的应用

SR锁存器在数字逻辑电路设计中有广泛的应用,如存储器、寄存器、计数器等。通过合理设计和优化,SR锁存器可以满足不同应用场景的需求。

-

反相器

+关注

关注

6文章

311浏览量

43493 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15870 -

输入信号

+关注

关注

0文章

469浏览量

12606

发布评论请先 登录

相关推荐

基本rs触发器的约束条件

sr锁存器约束条件怎样得出的

sr锁存器约束条件怎样得出的

评论