SR锁存器作为数字电路中的一个基础元件,其设计和使用过程中存在约束项的原因是多方面的。这些约束项旨在确保SR锁存器能够稳定、可靠地工作,避免产生不可预测或错误的状态。

一、SR锁存器的基本工作原理

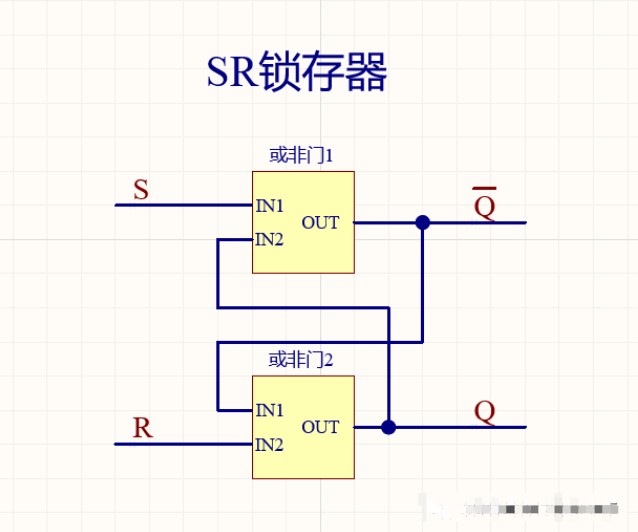

SR锁存器由两个交叉连接的反馈环组成,通常包含两个逻辑门(如或非门或非门),通过控制输入信号S(Set,置位)和R(Reset,复位)来控制其状态。SR锁存器有两个输出端Q和Q',其中Q表示当前状态,Q'是Q的补码。其基本工作原理可以概括为:

- 当S=1且R=0时,锁存器被设置为1状态,即Q=1、Q'=0。

- 当S=0且R=1时,锁存器被重置为0状态,即Q=0、Q'=1。

- 当S=0且R=0时,锁存器保持当前状态不变。

二、约束项存在的原因

1. 避免不确定状态

原因阐述 :

- S和R同时为1的情况 :当S和R同时为高电平时(在某些设计中为低电平,取决于逻辑门类型),SR锁存器会进入一种不确定状态。这是因为S和R的同时有效违反了锁存器的正常操作条件,导致输出Q和Q'无法稳定地保持在一个明确的状态。这种不确定状态可能导致数据错误、逻辑混乱甚至系统崩溃。

- 竞争冒险 :在信号传输过程中,由于信号传输延迟和电路中的非理想因素(如噪声、器件差异等),S和R信号可能在极短的时间内同时达到有效电平,从而产生竞争冒险现象。这种竞争冒险同样会导致锁存器进入不确定状态。

解决措施 :

- 设计约束:在电路设计阶段就明确S和R不能同时为有效状态的约束条件,并在实际电路中通过逻辑门电路或其他控制元件来确保这一约束得到遵守。

- 时序控制:在信号传输过程中加入适当的时序控制机制,以确保S和R信号的变化是顺序发生的,而不是同时发生的。

2. 维持稳定性

原因阐述 :

- 保持原有状态的需求 :在数字电路中,锁存器经常需要保持其存储的数据不变,以便在后续操作中使用。当S和R均为0时,锁存器应维持其原有状态不变。这是通过反馈环的正反馈机制实现的。如果反馈环的设计或实现存在问题,可能导致锁存器无法稳定地保持其状态。

解决措施 :

- 反馈环设计:优化反馈环的设计,确保其能够稳定地维持锁存器的状态。

- 噪声抑制:采取噪声抑制措施,如增加滤波电路、使用低噪声器件等,以减少噪声对锁存器稳定性的影响。

3. 同步控制

原因阐述 :

- 与时钟信号的同步 :在某些应用中,SR锁存器需要与时钟信号同步工作。时钟信号用于控制锁存器的状态更新时机。如果S和R信号的变化与时钟信号不同步,可能导致锁存器在错误的时刻更新状态,从而影响整个电路的正常工作。

解决措施 :

- 时钟同步机制:设计时钟同步机制,确保S和R信号的变化在时钟信号的特定边缘(如上升沿或下降沿)发生。

- 同步电路设计:采用同步电路设计方法,将锁存器与其他电路元件的操作同步到时钟信号的边缘上。

4. 功耗和速度优化

原因阐述 :

- 功耗考虑 :在设计SR锁存器时,需要权衡功耗和速度之间的关系。较低的功耗通常意味着较慢的速度,而较高的速度则可能带来较高的功耗。因此,设计者需要在满足性能要求的前提下尽可能降低功耗。

- 速度需求 :在某些高速应用中,SR锁存器需要具有较快的响应速度和较低的时延。这要求设计者优化锁存器的电路设计以提高其速度性能。

解决措施 :

- 低功耗设计:采用低功耗设计技术如动态功耗管理、电源门控等以降低功耗。

- 高速电路设计:优化锁存器的电路布局和信号路径以减少时延并提高响应速度。

三、总结

SR锁存器约束项的存在是为了确保锁存器能够稳定、可靠地工作并避免产生不可预测或错误的状态。这些约束项包括避免S和R同时为有效状态以防止不确定状态的产生、维持锁存器的稳定性、与时钟信号的同步以及优化功耗和速度等方面。通过遵守这些约束项并采取相应的解决措施,可以设计出高性能、高可靠性的SR锁存器以满足各种应用需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

逻辑门

+关注

关注

1文章

142浏览量

24145 -

数字电路

+关注

关注

193文章

1630浏览量

80888 -

输入信号

+关注

关注

0文章

469浏览量

12626

发布评论请先 登录

相关推荐

两种SR锁存器的约束条件

基本约束条件: SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它有两个输入端:S(Set)和R(Reset),以及两个输出端:

sr锁存器不定状态的产生原因

一、引言 SR锁存器(Set-Reset Latch)是数字电路中的一种基本存储元件,用于存储一个比特(bit)的数据。它由两个互补的门电路组成,通常是两个非门(或非门、与非门)构成,

sr锁存器如何确定q的值

SR锁存器是一种重要的数字电路元件,用于存储和锁定一个比特的信息。其输出端口Q的值是根据输入端口S(置位)和R(复位)的信号来确定的。 一、SR

SR锁存器的特性表、工作原理及应用

SR锁存器(Set-Reset Latch)是一种基本的数字逻辑电路,用于存储一位二进制信息。它具有两个稳定状态:置位状态(Set)和复位状态(Reset)。

SR锁存器的Q非和Q*是什么关系

SR锁存器是一种基本的数字逻辑电路,用于存储一位二进制信息。它由两个触发器(Set和Reset)组成,分别控制输出Q和Q非。在这篇文章中,我

SR锁存器有约束项的原因

SR锁存器有约束项的原因

评论