时序逻辑电路本身并不直接“产生”锁存器,但锁存器是时序逻辑电路中的重要组成部分。时序逻辑电路(Sequential Logic Circuits)与组合逻辑电路(Combinational Logic Circuits)不同,它能够在任何给定时刻的输出不仅取决于当前的输入,还取决于电路过去的输入(即电路的当前状态)。这种记忆功能使得时序逻辑电路能够处理更复杂的问题,如存储数据、进行状态转换等。

锁存器(Latch)是时序逻辑电路中的一种基础元件,用于存储一位或多位二进制数据。锁存器通过控制信号(如使能信号或时钟信号)来锁定或更新其存储的数据。当控制信号有效时,锁存器将输入的数据存储在内部,并在控制信号无效时保持该数据不变。这种特性使得锁存器成为实现时序逻辑电路的关键元素之一。

常见的锁存器类型包括RS锁存器、D锁存器等。这些锁存器通过不同的控制逻辑和反馈机制来实现数据的存储和更新。例如,RS锁存器具有两个控制输入端S和R,分别用于置位(Set)和复位(Reset)操作;D锁存器则具有一个数据输入端D和一个控制输入端(通常是时钟信号或使能信号),用于在控制信号有效时将D端的数据锁存到输出端。

时序逻辑与锁存器概述

1. 数字逻辑基础

数字逻辑是电子工程和计算机科学中的一个基础领域,它涉及到使用二进制数字信号来表示和处理信息。数字逻辑的核心是逻辑门,包括与门(AND)、或门(OR)、非门(NOT)、异或门(XOR)等,这些逻辑门可以组合成更复杂的逻辑电路。

2. 时序逻辑的定义

时序逻辑是一种特殊的数字逻辑,它使用时钟信号来同步电路的操作。在时序逻辑中,数据的传输和处理是按照时钟信号的周期性变化进行的。这种同步机制可以减少电路中的竞争条件和冒险,提高电路的稳定性和可靠性。

3. 锁存器的概念

锁存器是一种存储一位二进制信息的电路,它可以在没有时钟信号的情况下保持其输出状态。锁存器通常由一个或多个触发器(Flip-Flops)组成,这些触发器可以在特定条件下改变其状态。

锁存器的类型和工作原理

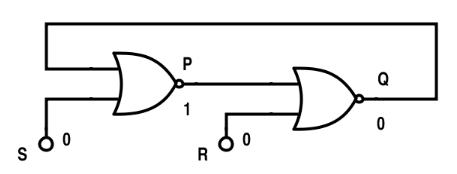

1. SR锁存器(Set-Reset Latch)

SR锁存器是最基本的锁存器类型,它有两个输入端:置位(Set)和复位(Reset)。当置位端被激活时,锁存器的输出将被设置为高电平;当复位端被激活时,输出将被设置为低电平。

2. D锁存器(Data Latch)

D锁存器是一种单数据输入的锁存器,其输出直接反映输入端的数据状态。D锁存器通常用于数据的暂存和传输。

3. JK锁存器(Jack-Kill Latch)

JK锁存器是一种具有两个输入端的锁存器,分别标记为J和K。JK锁存器可以执行置位、复位、保持和翻转操作,这使得它在时序逻辑设计中非常灵活。

时序逻辑中的锁存器应用

1. 数据暂存

在数字电路中,锁存器常用于暂存数据,以便在适当的时刻将数据传输到下一个逻辑阶段。这种暂存机制可以减少电路中的数据冲突和延迟。

2. 信号同步

在复杂的数字系统中,不同的逻辑模块可能以不同的速率运行。使用锁存器可以实现信号的同步,确保数据在正确的时刻被处理。

3. 状态机设计

状态机是时序逻辑设计中的一个重要组成部分,它可以控制电路的状态转换。锁存器在状态机设计中用于存储当前状态,以便在下一个时钟周期进行状态转换。

锁存器与触发器的区别

1. 触发器的定义

触发器是一种具有时钟输入的存储元件,它可以在时钟信号的控制下改变其状态。触发器通常由两个锁存器级联而成,具有更严格的时序特性。

2. 锁存器与触发器的比较

- 锁存器没有时钟控制,而触发器有。

- 触发器具有更严格的时序特性,可以减少亚稳态的风险。

- 在某些应用中,触发器可以替代锁存器,但反之则不一定。

时序逻辑设计中的挑战

1. 时钟偏斜和时钟抖动

时钟信号在传输过程中可能会受到干扰,导致时钟偏斜或抖动。这些问题会影响时序逻辑的正确性。

2. 亚稳态问题

在某些条件下,锁存器或触发器可能进入亚稳态,即输出在一段时间内不确定。这可能会导致电路的不稳定和错误。

3. 竞争条件和冒险

在复杂的时序逻辑设计中,不同的信号路径可能会导致竞争条件和冒险,从而影响电路的性能和可靠性。

-

二进制

+关注

关注

2文章

801浏览量

41853 -

锁存器

+关注

关注

8文章

918浏览量

41758 -

时序逻辑

+关注

关注

0文章

39浏览量

9226 -

存储数据

+关注

关注

0文章

89浏览量

14179

发布评论请先 登录

相关推荐

时序逻辑会产生锁存器吗

时序逻辑会产生锁存器吗

评论