十多年来,Cadence 对 PCIe 技术的坚定承诺和支持,在业界有目共睹。我们深知强大 PCIe 生态系统的重要性,并感谢 PCI-SIG 提供的平台。在 PCI-SIG 开发者大会迎来 32 周年之际,Cadence 宣布面向 HPC/AI 市场推出完整的 PCIe 7.0 IP 解决方案。

▋ PCIe 标准为何如此重要?

从 GPIO 等最简单的构建块到最先进的高速接口,IP 子系统是整个芯片制造生态系统的命脉。而推动 IP 发展的一个关键因素便是工业界和学术界在接口标准和协议制定上的合作。PCI-SIG 引领了一些关键定义和合规规范的制定,并确保了接口 IP 的互操作性。

HPC/AI 市场不断要求高吞吐量、低延迟和低功耗,这推动着技术的进步,促使 PCIe 技术持续发展,可服务于未来几代。作为 PCI-SIG 的成员,Cadence 能够尽早获知规范的变化和最新合规标准等重要信息。PCIe 7.0 及更高规范将助推市场不断扩展,而我们期待帮助我们的客户使用 Cadence IP 解决方案构建一流的尖端 SoC。

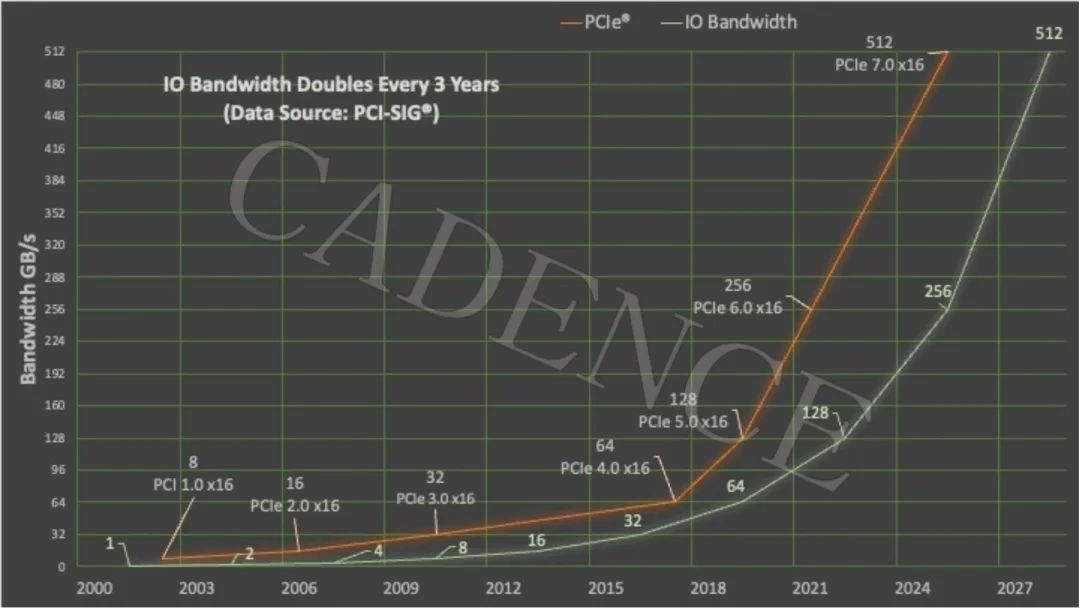

图 1:PCIe 数据传输速率变化(来源:PCI-SIG)

▋ 今年的开发者大会有何新看点?

在 2024 开发者大会上,PICe 7.0 标准成为焦点,Cadence 今年展示了面向 PCI 7.0 的一整套 IP 子系统解决方案。

▋ Cadence 有何与众不同之处?

Cadence 始终坚持为测试芯片构建一个完整的子系统,包括 8 通道 PHY 和一个完整的 8 通道控制器。在测试芯片中添加一个控制器,可以显著提高特性分析和压力测试的效率和粒度,同时使我们能够展示与真实系统的互操作性。此外,我们还可以将整个协议栈作为一个 8 通道的解决方案进行测试,其中涵盖客户实际使用的诸多应用。这种方法能够帮助客户大大降低 SoC 设计相关风险。

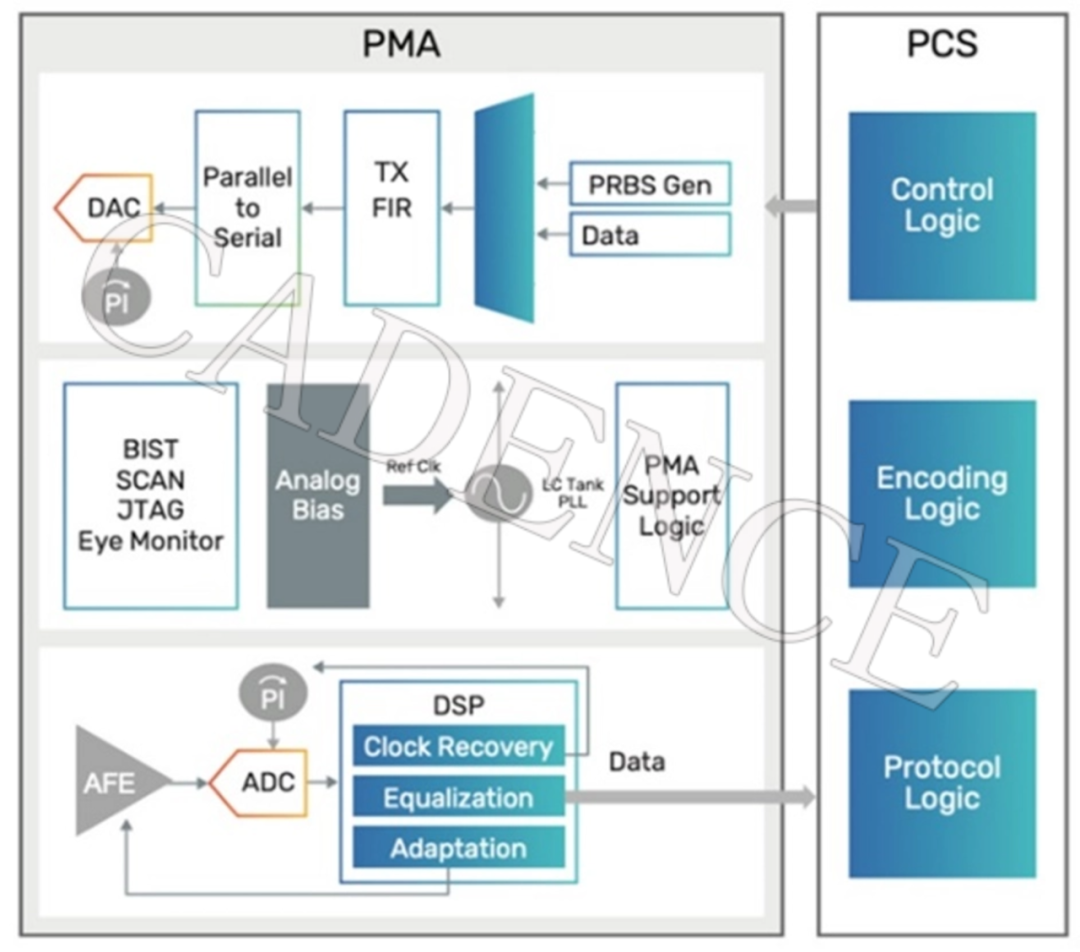

图 2:Piper——Cadence 面向 PCIe 7.0 的 PHY IP

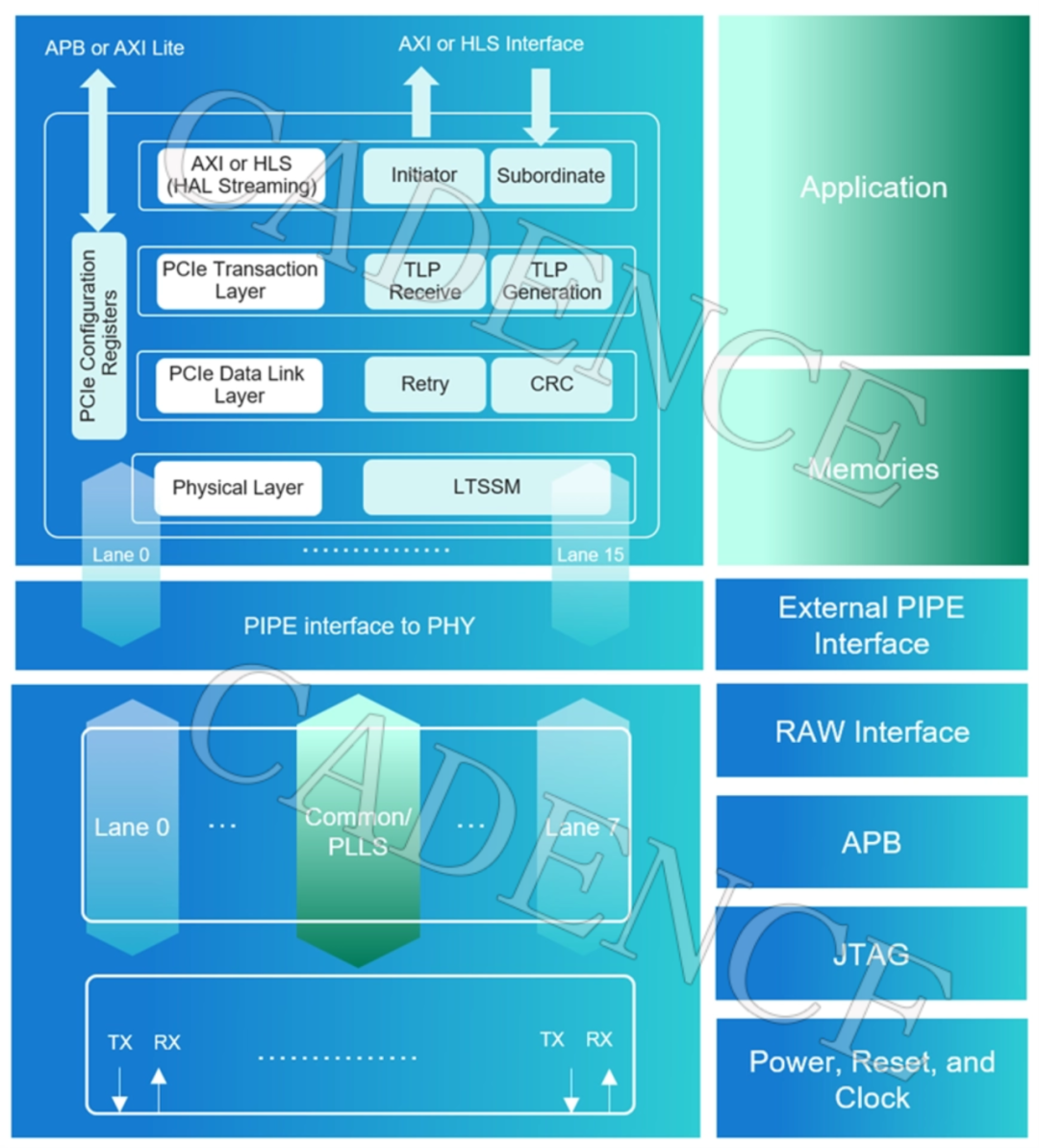

图 3:业界首款面向 PCIe 7.0 的 IP 子系统

这适用于哪个市场?

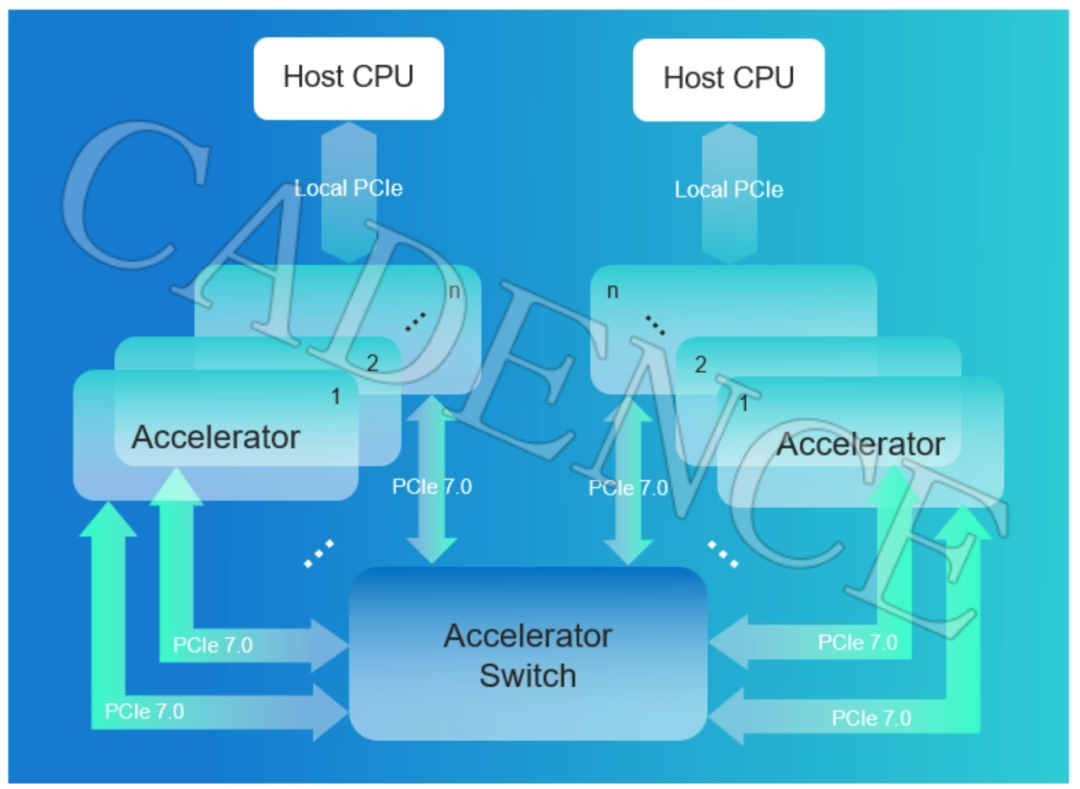

如今,加速计算已成为主流,PCIe 链路在系统中的作用随之愈发凸显。在服务器或计算集群内,要跨多个图形处理器(GPU)或加速器扩展复杂的计算任务,实现 GPU 之间的直接通信至关重要。业内逐渐认识到,要实现高性能计算,需要可扩展的开放式架构。随着 AI 和数据密集型应用的发展,对这种技术的需求可能增加,因此 PCIe 7.0 将成为下一代接口 IP 的关键部分。

下图展示了 PCIe 7.0 的潜在用例。

图 4:PCIe 7.0 用例

▋ 光纤链路为何如此重要?

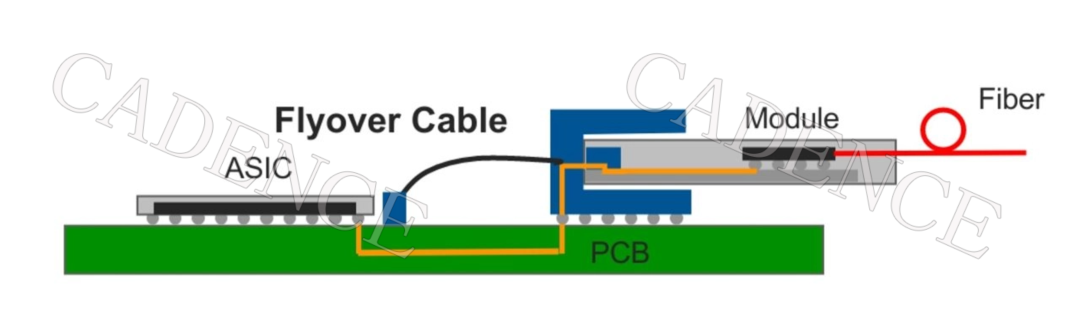

如今,训练 AI/ML 模型需要多个数据中心协作,而这些数据中心的地理位置又越来越分散,因此要求光纤网络能够有效应对因传输距离变长而导致带宽增加的问题。然而,将信号从 A 点传输到 B 点便已消耗掉所有预算功耗,已没有足够的功耗来运行实际的 CPU 和 GPU,因此光模块很快就会遇到功耗瓶颈。在这种情况下,非重定时的线性拓扑结构便可发挥所长。与传统的基于数字信号处理(DSP)的重定时光学解决方案相比,线性可插拔光学器件(LPO)链路可显著降低模块功耗和延迟,这对于提升 AI 性能至关重要。而且,由于功耗和冷却要求有所降低,从基于 DSP 的解决方案切换到 LPO 还可显著节约成本,减少开支,但于此同时,重定时器/DSP 将不再适用,而是需要一个功能强大的高性能 ASIC 来驱动光学器件。

为了展示 Cadence IP 的稳健性,我们演示了面向 PCIe 7.0 的子系统测试芯片板能够通过外部环回模式配置的非重定时光电链路成功发送和接收 128GT/s 信号,并留有多个数量级的裕度。

图 5:ASIC 驱动线性光学器件示例

合规是关键

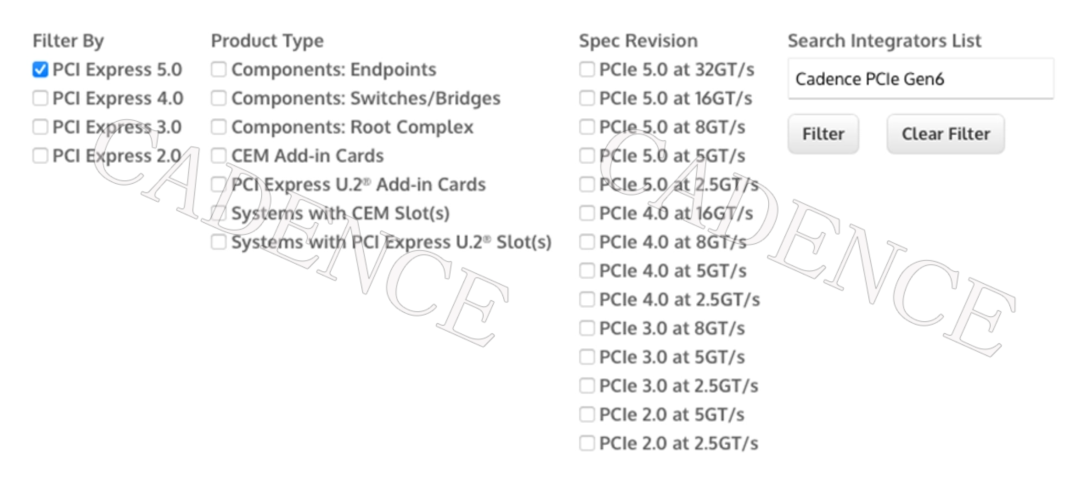

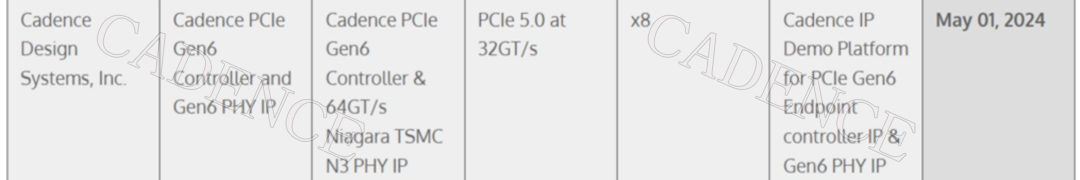

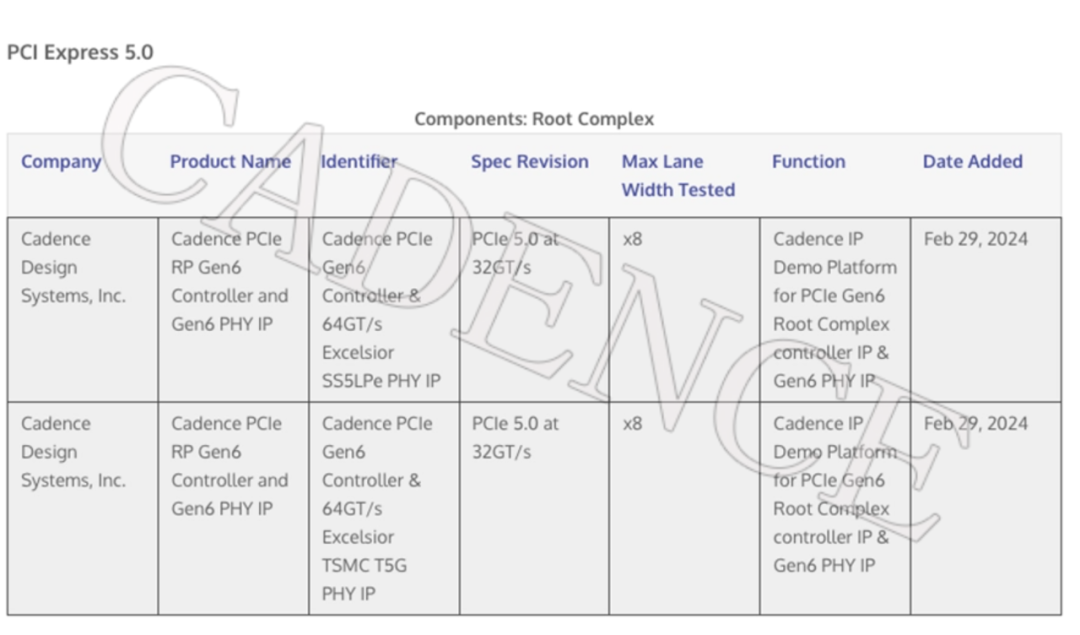

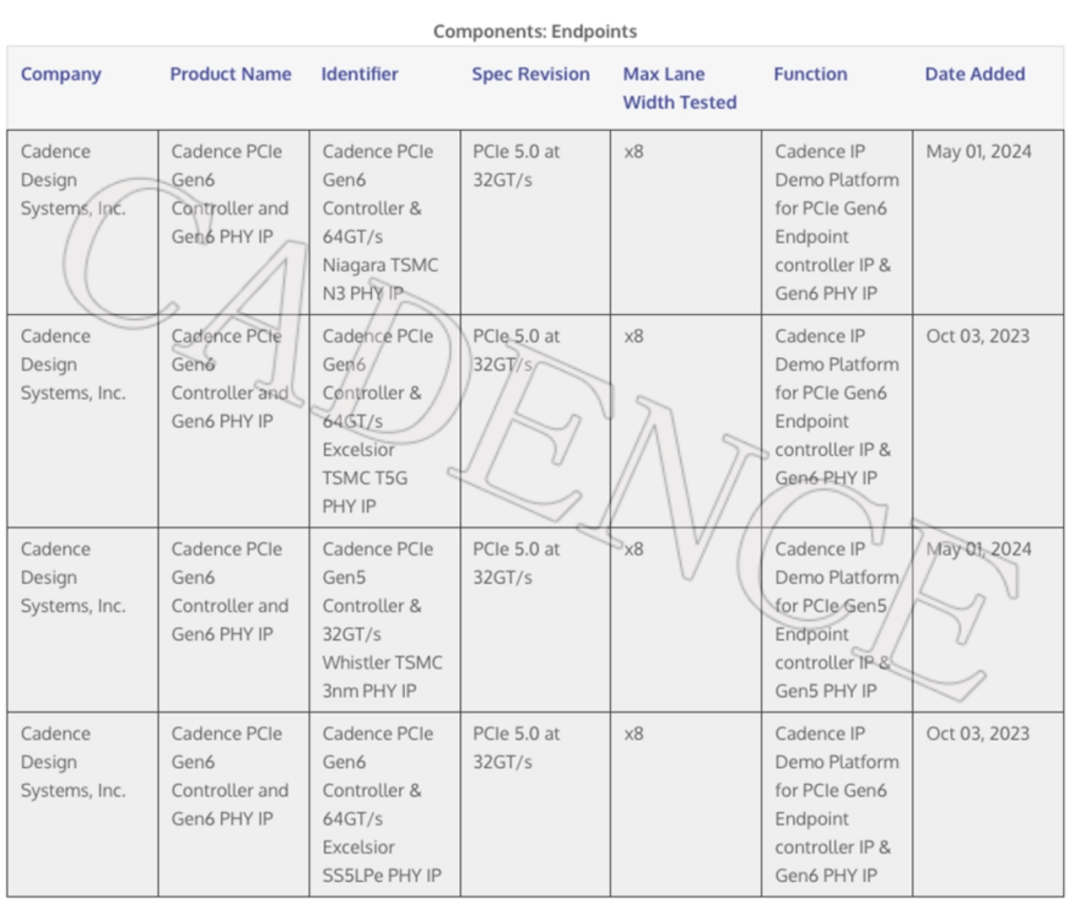

对 PCIe 6.0,目前官方合规计划尚未启动。这是 SIG 的常规做法,即在规范获批几年后启动合规计划,以便生态系统有充足的时间来准备初始产品,并让测试和设备供应商有足够的时间来启动和运行他们的硬件/软件。目前,PCIe 6.0 只能通过最高 PCIe 5.0 级别(SIG 支持的最高官方合规性测试套件)的官方认证。我们已经向 SIG 提交了针对多个工艺节点的 PCIe 6.0 IP 子系统解决方案,它们均被列为合规产品。您可以登录 pcisig.com 网站,在 Developers->Integrators 列表下查询。具体如下所示:

PCI-SIG 开发者大会的其他看点

在 6 月 12 日和 13 日举办的 PCI-SIG 开发者大会上,Cadence 进行了以下演示:

Cadence 面向 PCIe 7.0 的 IP 通过非重定时光学器件发送和接收 128GT/s 信号的强大性能

使用示波器测量 Cadence 面向 PCIe 7.0 的 IP 的功能,详细说明其稳定的电气性能和裕度

Cadence 面向 PCIe 6.0 接口的 IP 的可靠性,使用测试设备表征 PHY 接收器的质量

Cadence 面向 PCIe 6.0 的 PCI-SIG 兼容 IP 子系统,在功耗和性能方面进行了优化

作为 PCI Express 领域的领军人物,Cadence 的 Anish Mathew 了分享他对“UIO ECN 对 PCIe 控制器设计和性能的影响”这个重要话题的宝贵见解,重点介绍了 Cadence 设计团队在实现这一目标方面所取得的进展。

图 6:Cadence UIO 实现总结

总 结

Cadence 于 2023 PCI-SIG 开发者大会期间展示了 PCIe7.0-Ready IP,将继续引领 PCIe IP 的开发,面向 PCIe 7.0 提供支持先进节点的完整解决方案。预计这些解决方案将于明年初发布。Cadence 以 PCI-SIG 的成员身份为豪,将继续为市场提供包括 PHYs、控制器、软件和验证 IP 在内的完整解决方案,并大量投资于 PCIe 项目。Cadence 是首家提供面向 PCIe 3.0、4.0、5.0 和 6.0 的完整子系统解决方案的 IP 供应商,拥有业内领先的功耗、性能、面积(PPA )。我们很荣幸能够继续提供面向 PCIe 7.0 的最新 IP 子系统解决方案,为 PPA 和上市时间设定新的基准。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续十年名列美国财富杂志评选的 100 家最适合工作的公司。

-

芯片

+关注

关注

463文章

54602浏览量

470683 -

接口

+关注

关注

33文章

9633浏览量

157770 -

Cadence

+关注

关注

68文章

1039浏览量

147472 -

PCIe

+关注

关注

16文章

1497浏览量

89112

原文标题:Cadence 在 2024 PCI-SIG 开发者大会上展示完整的 PCIe 7.0 解决方案

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cadence PCB设计解决方案

CADENCE PCB设计解决方案提供完整的设计环境

Voltus-Fi定制型电源完整性解决方案

楷登电子发布PCIe 6.0规范Cadence IP

Cadence针对PCIe 6.0的完整IP解决方案

Cadence推出15种新验证 IP(VIP)解决方案

力科将推出(PCIe)完整性新协议分析和流量生成解决方案

Cadence 于 2023 PCI-SIG 开发者大会期间展示 PCIe7.0-Ready IP

Cadence展示完整的PCIe 7.0 IP解决方案

Cadence展示完整的PCIe 7.0 IP解决方案

评论