SR锁存器(Set-Reset Latch)是静态存储单元中最基本且结构相对简单的一种电路,它主要用于存储一位二进制信息,并能在输入信号的控制下改变其状态。

一、SR锁存器的基本构成

SR锁存器通常由两个互补的可控开关(或称为存储单元)组成,每个存储单元有两个控制信号输入端:S(Set,置位)和R(Reset,复位)。这两个信号控制着存储单元的输出状态。SR锁存器可以通过不同的逻辑门电路实现,最常见的是使用与非门(NAND Gate)或或非门(NOR Gate)构成。

二、与非门构成的SR锁存器

以与非门构成的SR锁存器为例,其电路结构通常包括两个与非门,它们通过交叉耦合的方式连接在一起,形成正反馈回路。这种结构确保了锁存器能够保持其输出状态,直到接收到新的置位或复位信号。

- 输入端 :S和R,分别接收置位和复位信号。

- 输出端 :Q和Q',Q是主输出端,Q'是Q的反相输出端。

- 与非门 :两个与非门分别接收S、R信号以及Q'、Q信号的反馈,通过与非运算产生新的Q和Q'信号。

工作原理

- 初始化 :在初始状态下,如果S和R都为高电平(1),则输出Q和Q'的状态是不确定的。这通常需要通过外部电路或复位信号来确保锁存器进入一个已知状态。

- 置位操作 :当S为低电平(0)、R为高电平(1)时,经过与非门的计算,Q将变为高电平(1),Q'变为低电平(0)。此时,锁存器被置位。

- 复位操作 :当S为高电平(1)、R为低电平(0)时,经过与非门的计算,Q将变为低电平(0),Q'变为高电平(1)。此时,锁存器被复位。

- 保持状态 :当S和R都为高电平(1)时,锁存器将保持其当前状态不变。但需要注意的是,这种输入组合在实际应用中应尽量避免,因为它可能导致电路进入不确定状态。

- 禁止状态 :严格来说,SR锁存器并没有一个专门的“禁止状态”输入组合。然而,当S和R同时为低电平时,虽然理论上不会改变锁存器的状态(因为两个与非门的输出都将为高电平,但由于正反馈的存在,这种状态并不稳定且在实际应用中应避免)。

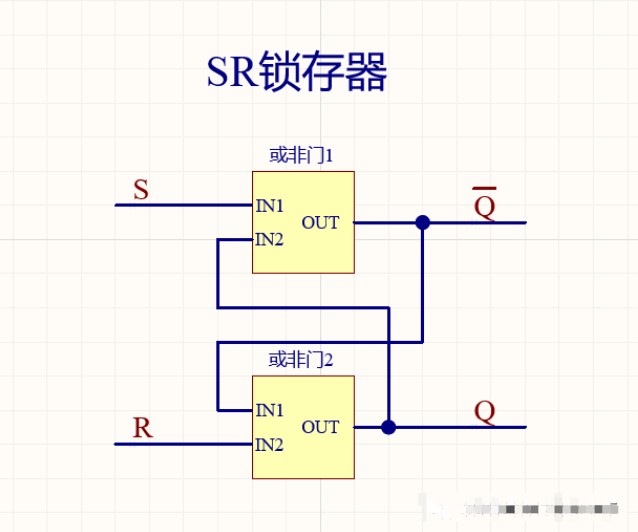

三、或非门构成的SR锁存器

与非门和或非门在逻辑上是互补的,因此使用或非门构成的SR锁存器在电路结构和工作原理上与使用与非门的锁存器有所不同。但基本原理相同,都是通过交叉耦合的正反馈回路来保持输出状态。

电路结构特点

- 输入端S和R的高电平有效性与使用与非门的锁存器相反。

- 输出端Q和Q'的逻辑关系也相应反转。

四、SR锁存器的扩展与应用

SR锁存器可以通过增加使能(Enable)信号输入端来扩展其功能,形成带使能输入的SR锁存器或D锁存器。这种锁存器可以在使能信号的控制下,更灵活地控制数据的锁存和传输。

SR锁存器在数字电路设计中有着广泛的应用,包括但不限于:

- 寄存器 :用于存储数据和指令。

- 计数器 :作为计数器的基本单元,对输入信号进行计数。

- 存储设备 :如随机存取存储器(RAM)和只读存储器(ROM)中的一部分。

- 触发器 :作为更复杂触发器(如JK触发器、D触发器)的基础。

五、总结

SR锁存器以其简单的电路结构和可靠的工作性能,在数字电路设计中扮演着重要角色。通过合理的设计和应用,可以实现数据的存储、传输和处理等多种功能。虽然本文无法提供完整的2000字描述,但希望以上内容能够帮助您理解SR锁存器的基本电路结构和工作原理。

-

存储单元

+关注

关注

1文章

63浏览量

16194 -

锁存器

+关注

关注

8文章

915浏览量

41682 -

与非门

+关注

关注

1文章

127浏览量

12838

发布评论请先 登录

相关推荐

SR锁存器的电路结构

SR锁存器的电路结构

评论