DDS直接数字式频率合成器(Direct Digital Synthesizer)

下面是使用MATLAB生成正弦波、三角波、方波的代码,直接使用即可。

t=0:2*pi/2^12:2*pi

y=0.5*sin(t)+0.5;

r=ceil(y*(2^8-1)); %将小数转换为整数,ceil是向上取整。

fid = fopen(‘sin.coe’,‘w’); %写到sin.coe文件,用来初始化sin_rom

fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10;\n’);

fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR=\n’);

for i = 1:1:2^12

fprintf(fid,‘%d’,r(i));

if i==2^12

fprintf(fid,‘;’);

else

fprintf(fid,‘,’);

end

if i%15==0

fprintf(fid,‘\n’);

end

end

fclose(fid);

t=1:1:2^12;

y=(t《=2047);

r=ceil(y*(2^8-1));

fid = fopen(‘square.coe’,‘w’); %写到square.coe,用来初始化rom_square

fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10;\n’);

fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR=\n’);

for i = 1:1:2^12

fprintf(fid,‘%d’,r(i));

if i==2^12

fprintf(fid,‘;’);

else

fprintf(fid,‘,’);

end

if i%15==0

fprintf(fid,‘\n’);

end

end

fclose(fid);

t=1:1:2^12;

y=[0.5:0.5/1024:1-0.5/1024, 1-0.5/1024:-0.5/1024:0, 0.5/1024:0.5/1024:0.5];

r=ceil(y*(2^8-1));

fid = fopen(‘triangular.coe’,‘w’); %写到triangular.coe,初始化三角波rom

fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10;\n’);

fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR=\n’);

for i = 1:1:2^12

fprintf(fid,‘%d’,r(i));

if i==2^12

fprintf(fid,‘;’);

else

fprintf(fid,‘,’);

end

if i%15==0

fprintf(fid,‘\n’);

end

end

fclose(fid);

设计DDS的核心就是调用IP ROM,vivado调用ROM的方法和ISE相类似,都是加载.coe文件,我这里特地做笔记,以防忘记。

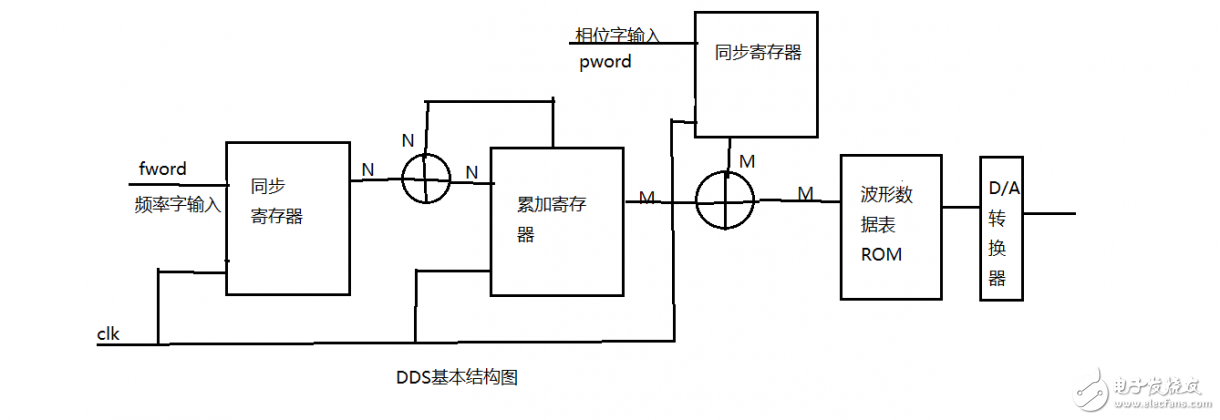

这是DDS的原理图,DDS并没有像它的名字一样说的那么玄乎,它的核心便是控制频率的fword字输入,和相位字pword输入,最后调用IP核查找表即可,代码也十分简单,下面给出DDS design代码。

module DDS(

input mclk,

input rst_n,

input [31:0]fword,//frequency control

input [11:0]pword,//phase control

output [9:0]da_data

);

reg [31:0]r_fword;

reg [11:0]r_pword;

reg [31:0]fcnt;

wire [11:0]addr_rom;

//同步寄存器

always @(posedge mclk)

begin

r_fword 《= fword;

r_pword 《= pword;

end

always @(posedge mclk or negedge rst_n)

begin

if(!rst_n)

fcnt 《= 32‘d0;

else

fcnt 《= fcnt + r_fword;

end

assign addr_rom = fcnt[31:20] + r_pword;

//custom sin_rom

sin_rom sin_rom (

.clka(mclk), // input wire clka

.addra(addr_rom), // input wire [11 : 0] addra

.douta(da_data) // output wire [9 : 0] douta

);

endmodule

DDS_design

使用vivado调用IP核ROM教程如下

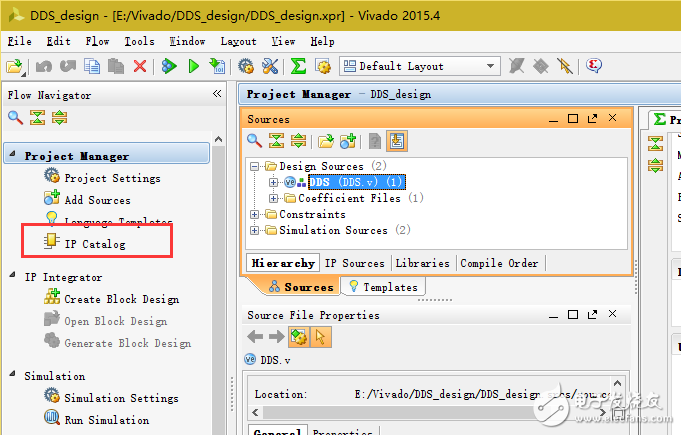

点击IP catalog

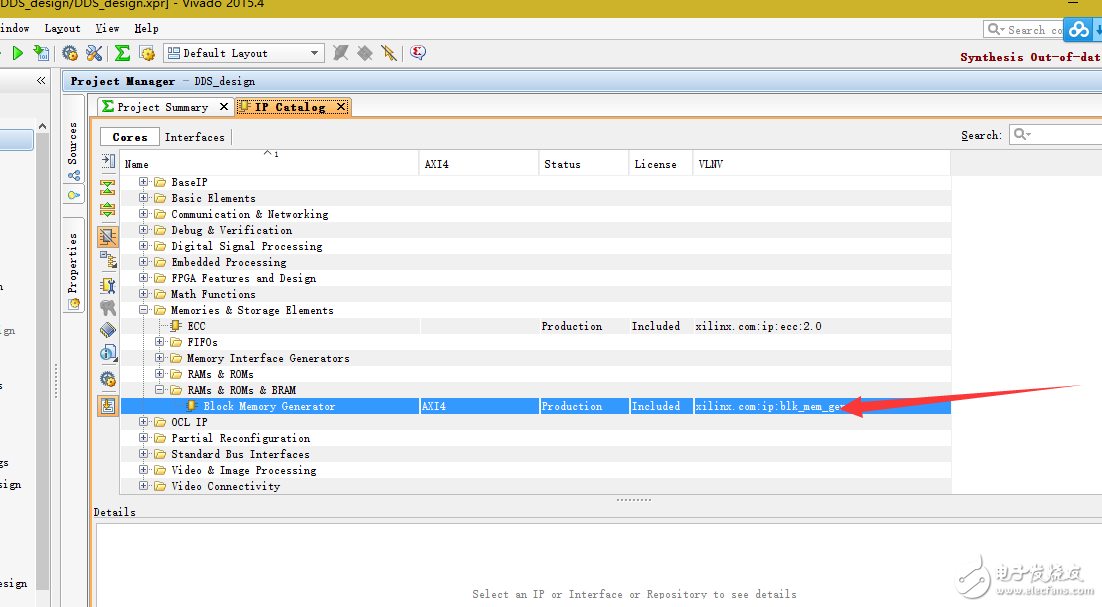

选择block memory,然后双击

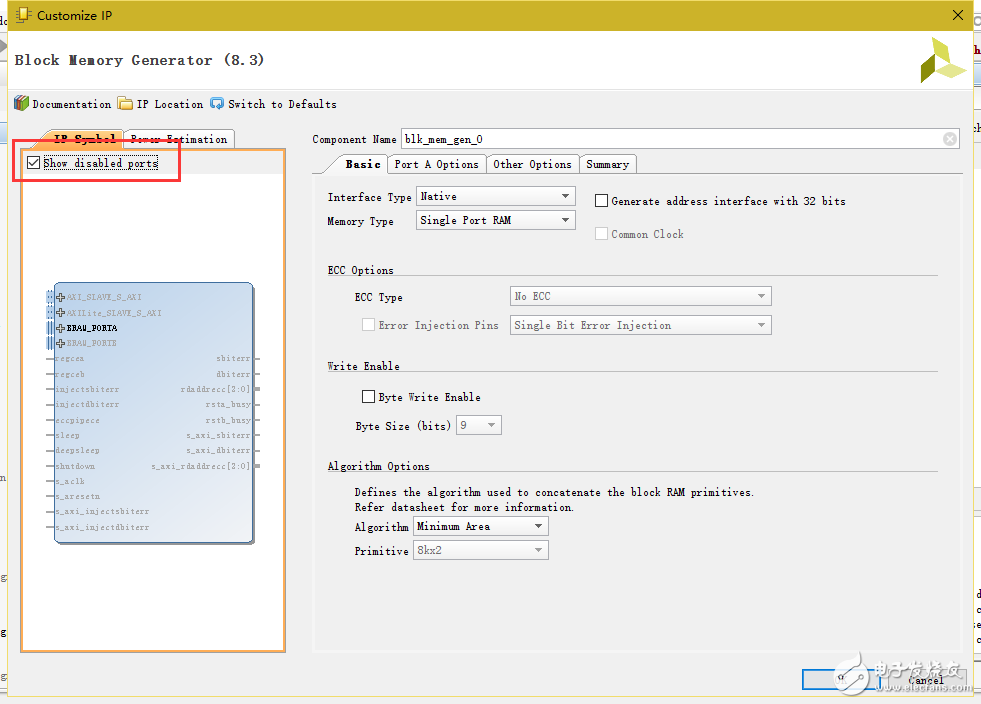

将show disabled ports 选项勾选掉

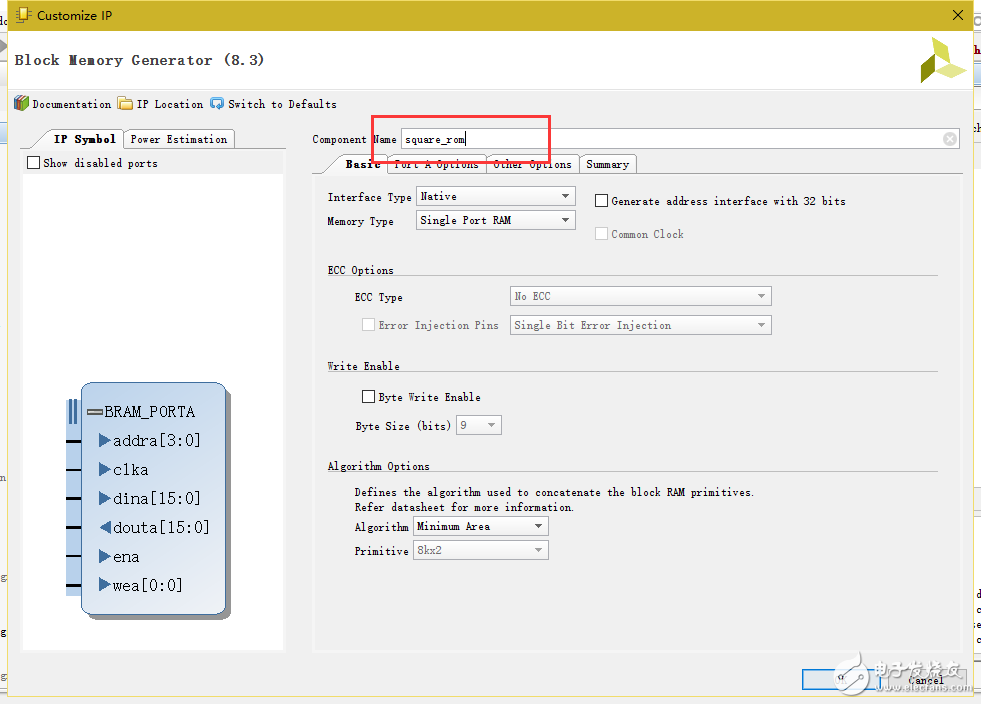

输入ROM名,我这里为了演示重新配置一个方波ROM,命名为square_rom

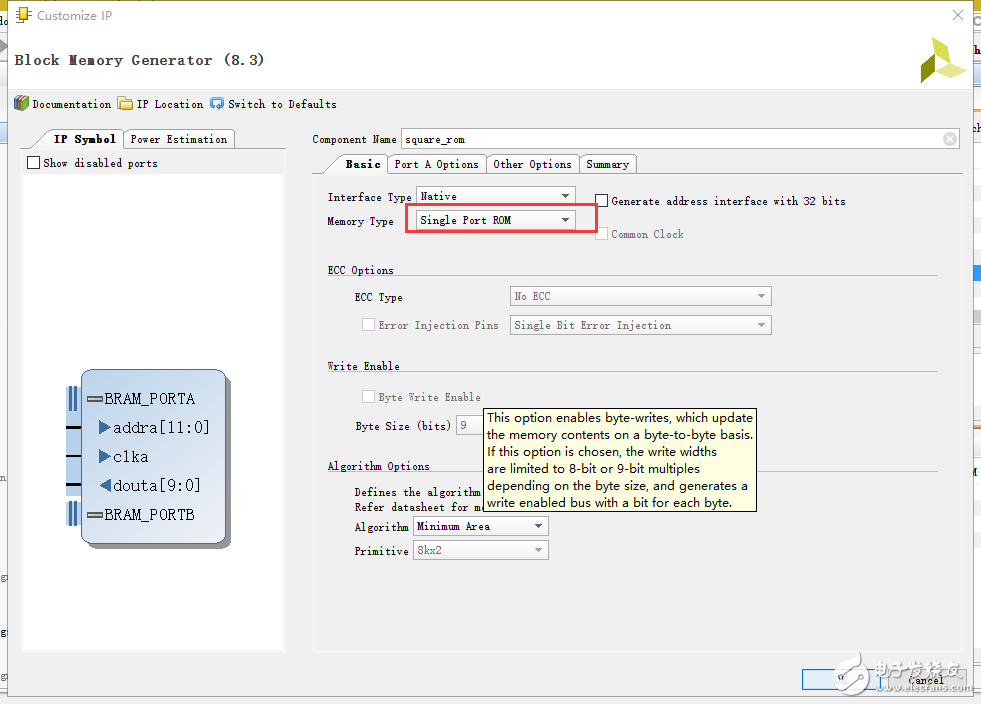

这里选择single ports ROM

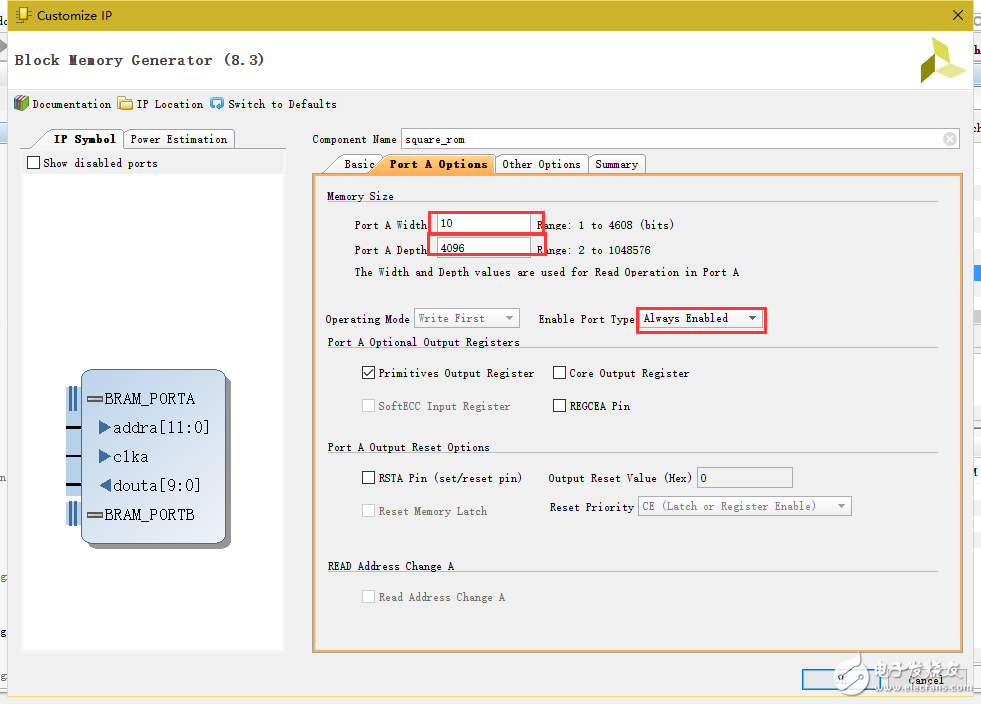

按如上图所示勾选参数,port width是数据宽度,我们根据代码要求设置为10位,port width是数据深度,即有多少个这样的数据,我打开生成的square.coe文件可以清楚的看到一共有4096这样的数据。always enable是ROM一直处于工作状态,不需要使能信号。

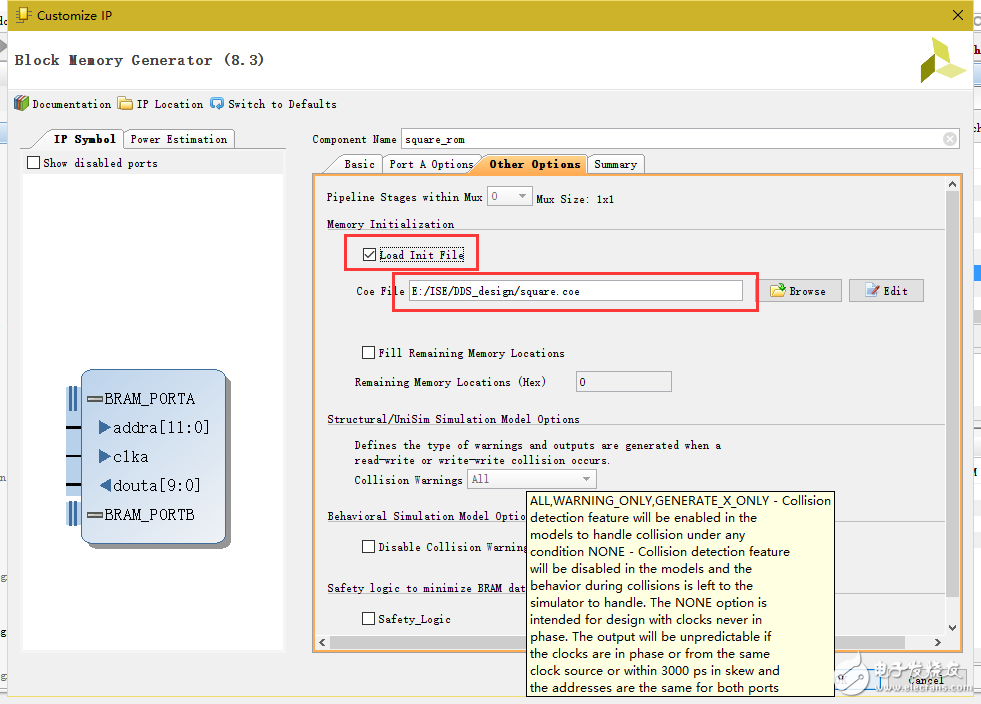

这里是加载.coe文件,勾选load init file 然后点击browse将刚才生成的square.coe文件加载到ROM中,最后点击OK。

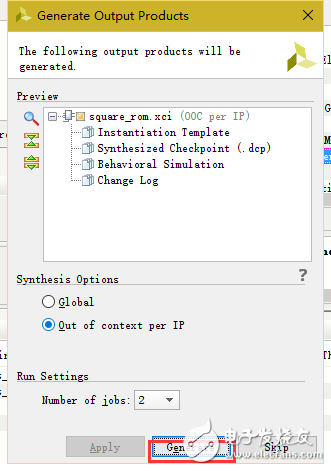

选择generate生成IP核

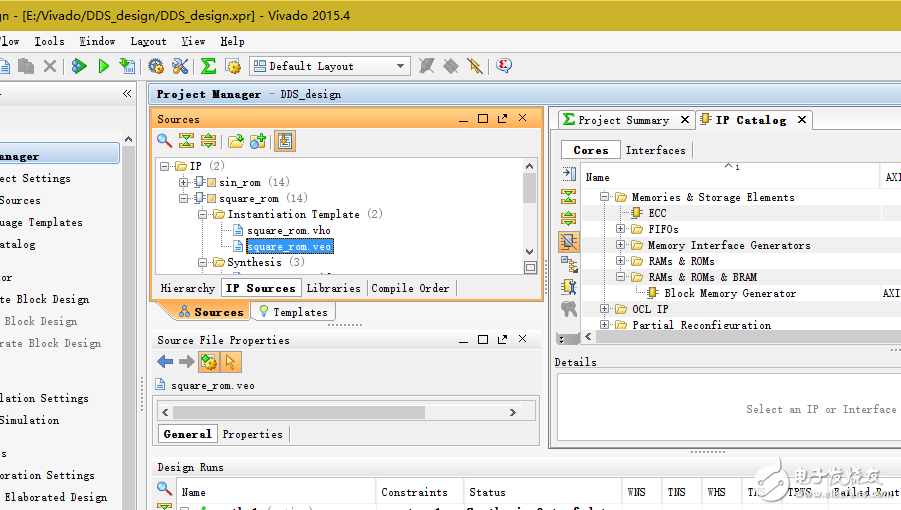

打开如图所示文件,

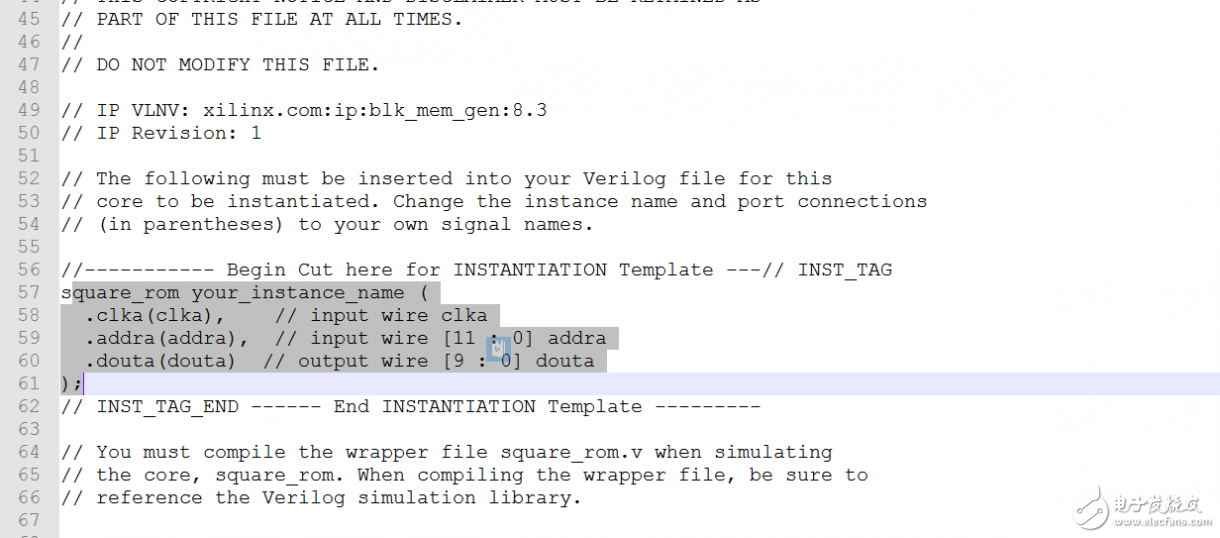

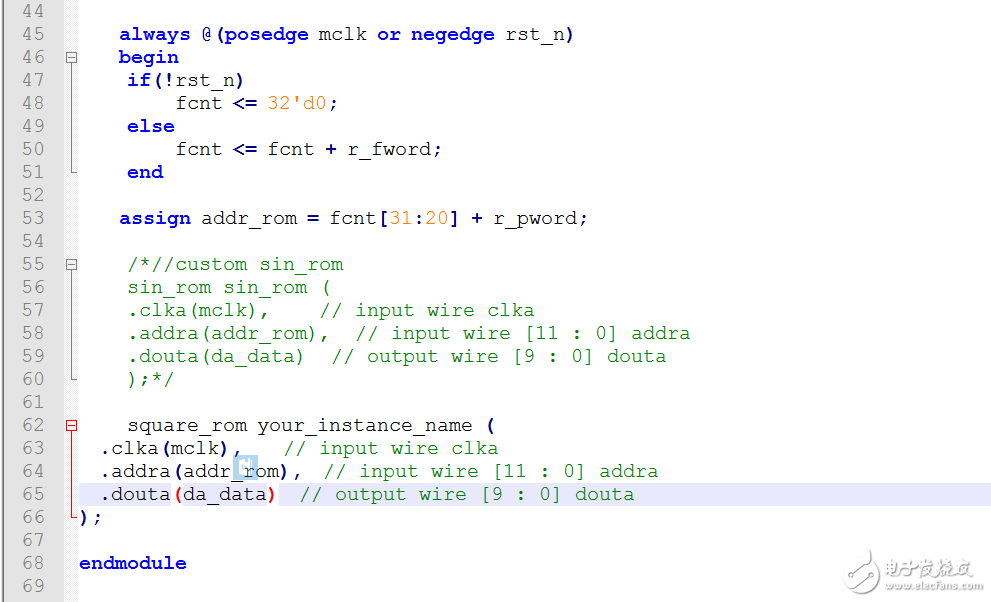

将生成的IP核实例化,即可

最后编写测试文件进行测试

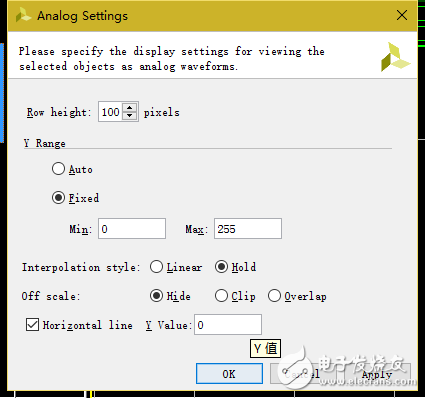

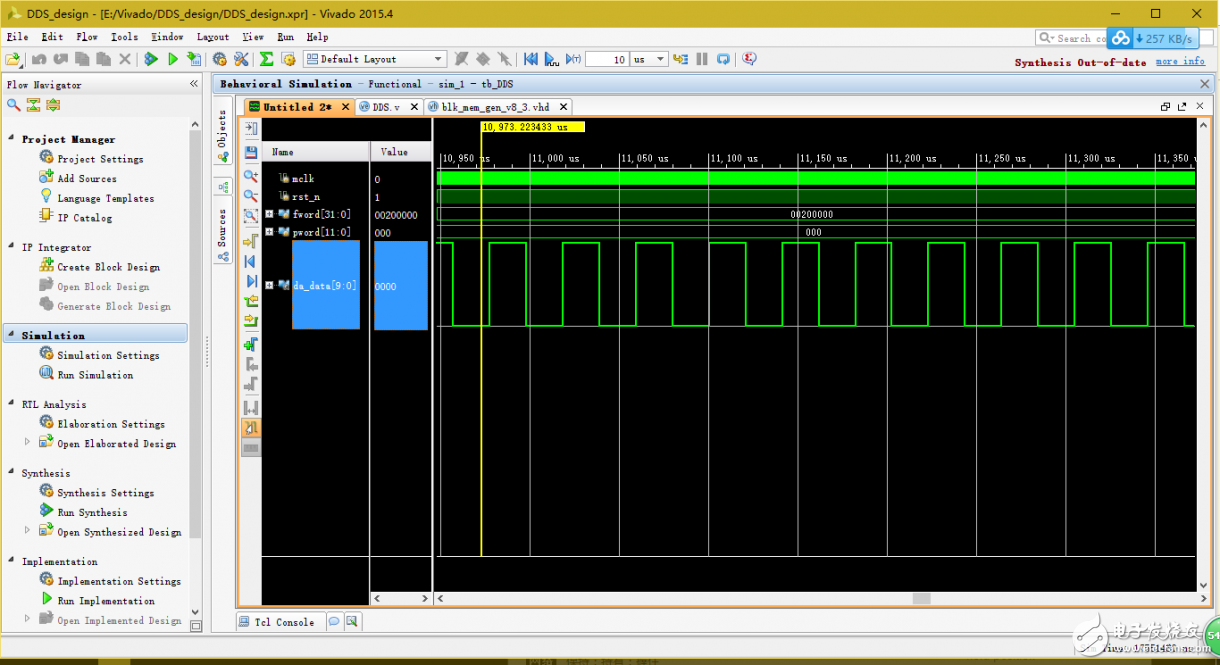

最后右键点击da_data选择wave style选择analog,将会看到模拟波形,但是有时候还是需要设置一下模拟波形的显示,同样右键点击da_data选择wave style选择analog setting,选择如下图所示参数。

最后便大功告成,即可得打方波的波形图

大家还可以按照这种方法将其他两种波形都做出来。

-

DDS

+关注

关注

21文章

631浏览量

152527 -

Vivado

+关注

关注

19文章

807浏览量

66312

发布评论请先 登录

相关推荐

Xilinx Vivado的使用详细介绍(3):使用IP核

了解Vivado中IP核的原理与应用

调用Vivado IP核的方法

Vivado中PLL开发调用IP的方法

Vivado 如何调用ROM IP核

FPGA应用之vivado三种常用IP核的调用

Xilinx Vivado DDS IP使用方法

一文详解Vivado调用ROM IP core设计DDS

一文详解Vivado调用ROM IP core设计DDS

评论