介绍

半导体行业不断演变,旨在满足用户对移动设备和数字家庭等领域中每一代新产品的多方面需求,包括更多功能、性能、电池寿命和更低成本。半导体工艺技术的演进遵循摩尔定律,这是这些产品得以上市的主要促成因素。对整个行业来说,从基于大体积平面晶体管向FinFET三维晶体管的过渡是一个重要里程碑。这一过渡促使工艺技术经过了几代的持续演进,并且减小了外形尺寸,提高了速度,同时减少了泄漏。

过去,最先在先进的工艺技术中部署的绝大多数产品都采用以数字为中心的数据处理方式,而模拟处理方式则保留给更保守的工艺技术使用。设计人员选择利用保守工艺中对模拟方式更加友好的特征,并且错误地认为模拟块区域在先进的工艺技术中无法扩展,或者价格昂贵。

对于每个连接拥有超过10 Gbps数据吞吐量的无线连接和大量设备连接(1000亿个链路),这些连接都需要更复杂的数字信号处理。因此,设计人员应考虑FinFET技术在高性能、低功耗和小体积方面的优势。如果大部分模拟功能集成到单独的晶片中,例如RF芯片,则它需要数据转换器 – 模拟数字 (ADC) 和数字模拟 (DAC) 转换器 – 作为外部模拟处理功能和内部数字处理块之间的接口。这些数据转换器一般集成到数字芯片系统 (SoC) 中,以消除对传统高耗电数字接口的需求。因此,在FinFET工艺中部署数据转换器非常重要。本文介绍设计人员如何采用针对FinFET工艺的IP而克服数据转换器设计的挑战。

针对数据转换器设计的FinFET工艺

尽管在FinFET工艺中设计数据转换器和其他模拟功能存在挑战,但将这些功能集成到FinFET工艺的SoC中也有一些关键的优点:

使更多功能集成到同一个SoC中的趋势继续

通过将模拟和数字功能密切集成到同一个SoC中降低功耗

消除对高耗电芯片间数字接口的需求

模拟功能设计人员也可以从FinFET工艺的特征中受益:

通过使用最少的特性而减小体积(线路、晶体管等):丰富且低价的区域和高速数字门有助于实施数字辅助型模拟功能,以提高可靠性,并减少IP体积和功耗(例如,通过数字校准)

更好的通道控制:3D门增强了控制设备门的能力,并且改善了晶体管的总体特征,无论是作为交换机还是作为模拟放大器设备运行

更快的设备:由于采用具有高传输频率 (Ft) 的晶体管,高速工艺消除了需要极高带宽或高速度的模拟功能的某些设计限制

降低设备可变性:更好的设备匹配特征简化了模拟设计,并减小了体积

FinFET设计流程中的布局和示意图

FinFET工艺的特定特征使得为平面CMOS设计而定义的传统设计流程效率低下。模拟功能设计人员必须特征所用的方法,将以下特征考虑在内:

FinFET晶体管体积的离散量化

电气特征对布局寄生现象的高度依赖

金属线路的更高电阻率和更高寄生电容

对匹配的结构的双重模式影响

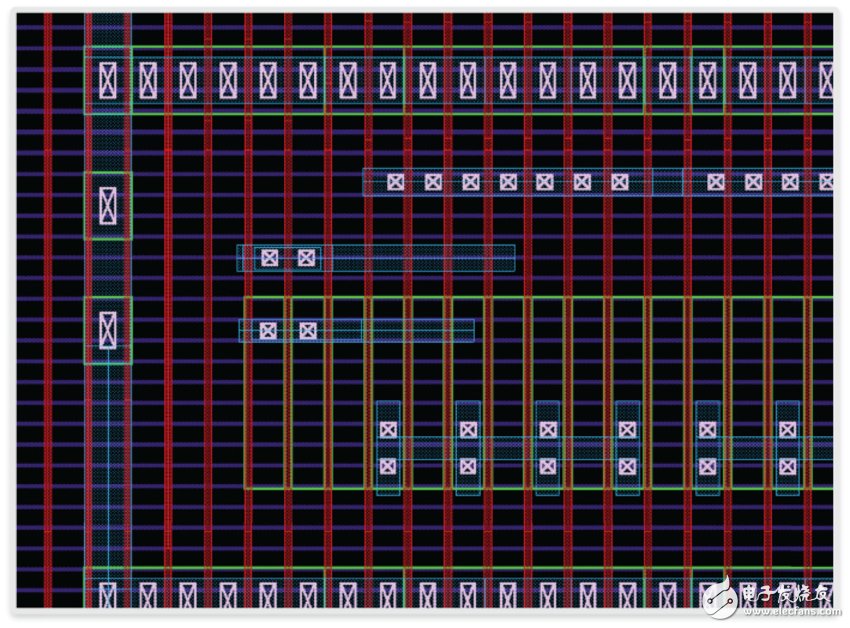

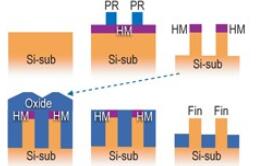

通过对定期测量的FinFET设备进行并行和串行组合而实现几乎任何有效的设备宽度/长度,FinFET工艺的某些复杂特征(例如鳍片宽度的有限粒度)可得到有效的管理。因此,设计人员能够以稍高的抽象化进行设计(有效的设备),以降低电气设计的复杂度。图1显示了定期测量的FinFET的布局,其中,在与绿色长方形重叠的区域(活动区域),各个晶体管是垂直红线(多晶硅)和水平蓝线(鳍片)的交叉点。

图1:常规FinFET布局示意图

然而,电迁移、更高的负偏压温度不稳定性(NBTI)和正偏压温度不稳定性(PBTI) 导致的老化效应迫使设计人员假设更高的设计余量,有时要以牺牲体积或性能为代价。

布局寄生结构上设备电气特征的复杂依赖关系导致电路行为对物理布局的极高依赖。这意味着在转到布局之前需要对最终电路原理图进行验证的传统模拟设计流程效率很低。布局寄生效应无法通过设计的少量调整而轻松恢复,而是有可能需要对电路进行完整的重新设计。

更高效的流程依赖电路物理布局的创建,这要在设计过程的早期进行,这样,电路的所有迭代都基于后批注结果。

FinFET技术的物理设计规则比前几代技术有更大的局限性。完成无误的布局需要更多次迭代,并且比前几代工艺需要的时间长得多。然而,通过在最初设计阶段认识到:严格遵守所有规则进行布局迭代并不是评估对性能的寄生效应的必然要求,前提是布局与示意图匹配。图2显示了FinFET工艺中12位高速ADC的布局例子。

图2:FinFET布局举例:12位高速ADC

金属堆叠与颜色

双模式是FinFET工艺的关键优势,因为它在设备层面和金属配线层面实现了更精细的形状间距,同时具有基本相同的间距。

对于大多数模拟设计,CAD工具和设计规则允许设计人员忽略双重模式,因为设计工具将自动对设计进行颜色标记(选择将两个模式/掩码中的哪一个用于每种形状)。然而,模拟设计中存在匹配关键结构,如金属-氧化物-金属 (MOM) 电容,或者存在关键信号跟踪路径,在这些路径中,匹配特征可能受到采用其他方式匹配的布局中不均匀的颜色选择影响。在这些情况下,设计人员可以实施平衡的配色,以确保最佳的匹配。图3显示了带有扭曲手指结构的MOM电容的例子,这种结构的原因是高级工艺中的每个金属层采用不同的设计网格。出于匹配目的,每个电容中相应的手指应组合到同一个掩码中(颜色)。

图3:FinFET中的MOM电容布局举例

这些考量尤其与依赖交换电容架构而实现模拟功能的设计相关,例如模拟数字转换器。类似的考量也适用于电流源间准确匹配是设备性能关键的电路,例如电流或电压控制DAC。

高密度配线作为减小间距的副作用,是金属线的电阻,并且大大提高了侧边寄生电容。在某些模拟设计中,关键路径或装置的自导噪音和关键节点上的总负荷(包括寄生)可严重影响电路性能。在某些情况下,这可能完全消除更先进的工艺的速度优势,影响系统性能和功耗。副作用必须及早评估,而且每个设计阶段都必须根据 (RCC) 布局抽象而进行模拟。

结束语

在FinFET技术中,数据转换器和其他模拟IP块的成功开发要求设计人员部署优化的设计方法论,这样才能充分利用该工艺的高速、低功耗和小提交的优点。28nm平面CMOS设计中经过验证的方法论不再适用,因为这些方法论导致设计速度超慢,而且需要经过太多次的设计迭代,最终导致性能和良品率不佳。Synopsys的DesignWare® Data Converters IP系列支持迁移技术从平面CMOS向FinFET迁移。该IP系列可帮助设计人员满足模拟前端接口要求,同时降低物料成本,最大限度减少集成限制因素,例如配线和凸点转移。12位高速DesignWare ADC基于SAR的架构提供了320 MSPS的数据速率,并且提供了并行装配选项,从而减小体积,降低功耗,并提高架构的可扩展性。12位 DAC以 针对高信号带宽的640 MSPS速率实现了低功耗。Synopsys全面的数据转换器IP已经集成到大量工艺的300多个SoC中,帮助设计人员降低集成风险,并加快产品上市速度。

-

IP

+关注

关注

5文章

1888浏览量

156861 -

数据转换器

+关注

关注

1文章

402浏览量

30776

发布评论请先 登录

将数据转换器IP集成到系统芯片简化设计技术

详解先进的半导体工艺之FinFET

FinFET工艺的IP克服数据转换器设计详解

FinFET工艺的IP克服数据转换器设计详解

评论