1 PCB(印刷电路板)

由于技术原因,最好使用多层PCB的单独一层专用于接地(VSS),另一层专用于VDD供电。这提供了不错的去耦和屏蔽效果。对于很多应用,由于经济原因不能使用此类板。在这种情况下,主要要求就是要确保接地和供电有良好的结构。2 元件位置 PCB的初始布局必须将电路分为不同模块: • 高电流电路 • 低电压电路 • 数字元件电路 • 根据电路的EMI影响分离电路,以降低因 PCB 上的交叉耦合产生的噪音 3 接地和供电 必须遵守与接地相关的以下规则: • 使每个块(噪声、低电平敏感、数字或其他)单独接地。• 将所有接地返回为一个点。 • 避免出现环路(或确保其具有最小面积)。为提高模拟性能,用户必须对VDD和VDDA使用单独的电源,将去耦电容放置在离器件尽可能近的位置。供电(VSS、VDD、VSSA、VDDA、VDDUSB、VDDIO2或 VDDSMPS)必须靠近地线实现,以最小化供电环的面积。这是因为供电环起到了天线及EM主发收的作用。所有无元件的PCB区域都必须填充额外的接地,以创造屏蔽环境(尤其是当使用单层PCB时)。 4 去耦 所有供电和接地引脚都必须适当连至供电电源。这些连接(包括焊盘、线和过孔)都必须有尽可能低的阻抗。典型情况下,这可通过使用粗的线宽做到,最好在多层PCB中使用专用供电层。此外,每个供电电源对都必须使用滤波陶瓷电容(100nF)及约10µF 的钽电容或陶瓷电容去耦,两个电容并联在器件上。在某些封装中,多个VDD引脚使用同一个VSS引脚,而不是一对电源引脚(每个VDD对应一个VSS)。这种情况下,电容必须处于每个VDD引脚和公共VSS引脚之间。这些电容必须放置在PCB 尽可能接近适当引脚的位置,或在这些引脚下面 PCB 的底层。其典型值为10至100nF,但准确值取决于应用需要。

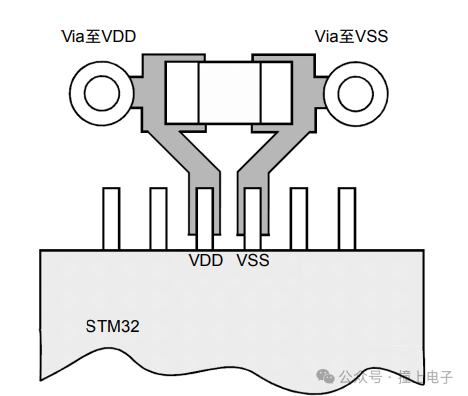

下图显示了这种VDD/VSS引脚对的典型布局。

5 其它信号 当设计应用时,可通过仔细研究以下几点来提高EMC性能:• 临时扰动会永久影响运行过程的信号(中断和握手选通信号就是这个情况,但LED指令不是这个情况)对于这些信号,可使用周围接地跟踪、更短的长度、无噪声、附近敏感跟踪(串扰影响)提高EMC性能。对于数字信号,两个逻辑状态必须达到可能的最佳电气边界。建议使用慢速施密特触发器消除寄生状态。• 噪声信号(例如:时钟) • 敏感信号(例如:高阻) 6 不使用的 I/O 和特性 所有微控制器都是为多种应用设计的,通常一个应用不会使用100 %的MCU资源。为了提高EMC性能和避免额外功耗,器件不使用的功能必须禁用且与时钟树断开连接,如下:• 不使用的时钟源必须禁用。• 不使用的I/O不得浮空。• 不使用的I/O引脚必须由软件配置为模拟输入,且必须通过外部或内部上拉或下拉连接到固定逻辑电平0或1,或使用软件配置为输出模式。

-

印刷电路板

+关注

关注

4文章

770浏览量

35085 -

STM32

+关注

关注

2265文章

10859浏览量

354546 -

硬件设计

+关注

关注

18文章

394浏览量

44523

发布评论请先 登录

相关推荐

专家建议:如何灵活进行软硬件协同开发

stm32硬件介绍 stm32硬件设计

STM32最小系统硬件解析

STM32F1x HAL库学习笔记(12)硬件 SPI 的配置

STM32硬件设计的建议(1)

STM32硬件设计的建议(1)

评论