在FPGA开发中,当我们写完代码,进行仿真,确定设计没有问题后,下载到硬件上一般都能按照我们的设计意愿执行相应功能。但这也并非绝对的,有时候你会遇到一些突然情况,比如时序问题或者仿真时我没有考虑到某种情况,但实际中它确实存在的,这就会造成功能上的错误了。也有时候你的设计似乎你没法进行仿真或者做起来很费劲,比如设计一个SDRAM或者DDR控制器,让你相应写一个SDRAM或者DDR之类的模型进行仿真,这时候是不是就很为难了哈哈。

所以在很多时候,一个FPGA工程师应该学会使用在线调试工具进行分析。我没法写一个DDR模型,我还不能采集它的时序进行修改,直到满足要求吗?这里给大家介绍Xilinx公司的开发软件Vivado上的在线调试工具——ILA。Vivado中对ILA的使用非常灵活,操作也很方便,这里先介绍做常用的调试方式,即使用ILA核。

1. ILA核如何调用

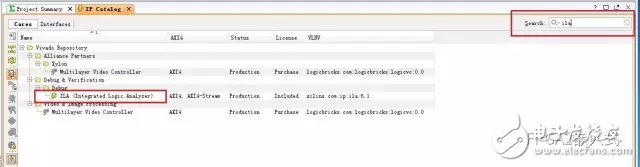

ILA核,也可以当做是一个IP核。他可以把用户指定的信号存入RAM中,然后读取出来,用于查看分析。如下图所示,在Vivado中,左边栏有一个“IP Catalog”,双击这个选项就可以进行IP选择了。

此时会弹出一个IP核选择界面,在右上角方框里输入“ila”,接着ILA核便会出现,我们只需双击即可。

2. ILA核如何配置

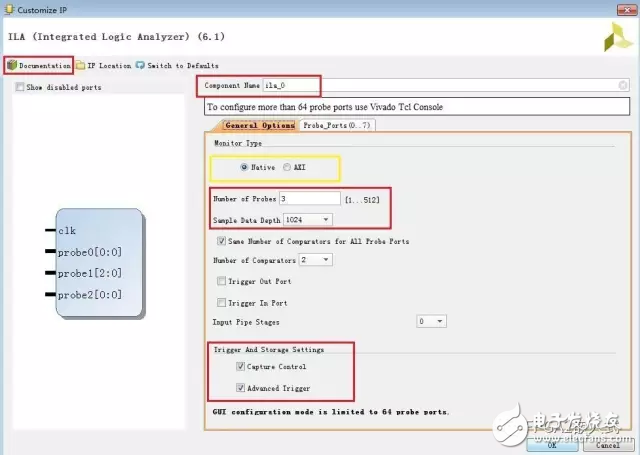

接下来便会看到ILA核的真面目了,它的帮助文档,在左上角的“Documentation”看到没,这个可以链接到IP核的data_sheet,如果对IP核的使用不是很懂可以点击此处获取IP核的详细信息。下面我们介绍最经常的使用。

图中最上面的“Component Name”可以给IP核取一个名字,注意,必须IP核名与代码中的IP名一致,才能关联起来,而且一旦生成了IP核,就算打开IP核,也不能再更改这个IP核的名字了,所以取名需谨慎。

黄色框里是输入信号的格式,如何你是AXI总线,就可以选择“AXI”,如果不是就选“Native”。

“Number of Probes”是要采集的信号数量,如果要采集5个信号就在方框里输入5即可。

“Sample Data Depth”是采样深度,深度越大意味着能看到的信息量越多。但是要切记一点,采样的数据都是要存储在芯片内的RAM里,所以选择越大占用的资源就越多,用户要根据自己芯片的情况选择采样深度。另外,因为使用了RAM,所以也会对布局布线产生影响,使用越多对时序可能影响越大,应该根据实际情况选择。

“Trigger Out Port”和“Trigger In Port”是用于触发,可以不选,触发在后面调试时可以灵活使用。

“Trigger And Strorage Setting”是数据捕获的设计,一般直接勾上即可。

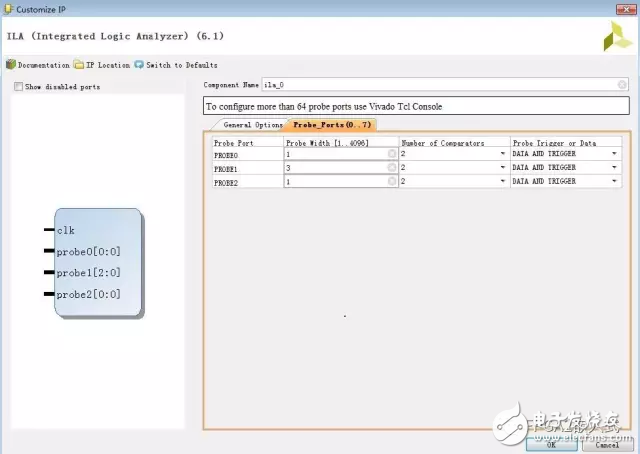

“Probe_Ports”这个页面就比较简单了,在“Number of Probes”中用户设置了多少个采样数量,这里就会有多少个通道。如前面所示,我们设置了3,这里就出现了3个通道。

“Probe_Width”数据宽度,有多少位就填多少,像“PROBE1”通道是一个3Bit的数据,就填3.其他的默认即可。

最后点击“OK”就行了,等待ILA核的生成就行了,是不是很简单哈哈。

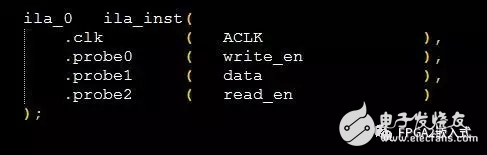

当然,我们的代码也必须有这个核的定义才行,如下图所示,这样才是一个完整的ILA核设计。

3. 总结

通过ILA核的使用,可以快速的帮助我们调试bug。另外,还有一个非常有用的VIO核,他就是虚拟输入输出IO,可以用来改变PL端的输入信号的值,观测输出的值,至于ILA的使用VIO的介绍和使用以后再讲。

-

Xilinx

+关注

关注

71文章

2167浏览量

121611 -

Vivado

+关注

关注

19文章

812浏览量

66631

发布评论请先 登录

相关推荐

开发软件

Vivado+FPGA:如何使用Debug Cores(ILA)在线调试

介绍一下xilinx的开发软件vivado的仿真模式

Xilinx公司的开发软件Vivado上的在线调试工具——ILA

FPGA开发要懂得使用硬件分析仪调试——ILA

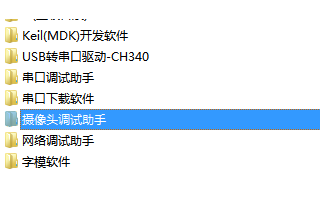

Keil开发软件和六种实用工具免费下载

Xilinx公司的开发软件Vivado上的在线调试工具——ILA

Xilinx公司的开发软件Vivado上的在线调试工具——ILA

评论