一位客户向我们提出了一个想法,希望我们设计一种解决方案,用于监测无线通信信号的频谱,以确保系统安全,即检测频谱中的意外活动。意外活动可以在任何频率、任何时间、使用任何通信协议发生。考虑到当今的技术,这些要求意味着要以高分辨率监测多个千兆赫的频率范围。尽管设置极具挑战性,但这项工作与我们的目标不谋而合。

面临的挑战

作为概念验证,客户要求系统以低于50 kHz的分辨率持续监控4.096 GHz带宽。能够以这种速度处理信号的硬件平台并不多,即使是现代ASIC也面临巨大挑战。考虑到这一点,我们选择了AMD的最新产品之一,即其Zynq UltraScale+ RFSoC器件。

解决方案

我们的团队在一台设备上安装了完整的概念验证系统--既有用于生成测试信号的信号发射器,也有用于计算频谱的信号接收器。FFT大小必须很大,每个时钟周期处理8个采样点:131'072个点,分辨率为31.25kHz,满足<50 kHz的分辨率要求。为此,需要进行大量优化,以最大限度地减少FPGA资源:使用线性插值来减少LUT大小,利用函数对称性来减少LUT大小,在多个位置之间共享LUT输出等。时钟频率为512MHz,以处理GHz信号。BRAM和URAM的使用率非常高,这使得围绕BRAM/URAM的时序闭合具有挑战性。另一个挑战是数据缩减。原始频谱数据(+ 元数据)每个采样64位,速度为4.096 GS/s(512MHz时钟上的512位总线速度为262.144 Gbps)。由于任何CPU都无法处理如此大的数据量,客户提供了一种算法来丢弃他们不需要的数据。

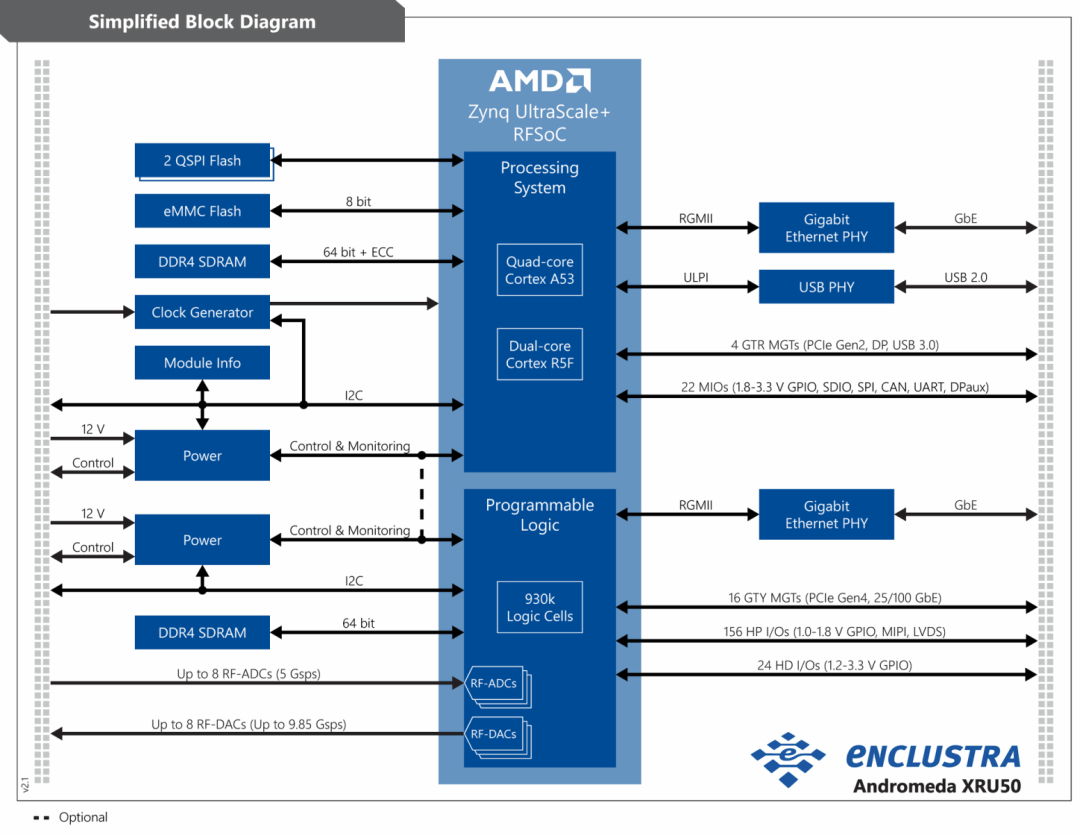

仙女座Andromeda XRU50核心板

仙女座Andromeda XRU50结构框图

成果

在AMD Zynq UltraScale+ RFSoC器件上实现了4.096 GS/s复杂信号(相当于 8.192 GS/s 真实信号)监测概念验证,时钟频率为512MHz。系统包括单个器件上的发射器和接收器,这就要求对资源使用进行复杂的优化。实现的信号监测分辨率为31.25kHz,远远低于最初的要求。

瑞苏盈科

Enclustra(瑞苏盈科)是FPGA领域全球一流的公司, 2004年成立于瑞士并成为AMD官方合作伙伴,同时是Altera FPGA金牌方案商、Microchip官方方案商。提供FPGA核心板/开发板、FPGA IP核、全栈设计服务。目前有来自29个国家的员工在全球70+国家服务1600+客户。其中不乏西门子、博世、罗氏、保时捷、ABB、舍弗勒、英飞凌等顶级企业。

如果您正在寻找具有丰富成功经验的FPGA产品和服务供应商、如果您希望打造一款成功的产品以增加您的市场份额,我们期待与您合作!

-

FPGA

+关注

关注

1634文章

21830浏览量

608035 -

带宽

+关注

关注

3文章

965浏览量

41222 -

无线通信

+关注

关注

58文章

4632浏览量

144216 -

瑞苏盈科

+关注

关注

0文章

22浏览量

10121

发布评论请先 登录

相关推荐

外差式频谱仪的技术原理和应用场景

PLC无线通信模块的工作原理 PLC无线通信模块网络配置

频谱分析仪在无线通信中的应用

电子耦合在无线通信中的应用

无线通信测试平台的技术原理和应用场景

瑞苏盈科打造基于工业标准SOM的人工智能

无线通信 | 瑞苏盈科FPGA应用于带宽(4.096 GS/s)信号的频谱监测

无线通信 | 瑞苏盈科FPGA应用于带宽(4.096 GS/s)信号的频谱监测

评论