【LLC众筹】张飞60小时精通半桥LLC谐振电源设计教程,众筹最后6天! >点此立即众筹<

不断增加的开关电源功率密度,已经受到了无源器件尺寸的限制。 采取高频运行,可以大大降低无源器件,如变压器和滤波器的尺寸。 但是过高的开关损耗势必成为高频运行的一大障碍。 为了降低开关损耗和容许高频运行,谐振开关技术已经得到了发展。这些技术采用正弦方式处理电力,开关器件能够实现软转换。 使得开关损耗与噪声大为降低。

在各种类型的谐振转换器中,最简单和最普遍的谐振转换器为 LC 串联谐振转换器,其中整流器-负载网络与 LC 谐振网络串联,如 图 1 [2-4]所示。 在该电路结构中,LC谐振网络与负载一起形成分压器。 通过改变驱动电压Vd的频率,可以改变该谐振网络的阻抗。输入电压在谐振网络阻抗与反射负载之间进行分压。由于分压作用,LC 串联谐振转换器的 DC 增益总是小于1。在轻载条件下,相比谐振网络的阻抗而言,负载阻抗很大。全部输入电压都被施加到负载上。 这使得轻载下很难调节输出。 在空载时,为了能够调节输出,理论上谐振频率应该为无限大。

为了打破串联谐振转换器的限制,LLC谐振转换器已经获得提出[8-12]。 LLC 谐振转换器是一种改进型的LC 串联谐振转换器,通过在变压器初级绕组放置一个并联电感而得以实现,如图 2所示。 采用并联电感可以增加初级绕组的环流,有利于电路运行。 由于这个概念不直观,在该拓扑首次提出时没有受到足够的重视。 然而在开关损耗相比通态损耗占主导比重的高输入电压应用中,却有利于效率的提高。

在大多数实际设计中,该并联电感采用变压器的励磁电感。 LLC谐振转换器的电路图与LC串联谐振转换器的电路图十分相似。 唯一的差别在于:励磁电感的取值不同。 LLC谐振转换器的励磁电感远远大于LC串联谐振转换器的励磁电感(Lr),LLC谐振转换器中的励磁电感为Lr的3-8倍,通常通过增加变压器的气隙来获得。

LLC谐振转换器具有许多超越串联谐振转换器的优点。它能够在较宽的电源和负载波动范围内调节输出,而开关频率波动却较小。 在整个工作范围内,能够获得零电压开关(ZVS)。 全部固有的寄生参数均可以用于实现软开关,包括所有半导体器件的结电容、变压器漏感与励磁电感。

包括LLC谐振转换器工作原理的解释、变压器与谐振网络的设计、元器件的选型。 给出设计实例,逐条地解释设计过程,有助于进行LLC谐振转换器的设计。

LLC 谐振转换器与基波近似

图 3中给出了半桥 LLC 谐振转换器的原理简图,图中,Lm指励磁电感,用作并联电感,Lr指串联谐振电感,Cr 指谐振电容。图 4给出了 LLC 谐振转换器的典型波形。 假定:工作频率与谐振频率相同,后者决定于 Lr 与Cr.之间的谐振。 由于励磁电感相对较小,形成相当量的励磁电流(Im),在初级绕组续流,并不参与电能的传输。初级电流(Ip)为励磁电流与次级电流反射到初级的电流之和。

一般情况下,LLC 谐振拓扑包括 3 级电路,如图 3所示,即方波发生器、谐振网络和整流器网络。

? 方波发生器负责产生方波电压Vd,通过50%占空比交替驱动开关Q1 和Q2 来实现。 通常,在连续切换中会引入一个较小的死区时间。 方波发生器可以构造成全桥或半桥类型。

? 谐振网络包括一只电容、变压器漏感和励磁电感。 谐振网络滤除高次谐波电流。 在本质上,即使方波电压施加到谐振网络上,也只有正弦电流容许流过该谐振网络。 电流(Ip)滞后于施加到谐振网络上的电压(即方波电压(Vd)的基波分量被施加到半桥的图腾柱上),容许MOSFET零电压开通。 如图 4所示,当 MOSFET 电压为零时MOSFET 开通,此时电流流经反并联二极管。

? 整流器网络产生直流电压,采用整流器二极管和电容对交流电进行整流器。 整流器网络可以设计成带有容性输出滤波器的全波整流器桥或中心抽头配置。

谐振网络的滤波作用可以采用基波近似原理,获得谐振转换器的电压增益,这需要假定方波电压的基波分量输入到谐振网络,并传输电能至输出端。 由于次级端整流电路可作为阻抗变压器,所以其等效负载电阻与实际负载电阻并不相同。图 5所示为该等效负载电阻的推导方式。 初级电路由正弦电流源Iac代替,方波电压VRI出现在整流器的输入端。 由于|Iac|的平均值为输出电流 Io,则Iac可以描述为

注:Vo指输出电压。

由于VRI的各次谐波分量不涉及功率传输,交流等效负载电阻可以采用(VRIF/ Iac)计算:

考虑到变压器匝比(n=Np/Ns),则初级等效负载电阻可

以描述为

采用等效负载电阻,可以得到交流等效电路,如图 6

FF

所示,图中Vd 和VRO 分别指驱动电压Vd 和反射输出电压VRO (nVRI)的基波分量。

利用式5中得到的等效负载电阻,可以推导出LLC谐振转换器的特性。 利用图 6所示的交流等效电路,可得电压增益M的计算公式:

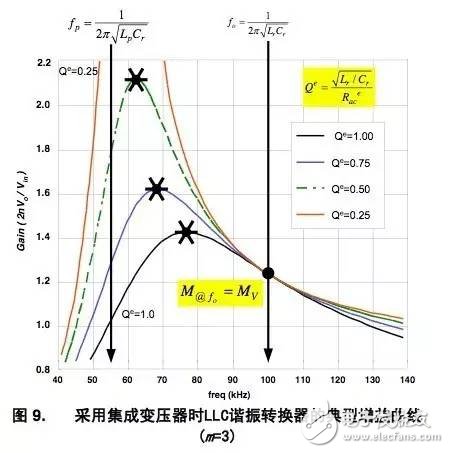

图7给出了 Q 值不同且 m=3、fo=100kHz 且fp=57kHz

时,式 6 表达出的增益。 由图 7可见,当开关频率处于谐振频率fo附近时,LLC 谐振转换器显示的电压增益特性几乎独立于负载。 这是LLC型的谐振转换器超出传统串联谐振转换器非常突出的优势。 因此,想当然地使得转换器运行在谐振频率附近,降低开关频率波动。

LLC 谐振转换器的工作范围受制于峰值增益(可达最大增益),该增益标示有‘*’(如图 7所示)。 需要说明的是,峰值电压增益不会出现在fo 或 fp.附近。 获得峰值电压增益的频率位于fp和fo之间,如图 7所示。 随着负载变轻,Q值下降,峰值增益频率移向fp,峰值增益随之下降。 因此对于谐振网络设计而言,满载条件为最坏情况。

集成变压器的考虑事项

对于实际设计,通常需要采用集成变压器的概念设计实现磁器件(串联电感与并联电感),其中将漏感用作串联电感,励磁电感用作并联电感。 当采用这种方法构造磁元件时,需要将图 6中的等效电路改进成图8,这是因为不仅在初级,而且在次级都存在有漏感。不考虑变压器次级的漏感时往往会导致设计出错。

在处理实际变压器时,提倡采用具有Lp 和 Lr的等效电路,因为通过分别开路和短路次级绕组,在初级可以很容易地测得这些电感取值。 在实际变压器中,Lp和Lr可分别在次级端绕组开路和短路的条件下在初级侧测得。

在图 9中,引入了一个虚拟增益 MV,这个增益是由次级端漏电感导致的。 采用图9改进后的图 9等效电路,调整式6的增益表达式,可以得到集成变压器的增益表达式:

工作模式与可达最大增益考虑事项

LLC 谐振转换器的工作频率可以低于或高于谐振频率(fo),如图 10所示。图 11给出了每种工作模式下变压器初级与次级的电流波形。 在低于谐振频率下(情况I )工作,容许次级整流器二极管实现软换流,尽管此时环流相比较大。 随着工作频率降低,偏离 ID谐振频率,环流大大增加。 尽管在高于谐振频率下(情况II )工作,容许环流降低,但是整流器二极管不能实现软换流。 对于高输出电压应用中,例如等离子显示屏(PDP),提倡采用低于谐振频率下工作,因为这类应用场合中整流器二极管的反向恢复损耗相当

大。 低于谐振频率下工作,对于负载波动而言,还具有较窄的频率范围,因为甚至在空载条件下运行,其工作频率受限制低于谐振频率。

另一方面,在上谐振工作时,相比在下谐振工作时,通态损耗较小。 对于低输出电压的应用场合,例如液晶显示器(LCD)TV或膝上适配器,表现出良好的效率。 因为这类应用场合中,次级整流器二极管适合采用肖特基二极管,此时反向恢复问题已无关重要。 然而,在上谐振频率工作时,在轻载下工作会使开关频率大量增加。 上谐振工作时,需要采用频率跳跃功能,防止开关频率剧烈上升

最大增益与峰值增益需求

高于峰值增益频率下,谐振网络的输入阻抗呈感性,谐振网络的输入电流 (Ip)滞后于施加在谐振网络的电压(Vd). 这样 MOSFET 可以实现零电压开通 (ZVS),如图 12所示。 低于峰值增益频率下,谐振网络的输入阻抗呈容性,Ip超前Vd. 当工作在容性区间,在开关切换过程中,MOSFET的体二极管反向恢复,引起严重的噪声。 进入容性区间的另外一个问题是,由于增益斜率出现反向,输出电压失控。 最小开关频率应该适当地高于峰值增益频率

LLC谐振转换器的合适输入电压范围决定于峰值电压增益。 因此,谐振网络的设计应确保增益曲线具有足够的峰值增益,并能够覆盖整个输入电压范围。 但是,低于峰值增益点,ZVS 条件会丢失,如图 12所示。因此当确定最大增益点时,要求保留一些裕量,在负载瞬态变化和启动阶段,确保获得稳定的ZVS工作。典型地,对于实际设计,选取最大增益的 10~20% 作为裕量,如图 13所示。

在某一给定的条件下,即使采用增益公式6得到峰值增益,也是很难地以明确形式表达出峰值增益。 为了简化分析与设计,可以采用仿真工具获得峰值增益,如图 14所示。图中给出了不同 m 取值时,随着Q值变化的峰值增益(可达最大增益)。 可见,通过减少m和Q值,可以获得较高的峰值增益。 对于给定的谐振频率 (fo)和 Q 值,降低m意味着励磁电感减少,将导致环流增加。 自然地,应在可用增益范围与导通损耗之间作出权衡。

FSFR系列的特征

FSFR系列产品集成有脉冲频率调制(PFM)控制器以及专门设计用于零电压开关(ZVS)半桥转换器的MOSFET,外部元器件用量最少。内部控制器包括一个欠压闭锁、优化的高端/低端栅极驱动器、温度补偿的精密电流控制振荡器以及自保护电路。 与分立MOSFET和PWM控制器方案相比,FSFR系列产品减少了总成本、元器件数量、尺寸和重量,与此同时却提高了效率、生产率和系统可靠性。

设计步骤

本节提供了基于图 17所示原理图的设计步骤。 集成变压器具有中心抽头,输入电压来自预调节器-功率因数校正器(PFC)。 带有 192W/24V 输出的DC/DC转换器已被选中作为设计实例。 设计规格如下:

- 标称输入电压: 400VDC (PFC 级的输出)- 输出: 24V/8A (192W)

- 保持时间要求: 20 毫秒(50Hz 电源频率)

- PFC 输出直流电容: 220μF

[[STEP-1] 确定系统的各项指标

[[STEP-2确定谐振网络的最大与最小电压增益

根据上节讨论,为了减少开关频率波动,典型地,LLC谐振网络应设计工作在谐振频率 (fo) 附近。 鉴于LLC谐振转换器由PFC输出电压供电,为使该转换器的工作频率设计在fo,应该适应PFC标称输出电压。

由式10可见,fo处的增益为m (m=Lp/Lr).的函数。 fo处的增益决定于m值的选取。 尽管m 取值较小时,可以得到高的峰值增益,但是过小的m 取值会导致变压器的耦合恶化和效率下降。 典型地,设置m 位于3~7,可使谐振频率处(fo)的电压增益为1.1~ 1.2。

m取值选择后,PFC标称输出电压时的电压增益可以描述为:

- 磁芯: EER3542 (Ae=107 mm2)

- 骨架: EER3542(水平/分段类型)

6. 实验验证

为了验证本使用说明书中设计过程的有效性,对本转换器设计实例的进行了建立和测试。 设计实例中涉及的全部电路元件都得到了采用。

图 30和图 31给出了标称输入电压时满载与空载下的工作波形。 可见,由于谐振作用,在开通前,MOSFET的漏源电压 (VDS)下降至零,实现了零电压切换。

图 32给出了满载条件下谐振电容电压和初级电流波形。 谐振电容电压与初级端电流的峰值分别为 325V 与1.93A,这与设计过程章节中第八步的计算值非常匹配。图 33给出了输出短路条件下谐振电容电压和初级端电流波形。 对于输出短路条件,当初级电流大于3A时,过电流(OCP)发生动作。 谐振电容的最大电压略高于计算值419V,其原因是1.5μs的关闭延时使得OCP动作电流略高于3A(参阅FSFR2100产品说明书)。

图 34给出了满载和空载条件下整流器二极管的电压与电流波形。 由于杂散电感引起的电压过冲,电压应力略高于第九步中的计算值。图 35 给出了满载和空载条件下输出电压的纹波波形。 输出电压的纹波与第九步中的设计值相配。

图 36给出了不同负载条件下效率测量结果。 满载条件下的效率大约为94%。

图文 I 网络

-

LLC

+关注

关注

36文章

567浏览量

76745 -

谐振

+关注

关注

5文章

371浏览量

39578

原文标题:LLC计算最全套路

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

LLC最全计算套路

LLC最全计算套路

评论