原创:DrChip芯片行业

随着先进封装技术的发展,翘曲问题日益严重。这种现象通常由多种材料混合造成的不均匀应力点引起,影响封装的组装和实际使用中的长期可靠性。

翘曲在确定先进封装是否能够成功组装以及满足长期可靠性目标方面扮演了关键角色。新进展,如改进了热性能的模塑材料、高级建模技术以及涉及两步模塑的创新架构,正在使对封装翘曲的控制变得更加有效,同时也提供了优化多芯片系统的更大灵活性。

翘曲是由硅芯片、模塑材料、铜、聚酰亚胺等材料之间的热膨胀系数(CTE)不匹配所导致的必然结果。它在整个组装过程中变化不定,可能会导致裂纹或剥离失效。最容易出现问题的区域包括低介电常数核心,这些区域容易发生裂纹和短路,或者在微凸点中出现非湿润失效。

“目前关于封装翘曲和应力的讨论非常热门,”Synopsys产品管理高级总监Kenneth Larsen表示,“这不仅仅是在制造过程中,温度变化可能导致翘曲,还包括当你将设备插入插座时,可能会遇到翘曲问题。”

即便在组装和封装过程中有效地解决了翘曲问题,设备在实际使用中仍可能出现翘曲。这在异质设计中尤其明显,其中芯片采用不同材料或工艺,而逻辑集中在不对称封装的特定区域。

由于对更高处理速度和低延迟的需求,尤其是在移动、汽车和高性能计算/AI应用中,多芯片封装的过渡正迅速加速。工程师们越来越依赖建模和仿真来理解温度依赖的翘曲,这种翘曲可能因芯片厚度、模具与硅比例及基板类型而异。尽管有机基板因其价格低廉且可以定制到任何尺寸而非常有吸引力,但它们比硅基板更具柔韧性,容易发生翘曲。

所有这些考虑都指向了对复杂异质组装和封装进行热学和结构建模的必要性。“高级建模允许公司模拟不同材料、热动态和机械应力在组装过程中的行为,”Amkor芯片/FCBGA集成副总裁Mike Kelly表示,“通过这种虚拟实验,可以预测和缓解潜在挑战,确保最终产品满足严格的质量和可靠性标准。”

翘曲的发生机制

组装过程中包含多个加热和冷却步骤,这会在具有不同热和机械性能的相邻材料之间引起一定程度的变形。在先进封装中,100微米范围的翘曲并不罕见。

翘曲问题的一个原因是芯片的尺寸较大,而芯片、重新分布层(RDL)、基板和各种尺寸的凸点的加工窗口非常紧凑。相邻材料的膨胀和收缩取决于材料的CTE,即每度温度变化引起的尺寸增加(ppm/°C)。

“芯片通常是相对较大的芯片,”Promex Industries首席执行官Dick Otte表示,“例如iPad中,芯片尺寸为20 x 30毫米,可能有多达10,000个I/O,通常为铜柱。仅仅将单个芯片放置在基板上就可能是一个挑战,因为间距非常小。因此,对于这些组装而言,控制翘曲和平整度至关重要。在整个回流焊接过程中,它需要保持平整,以弥合铜柱与电路板上的接触点之间的间隙而不发生翘曲。”

翘曲可以向上发生(边缘弯曲,称为“微笑”),也可以向下发生(称为“哭泣”),这取决于堆叠材料的相对CTE。例如,硅的CTE为2.8,铜为17,FR4 PCB为14至17 ppm/°C。硅互连层与有机基板之间的CTE不匹配最为严重。

将封装堆叠视作材料组合有助于理解这一现象。“你需要考虑材料的CTE及其在温度下的反应,”Otte说,“比如你在上面有相对低膨胀的铜,而底部有焊料,它们的膨胀量基本相等,中间则有一个高膨胀的介电材料,所以当你加热它时,它的膨胀量也大致相同。如果你把所有的铜放在上面,当你加热它时,它会向铜的一侧翘曲。铜的CTE是15 ppm/°C,而有机材料的CTE大约是其两倍,25到30 ppm/°C。”

其他关键指标包括材料的模量或弹性,以及玻璃化转变温度(Tg),即材料开始流动的温度。这些值也是相关的。例如,聚合物(如环氧模塑化合物(EMC))的热行为中,当温度超过玻璃化转变温度时,模量通常会急剧下降。这是因为在液态时,聚合物链会自由滑动,而在固态时则较为刚性。

除了焊料回流外,翘曲还常发生在模塑后固化阶段。ASE的Hung-Chun Yang及其同事最近发现,芯片厚度对现有芯片优先流封装过程中的翘曲水平有显著影响。研究表明,“固化后出现严重的晶圆翘曲,导致对齐失效并在后续工艺中处理困难。”为减少封装翘曲,团队用玻璃载体替代了金属载体/薄膜方案。团队还发现,3D有限元法(FEM)能够捕捉翘曲行为,并与实际测试数据相符。

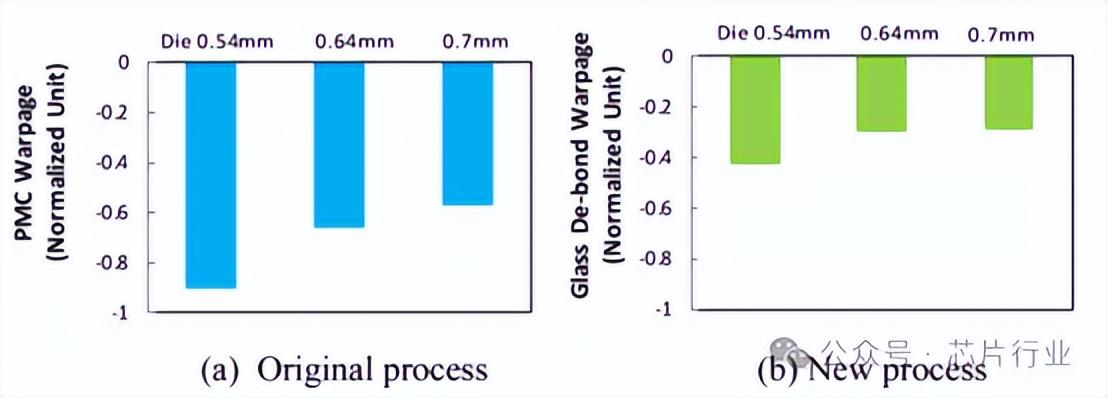

图1:改进流程中的玻璃载体(右)引起的翘曲较少。增加芯片厚度也显著减少了翘曲。来源:ASE

芯片优先流程从探测制造好的晶圆开始,随后对其进行薄化并电镀铜柱,然后切割并放置已知良品的芯片。最初的流程使用了一个金属载体,该载体在模塑后被去除,替换为薄膜。改进后的流程使用了一个在模塑、固化、模具磨削、RDL和铜柱处理过程中都保持在位的玻璃载体,然后再进行脱粘。

在模塑后固化过程中,翘曲达到最大值,并且在固化步骤和玻璃载体脱粘后变化最为显著。玻璃载体流程总体上减少了翘曲。此外,ASE工程师确定,通过将晶圆厚度从0.54毫米增加到0.7毫米,可以额外减少35%的翘曲。

第二种减少翘曲的策略是使用具有不同热性能的EMC,特别是在工艺需要两步模塑时。Amkor工程师最近通过建模和制造两个高性能测试样本评估了两种高性能多芯片封装的可靠性表现。一个模块大约是一个掩模的大小,包含1个ASIC、2个HBM和2个桥接芯片(33 x 26毫米)。第二个模块为三个掩模的大小,包含2个ASIC、8个HBM和10个桥接芯片(54 x 46毫米)。Heejun Jang及其同事在Amkor Technology Korea使用Ansys Parametric Design Language(APDL)版本16.1进行建模和仿真,并将结果与包含虚拟芯片的测试样本进行了比较。

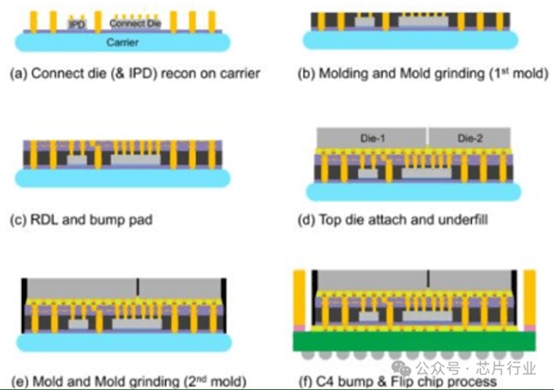

Amkor的“最后封装”S-Connect流程从载体晶圆开始,制造用于桥接芯片和铜柱的铜柱(见图2)。集成的被动器件和桥接芯片被嵌入第一模具中,该模具固化后被磨回。RDL沉积在模具上,焊料捕集垫和芯片通过微凸点附着在垫上。然后,焊料被回流和填充。第二模具围绕正面芯片固化并磨回,然后进行C4凸点加工以实现与基板的翻转连接。仿真分析了9种不同CTE(7到12 ppm Tg以下,22到46 ppm Tg以上)和高至低玻璃化转变温度(145°C到175°C)的EMC组合下的翘曲情况。

图2:S-Connect封装的工艺流程。来源:Amkor

翘曲作为EMC选择的函数表明,所有材料在室温下表现出相同的微笑模式,在高温(250°C)下表现出哭泣模式。CTE较低的EMC导致的翘曲较少。在模具占据相对较大区域时,翘曲水平更加明显。更重要的是,相对于450μm的芯片,650μm厚的芯片翘曲水平大约高出50%。有趣的是,较厚的硅芯片在控制总体模块翘曲方面的效果是EMC材料选择的3倍,因此芯片厚度是减少翘曲的最大杠杆因素。

一旦确定了封装配置,可靠性测试至关重要。Amkor对其先进封装测试样本进行了湿气抵抗测试、高加速应力测试、热循环B条件和高温存储测试。这些测试是发现早期失效问题所必需的,横截面分析可以揭示可能导致实际使用中故障的裂纹或潜在缺陷。

尽管上述例子可能代表了今天的大型多芯片封装,但封装尺寸正在不断增长,这意味着需要更多关注翘曲问题。越来越多的组装线将推动数字双胞胎或虚拟表示的应用,以实现工艺和封装优化。

“通过创建半导体组装线的虚拟表示,可以识别潜在的关注点并优化控制策略,”Amkor的Kelly表示,“在物理原型甚至尚未创建之前,虚拟制造可以帮助公司评估设计更改对制造过程的影响。这不仅加快了产品开发周期,还减少了昂贵错误的风险。”

及早识别潜在的瓶颈进一步缩短了周期时间,并提升了整体效率。

结论

未来,设计师和封装工程师团队将需要更加关注机械和热学属性。“新的封装设计要求在堆叠过程中对机械和电气公差进行准确分析,”Amkor工程与技术营销副总裁Curtis Zwenger表示,“随着工艺能力的要求不断提高,像CpK这样的常见指标也越来越重要。通过这种类型的建模,可以在工艺开发的早期识别这些关键交互,从而指导先进工艺控制的投资,确保工艺能力得到保持。”

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!诚邀您报名参会:https://w.lwc.cn/s/n6FFne

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54593浏览量

470594 -

晶圆

+关注

关注

53文章

5475浏览量

132886 -

先进封装

+关注

关注

2文章

569浏览量

1074

发布评论请先 登录

揭秘半导体后道封装辅助小设备:UV解胶机的三大硬指标与未来趋势

制程残余应力致CMOS芯片翘曲,白光干涉精准测量方案

半导体aligner寻边器怎样依据晶圆尺寸及翘曲度精准选型?

适配超薄晶圆的aligner型号有哪些?能处理±1.5mm翘曲吗?

从设计到工艺:PCB防翘曲全流程指南

从材料到回流焊:高多层PCB翘曲的全流程原因分析

印刷电路板(PCB)翘曲问题及其检测技术

PCB翘曲不用愁!| 鑫金晖压板烘箱专治电路板卷翘异常,高效节能热压整平

wafer晶圆厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量的设备

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

wafer晶圆几何形貌测量系统:厚度(THK)翘曲度(Warp)弯曲度(Bow)等数据测量

先进封装晶圆翘曲控制!

先进封装晶圆翘曲控制!

评论