高速并行总线的工作原理及其具体类型是一个涉及硬件技术和数据传输的复杂话题。以下是对高速并行总线工作原理的概述以及几种常见的高速并行总线的介绍。

高速并行总线的工作原理

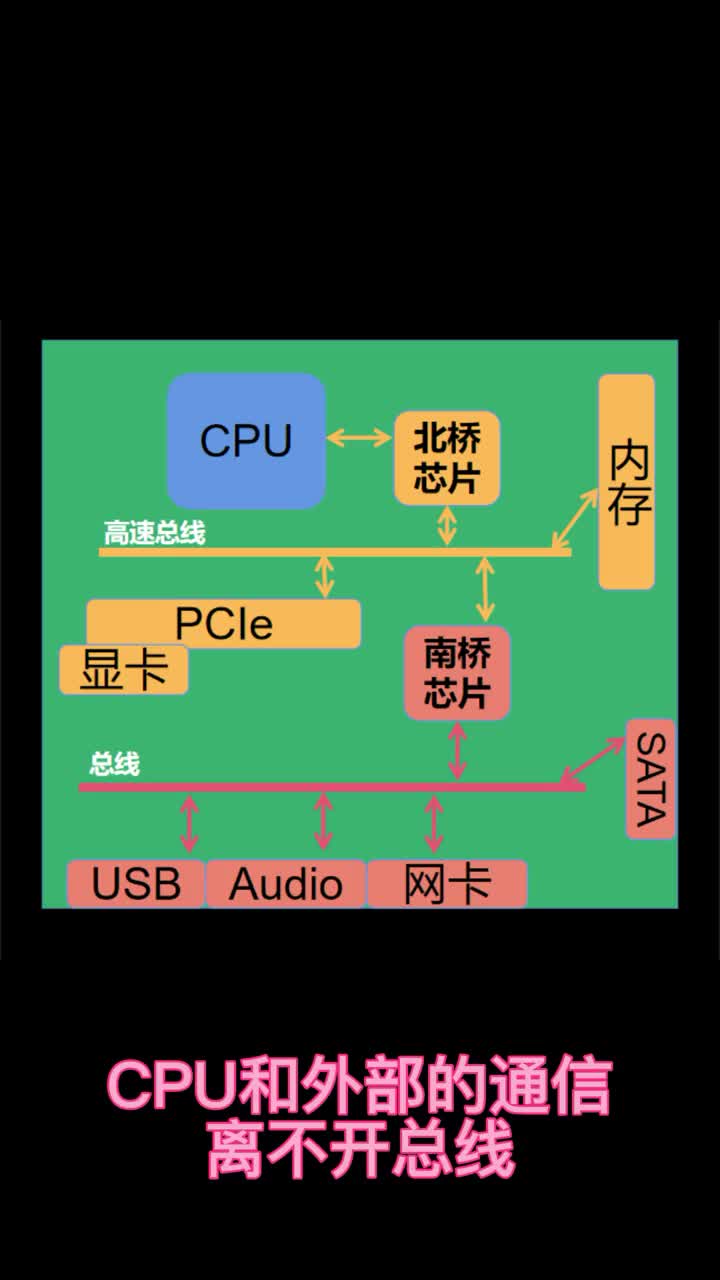

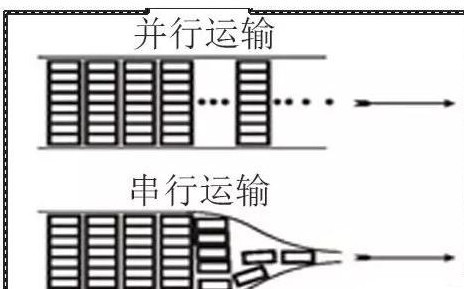

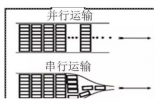

高速并行总线的工作原理主要涉及多个数据通道的同时传输。与串行总线相比,并行总线在同一时间内能够传输多个数据位,从而提高了数据传输的速率。这种并行传输方式通常通过一组数据线来实现,每条线传输数据的一个位(bit)。为了确保数据的同步和完整性,还可能需要额外的控制线和时钟信号线。

并行总线的工作原理可以概括为以下几个步骤:

- 数据分割 :发送端将数据按照一定的位宽分割成多个数据位,每个数据位通过不同的数据线同时传输。

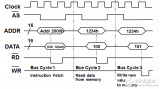

- 同步控制 :使用时钟信号或其他同步机制来确保接收端能够正确地接收和重组这些并行传输的数据位。

- 传输与接收 :数据在并行总线上同时传输,接收端则同时接收这些数据位,并按照一定的规则进行重组,以恢复原始数据。

- 错误检测与校正 :在传输过程中,可能会遇到噪声、干扰等问题,导致数据出错。因此,并行总线通常需要实现某种形式的错误检测与校正机制,以确保数据的准确性。

高速并行总线的类型

高速并行总线有多种类型,每种类型都有其特定的应用场景和优势。以下是一些常见的高速并行总线:

- PCI(Peripheral Component Interconnect)总线

- 简介 :PCI总线是早期计算机系统中广泛使用的一种并行总线标准。它采用32位或64位数据传输,具有较高的数据传输速率和即插即用等特性。

- 特点 :支持多个设备同时连接,具有高速缓存技术,提高了数据传输速度。然而,随着技术的发展,PCI总线逐渐被更先进的总线标准所取代。

- AGP(Advanced Graphics Port)总线

- DDR(Double Data Rate)总线

- 简介 :DDR总线是一种用于内存模块的高速并行总线标准。DDR总线通过在时钟信号的上升沿和下降沿都传输数据,实现了双倍的数据传输速率。

- 特点 :DDR总线具有较高的数据传输速率和较低的功耗,广泛应用于计算机内存系统中。随着技术的发展,DDR总线已经发展到了多个版本(如DDR2、DDR3、DDR4等),每个版本都在前一代的基础上进行了改进和优化。

- 其他高速并行总线

从第一代DDR 开始,一直到即将推出的第五代的DDR,数据传输速率在一直在不断增加,同时功耗及供电电压在不断降低。DDR系统要在这种越来越严苛的条件下还能保证良好的工作性能,就需要在信号完整性方面必须满足特定的要求。保证整个系统的信号完整性不出问题对系统的正常工作而言非常关键, 或者说只有保证整个系统的信号完整性不出问题才能确保不同厂商生产的器件整合在一起时还可以正常工作。那DDR总线在传输数据中会有哪些信号完整性问题呢?

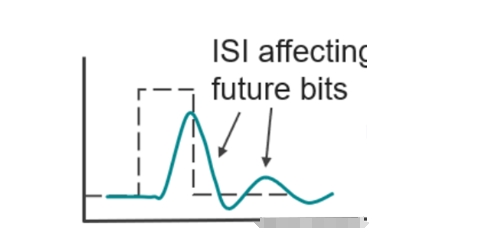

ISI

码间干扰( Inter Symbol Interference, ISI)是指,当信号通过实际信道时,信号的带宽变窄,同时信号的上升边、下降边变长。因此单位脉冲响应会变宽,即一个比特位所占有的时间会延长,并产生拖尾,如图所示。

这样接下来的比特位就会受到之前比特位的拖尾的影响。一个比特位可能会受到多个比特位的拖尾的影响,这个比特位的实际电压值就等于本身的电压值与诸多拖尾的电压值的叠加值,这样对该比特的电压值就有可能产生误判,导致本来是低电压的比特位判定为高电压,本来是高电压的比特位判定为低电压。

可以看出ISI产生的原因是单位脉冲响应的延展。而单位脉冲响应之所以产生了延展主要因为两点,一是在信道上信号中的高频部分和低频部分的传输速度不一致,高频部分的传输速度要大于低频部分,造成信号在时域上的展宽,这种现象我们称之为色散。二是在信道中,信号中高频部分的衰减要大于低频部分,这是因为信道的插入损耗随着频率的增加而变大,这也会造成信号在时域中的展宽。

同时,ISI和信道中所传输的具体码型也有关系,传输的码型不同,产生的ISI也会不同。由前面的解释可以知道,当前比特位所受到的ISI与其前后的几个比特位都有关系,因此不同的码型会使边沿变快或者变慢,导致其眼图有多个交叉点存在。

总结

高速并行总线通过多个数据通道的同时传输来提高数据传输速率,广泛应用于计算机系统和各种电子设备中。然而,随着技术的发展和串行总线技术的普及,许多传统的高速并行总线标准已经逐渐被更先进的串行总线标准所取代。这主要是因为串行总线在数据传输速率、信号完整性、功耗和布线复杂度等方面具有更多的优势。

-

驱动器

+关注

关注

53文章

8302浏览量

147230 -

数据传输

+关注

关注

9文章

1964浏览量

64893 -

图形处理

+关注

关注

0文章

45浏览量

13842 -

并行总线

+关注

关注

0文章

30浏览量

13540

发布评论请先 登录

相关推荐

高速并行总线互连

什么是基于FPGA的ARM并行总线?

高速并行总线信号完整性测试技术

高速并行总线信号完整性测试技术

并行总线有哪些?串行总线有哪些?

并行总线是什么?(并行总线协议介绍)

基于FPGA的ARM并行总线和端口设计

高速并行总线的工作原理是什么 高速并行总线有哪些

高速并行总线的工作原理是什么 高速并行总线有哪些

评论