DDS(Direct Digital Synthesizer,直接数字频率合成器)技术是一种频率合成方法,其输出频率与时钟之间存在密切的关系。

一、DDS基本原理

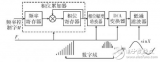

DDS技术通过编程频率控制字来分频系统时钟,以产生所需的频率。DDS系统的核心部件包括相位累加器、波形存储器(ROM查询表)、数模转换器(DAC)和低通滤波器。其工作原理可以概括为:在每个时钟周期,相位累加器根据频率控制字累加相位值,累加的结果作为地址去查询波形存储器中的波形数据,然后将波形数据通过DAC转换为模拟信号,最后通过低通滤波器得到平滑的波形输出。

二、DDS输出频率与时钟的关系

DDS输出频率与时钟的关系可以通过以下公式来表达:

**F_{out} = frac{K times f_{clk}}{2^N} ] 其中: - (F_{out}) 是DDS的输出频率。 - (K) 是频率控制字,它是一个整数或小数,用于控制DDS的输出频率。 - (f_{clk}) 是参考时钟频率,即DDS系统使用的时钟源频率。 - (N) 是相位累加器的位数,它决定了DDS的频率分辨率和相位累加器的精度。

直接数字式频率合成器 (Direct Digital

Synthesizer, DDS )是一种新型的频率合成技术,具有相对带宽大、频率转换时间短、稳定性好、分辨率高、可灵活产生多种信号等优点,被广泛应用于现代电子系统及设备的频率源设计中。

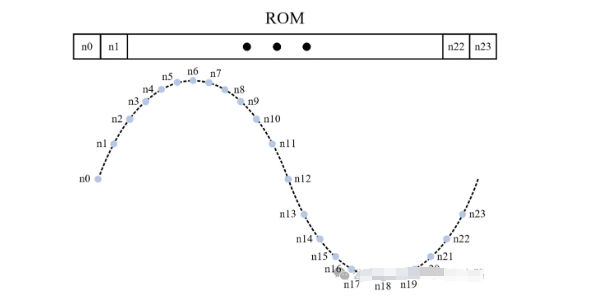

假设存储空间里有一组数据:n0~n23,这组数据是对一个周期正弦波形采样的结果。现在计算机想输出其中一些数据点,有几种输出方法呢?

输出数据索引从n0开始依次累加M

1、M = 1:即n0、n1、n2、…、n22、n23、n0、n1、…

2、M = 3:即n0、n3、n6、…、n18、n21、n0、n3、…

假设系统时钟频率为Fclk,那么,在一秒钟的时间内索引会一直累加至M×Fclk,但是,存储空间内只有一个周期的数据,只有24个数据点,因此,每当索引值累加至23时便会溢出,继续从0开始累加,意味着一个周期输出完成,开始输出下一周期。

三、影响DDS输出频率与时钟关系的因素

- 参考时钟频率((f_ {clk})) : - 参考时钟频率是DDS系统的基础,它决定了DDS能够产生的最高频率。理论上,DDS可以产生的最高频率是参考时钟频率的一半(即奈奎斯特频率),但由于实际电路中的限制(如DAC的带宽、低通滤波器的截止频率等),实际可实现的最高频率通常会低于这个值。 - 参考时钟频率的稳定性也直接影响到DDS输出频率的稳定性。因此,在选择参考时钟源时,需要选择具有高稳定性的晶振或其他时钟源。

- 频率控制字((K)) : - 频率控制字是控制DDS输出频率的关键参数。通过改变频率控制字,可以实现对DDS输出频率的精确调整。 - 频率控制字的取值范围受限于相位累加器的位数。当相位累加器的位数确定后,频率控制字的取值范围也就确定了。

- 相位累加器位数((N)) : - 相位累加器的位数决定了DDS的频率分辨率。位数越多,DDS的频率分辨率越高,即能够产生的最小频率间隔越小。但同时,也会增加系统的复杂性和功耗。 - 相位累加器的位数还决定了DDS能够产生的最高频率。在参考时钟频率确定的情况下,相位累加器的位数越多,DDS能够产生的最高频率也越高(尽管实际可实现的最高频率受到其他因素的限制)。

四、DDS输出频率与时钟关系的实际应用

在实际应用中,需要根据具体需求来选择合适的参考时钟频率、频率控制字和相位累加器位数。例如,在需要产生高精度、高分辨率的频率信号时,可以选择较高的参考时钟频率和较多的相位累加器位数;而在对频率分辨率要求不高但需要快速频率切换的应用场景中,则可以选择较低的参考时钟频率和较少的相位累加器位数以简化系统设计和降低成本。 此外,还需要注意DDS输出频率与时钟之间的相位关系。

由于DDS是基于数字信号处理技术实现的频率合成器,因此其输出信号的相位是可控的。通过调整相位控制字或相位累加器的初值等参数,可以实现对DDS输出信号相位的精确控制。这一特性使得DDS在需要精确控制信号相位的应用场景中(如雷达、通信等领域)具有广泛的应用前景。

-

频率合成器

+关注

关注

5文章

222浏览量

32442 -

时钟

+关注

关注

11文章

1750浏览量

131948 -

DDS

+关注

关注

21文章

637浏览量

153089 -

输出频率

+关注

关注

0文章

10浏览量

8298

发布评论请先 登录

相关推荐

关于DDS输出信号频率的分辨问题

请问在DDS系统中通过DDS内部倍频得到芯片参考时钟内部倍频是否对输出信号有影响?

AD5933和AD5934的时钟频率差异的相关问题?

如何确定DDS输出信号频谱中的杂散源

AD9850 DDS 频率合成器的原理及应用

DDS阵列频率源技术研究

DDS有关名词解释

直接数字频率合成器(DDS)简介及其输出频谱中主相位截断杂散的频率和幅度

基于DDS的短波射频频率源设计方案解析

dds输出频率与时钟的关系

dds输出频率与时钟的关系

评论