IIC(Inter-Integrated Circuit,即集成电路总线)信号线需要增加上拉电阻,这主要是因为IIC的IO(输入输出)设计采用了开漏(Open-Drain)输出方式。开漏输出方式在IIC通信中扮演着至关重要的角色,而上拉电阻的加入则是实现这种通信方式有效性和可靠性的关键。以下是对此现象的介绍:

一、IIC通信与开漏输出

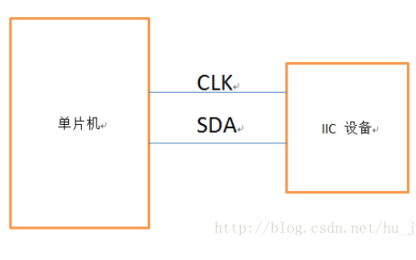

IIC通信协议是一种广泛应用的串行通信协议,由飞利浦公司(现被恩智浦电子收购)于1982年推出。它主要用于集成电路之间的通信,具有简单、高效的特点。IIC通信通过两条总线线路进行:串行数据线(SDA)和串行时钟线(SCL)。这两条线路的电平变化用于传输数据和时钟信号。

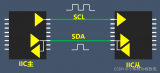

在IIC通信中,设备的IO端口采用开漏输出方式。开漏输出与推挽输出不同,它只能输出低电平(即将线路拉低),而不能直接输出高电平。这意味着,当没有设备主动拉低SDA或SCL线时,这两条线路需要依赖外部电路来维持高电平状态。这正是上拉电阻发挥作用的地方。

二、上拉电阻的作用

- 确保线路默认为高电平 :

- 如前所述,开漏输出无法直接输出高电平。因此,在没有设备主动拉低SDA或SCL线时,需要上拉电阻将这些线路拉高到电源电压(通常是Vcc或VDD),从而确保线路默认为高电平状态。

- 支持数据传输和时钟同步 :

- 在IIC通信中,SDA线上的数据位是在SCL为低电平时改变,在SCL为高电平时被采样。上拉电阻确保了SDA线在SCL为高电平时能够保持稳定的状态,这样接收设备才能正确地读取数据。

- 同时,SCL线作为时钟信号线,其高电平状态也由上拉电阻维持,确保了时钟信号的稳定性和同步性。

- 支持ACK信号 :

- 接收设备在接收到数据后,需要发送ACK(Acknowledge)信号来确认数据已被正确接收。ACK信号是通过将SDA线拉低来实现的。上拉电阻的存在使得接收设备能够将SDA线从高电平拉低到低电平,从而发送ACK信号。

- 解决总线竞争 :

- 在多主机IIC总线系统中,如果有多个设备试图同时控制总线,可能会导致总线竞争。上拉电阻有助于解决这种情况下的竞争,因为当一个设备释放总线时,其他设备可以接管并驱动总线。

- 限制电流和保护设备 :

- 当设备将SDA或SCL线拉低时,电流会通过上拉电阻流向地。选择适当的上拉电阻值可以确保电流不会过大,从而保护设备免受损坏。

- 提高信号完整性和噪声抑制能力 :

- 上拉电阻与线路的电容(主要是寄生电容)形成RC充电回路,有助于滤除高频噪声,提高信号完整性。同时,它还能减少信号反射和其他信号完整性问题。

三、上拉电阻的选择

选择合适的上拉电阻值对于IIC通信的可靠性至关重要。以下是选择时需要考虑的几个因素:

- 上升时间 :

- 电阻越大,上拉至高电平的速度就越慢。这会导致数据传输速率受限。因此,需要根据IIC总线的最大频率来确定合适的上升时间,并据此选择阻值。

- 最大灌电流能力 :

- IIC总线规范定义了每个总线上的设备在拉低线路时能够承受的最大电流(灌电流)。上拉电阻的阻值应确保即使所有挂载的设备同时尝试将线路拉低,也不会超过任何单个设备的最大灌电流规格。

- 功耗考量 :

- 电阻上会持续消耗一定的功率(P = I²R),尽管这部分功耗通常很小,但在低功耗设计中仍需考虑。较大的上拉电阻可以减小静态功耗,但也要平衡数据传输速度的需求。

- 设备数量 :

- IIC总线上的设备增加也会适当的减小电阻阻值以保证信号完整性。

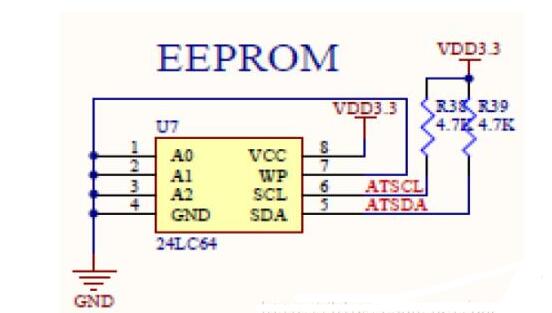

常见的上拉电阻阻值范围从1kΩ到10kΩ。对于标准速率为100kHz的IIC通信,通常选择4.7kΩ或10kΩ是比较合适的。对于快速模式(400kHz)或更快的高速模式(3.4MHz),可能需要降低阻值到几千欧姆,以保证信号的快速上升沿。

四、结论

综上所述,IIC信号线需要增加上拉电阻,主要是因为IIC的IO采用了开漏输出方式。上拉电阻在IIC通信中发挥着至关重要的作用,它确保了线路默认为高电平、支持数据传输和时钟同步、支持ACK信号、解决总线竞争、限制电流和保护设备、提高信号完整性和噪声抑制能力。因此,在设计和使用IIC总线时,必须合理选择和配置上拉电阻。

-

IO

+关注

关注

0文章

448浏览量

39138 -

上拉电阻

+关注

关注

5文章

359浏览量

30611 -

IIC

+关注

关注

11文章

300浏览量

38315 -

信号线

+关注

关注

2文章

171浏览量

21463 -

串行时钟

+关注

关注

1文章

5浏览量

10416

发布评论请先 登录

相关推荐

如果信号线是3.3V,给1.8V的上拉电压,最后输出的是多少伏?

SD卡的时钟线为什么可以不加上拉电阻呢?是因为时钟永远是输出信号吗?为什么输出信号就可以不加上拉电阻

IIC总线的相关资料推荐

IIC设备需要的线挺长如何操作?

使用IO PORT进行IIC通讯

【51单片机】IIC总线

IIC信号线需要增加上拉电阻,是因为IIC的IO是什么

IIC信号线需要增加上拉电阻,是因为IIC的IO是什么

评论