尤其在无线通信应用中,常常需要以非常短的时间切换 PLL (锁相环) 合成器的输出频率。在这类情况下,人们经常希望在相对较大的频率跳变之后,以不到 20µs 时间实现稳定的输出频率。以下我们将介绍,集成了 VCO 的超低噪声和超低寄生 0.37GHz 至 6.39GHz 整数 N PLL 合成器 LTC6946 怎样才能实现这样的目标。

更具体地说,针对20MHz 频率阶跃,我们选择适当的

LTC6946 参数以使其输出在尽可能短的时间里稳定至最终频率的 10kHz 之内。就本例而言,对于 LTC6946 我们可以采用一个20MHz 的比较频率(相位 - 频率检波器频率,即fPFD)。举个例子,这意味着如果基准输入频率 (fREF) 为 100MHz,则基准分频器 (R) 必需设定为等于 5。

在 PLL 系统中实现一个稳定环路的经验法则是使环路带宽 (LBW) 至少比fPFD小 10 倍。因此,而且为了优化快速稳定,在本例中我们可以设定 LBW = 2MHz。这与把 LBW 设定为等于频率偏移的做法正相反,这里,PLL 的带内相位噪声与 VCO 的相位噪声交叉以优化整体相位噪声性能。

我们选择由 LTC6946-3 产生 4GHz 输出信号,并使用 PLLWizard™软件工具来确定,建立 LTC6946 周边电路所需的滤波器组件值。PLLWizard 是一款免费工具,通过

www.linear.com.cn/pllwizard提供,以辅助 LTC6946 的设计和仿真。

在 PLLWizard GUI 中输入所希望的 fPFD和 LBW 值并点击几下鼠标后,我们就有了环路滤波器组件值,我们可以将这些组件安装到 LTC6946 电路中。图 1 的屏幕截图显示,PLLWizard 工具是怎样简化 LTC6946 的设计过程的。为了核实我们的工作是否正确,我们在给定条件下仿真 LTC6946 的预期相位噪声。图 1 包括 PLLWizard 的预测。

图 1:在 4GHz、20MHz fPFD 和 2MHz LBW 时,PLLWizard 工具的设置以及对 LTC6946 相位噪声的预测

接下来,我们给电路加电,用 Keysight E5052A 信号源分析仪测量相位噪声。图 2 显示,这一测量结果与上述仿真结果非常一致。

图 2:Keysight E5052A 信号源分析仪测得的

LTC6946 的输出相位噪声

现在,我们来检查一下,从 3.98GHz 到 4.00GHz 阶跃 20MHz 之后,LTC6946 的输出稳定到与最终频率值相差 10kHz 以内有多快。E5052A 可捕捉瞬态响应,如图 3 所示。

图 3:在 20MHz 频率跳变后,LTC6946 输出的稳定过程

我们通过缩小上述测量中 E5052A 检测器的带宽来放大 y 轴,以更准确地确定稳定时间。图 4 说明了 LTC6946 的输出是怎样在不到 15µs时间内稳定到与最终频率值相差不到 10kHz 的范围内的。

图 4:在 20MHz 频率阶跃后,LTC6946的输出

在不到 15µs 时间内稳定

应该提到的是,集成了 VCO 的新式合成器 IC 用多个内部 VCO 子频段来涵盖其整个输出频率范围。每次合成器 IC 的输出频率改变时,该 IC 都必须运行一次内部 VCO 校准例程,以确定正确的 VCO 子频段。在 PLL 的 LBW 相对较大的情况下,如我们的例子中那样,当切换频率时,最终确定校准流程所需的时间会占稳定时间的很大部分。由于 LTC6946-3 一般能够在略多于 10µs的时间内运行这种校准流程,所以我们能够实现约为 15µs 的总稳定时间。

图 3 和图 4 显示,在 VCO 校准时,LTC6946 的输出频率跳来跳去。这里显示这种行为是为了说明原因。在大多数实际情况下,人们不希望让输出频率这样跳来跳去。将 LTC6946 上的 “MTCAL” 寄存器设定为 “1”(“1” 是缺省值),就可通过在校准时抑制 RF 输出来应对这种情况。建议 “MTCAL” 始终设定为 “1”。

您可以遵照和修改本文提供的步骤,以确定适合您的应用参数。DC1705 (LTC6946 演示电路板) 为在各种滤波器和频率配置情况下评估 PLL 的性能提供了一个全面的开发平台。DC2026 Linduino®USB 控制器电路板在 PLL 演示电路板和使用 PLLWizard 工具的 PC 之间提供通信接口。

PLLWizard GUI 允许全面控制 DC1705。不过,为了在非常短的时间内设定 PLL IC 以实现快速频率切换,我们会编写一些 Linduino 代码,并以 DC2026 的最高 SPI 接口速度运行 DC2026。要通过 SPI 接口快速设定 PLL IC,使用 DC2026 和定制代码是至关重要的,如果需要,还可以利用 Arduino IDE 提供一种代码开发环境。

我们已经评估了我们的快速稳定合成器的相位噪声行为。然而,考虑到我们已经使环路带宽相对较大,所以有人可能会问,寄生性能会受到怎样的影响。有人可能会预期,使用典型的合成器 IC 时,寄生性能在这些条件下会受到损害。使用 LTC6946 时情况却不是这样的。在 2MHz 环路带宽和 20MHz fPFD 时,实现接近-90dBc 的基准杂散噪声 (从 4GHz 载波偏移 fPFD= 20MHz 时不想要的信号) 是引人注目的,正如图 5 显示的 LTC6946 频谱所确认的那样。

图 5:LTC6946的输出频谱,在 4GHz 输出、环路带宽为 2MHz 时展示了不同寻常的低杂散噪声

LTC6946 以能够产生低相位噪声和低寄生输出而闻名。我们在本文中展示了,使用 LTC6946,可以在不损害寄生性能的情况下,实现超快频率切换。在跳频通信应用中,要产生低相位噪声频率,LTC6946 是出色的选择。

-

Linear

+关注

关注

17文章

434浏览量

132107 -

pll

+关注

关注

6文章

788浏览量

135688

原文标题:用 PLL 实现超快频率切换

文章出处:【微信号:Linear-Technology,微信公众号:凌力尔特】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

大族激光薄片超快激光器产品介绍

小鹏大众将携手合力打造中国最大的超快充网络

FMC150不能转换出正确的波形是哪里出了问题?

kvm切换器怎么实现键盘热键切换

双层频率选择表面等效电路的条件

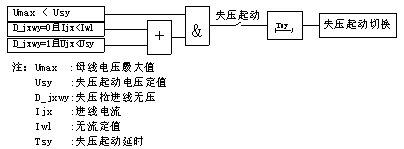

FSC中高压无扰动周波快速切换系统 双电源快切柜 介绍

DCM635无扰动快切装置切换安全吗,无扰动快切装置有哪些闭锁功能?

DCM635无扰动快切装置有哪些切换方式?无扰动快切装置切换原理是什么?

什么是超快激光器?

LTC6946是实现超快频率切换出色的选择

LTC6946是实现超快频率切换出色的选择

评论