Vivado 结果是否可重复用于相同的工具输入?

解决方案大多数情况下是可以的,Vivado 应该可在涉及相同应用的运行之间生成相同的结果:

-

设计源

-

约束

-

Tcl 脚本及命令顺序

-

工具与命令选项

-

Vivado 软件版本

-

多线程设置

这适用于从 HDL 综合到比特流生成的设计流程的各个环节。例如,构建脚本反复在同一系统或相似配置的机器上运行时,应该能生成相同的结果。

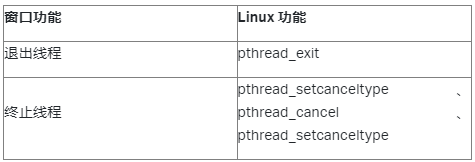

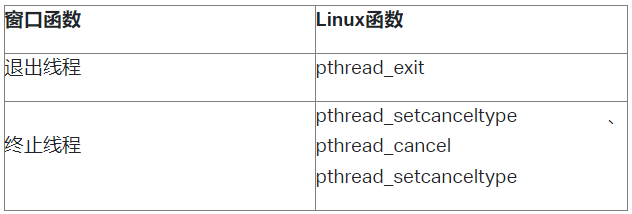

不同操作系统的结果通常可重复,但也不一定,特别是在使用 Linux 和 Windows 操作系统的情况下。

注意确定性

术语“可重复性”和“确定性”通常可交替使用,这种说法是不对的。Vivado 使用多线程来并行执行,因此它在定义上是不确定的。然而,Vivado 中的多线程可通过编程实现同步,因而多线程执行可重复。注意,除了多线程外,Vivado 也管理 OS 系统调用及内存管理等可导致不确定性的其它因数。

确定重复性问题

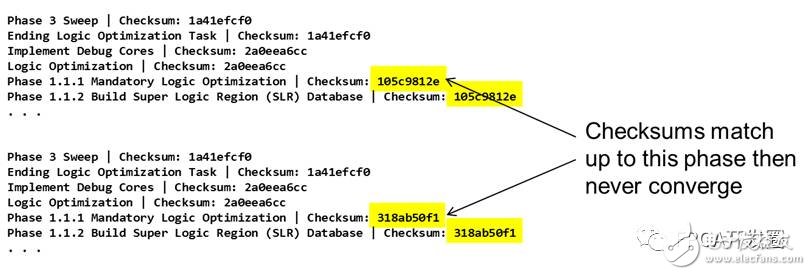

有分歧的运行最常见的症状是布线后时序结果的不同。如果您怀疑某个不可重复性的情况,并验证工具输入是完全相同,就可使用校验和来进一步验证分歧。Vivado 在每个实现方案命令的各个中间阶段,都会在日志中报告一个校验和,这是一个基于设计网表及物理数据的签名。校验和可以在不同的运行之间比较,校验和不匹配可帮助发现哪里的结果有分歧。

实例:以下校验和开始出现分歧,因此永远不会收敛。如果所有输入都是完全相同的,那这很可能就是一个可重复性问题。

检查点与内存中的运行

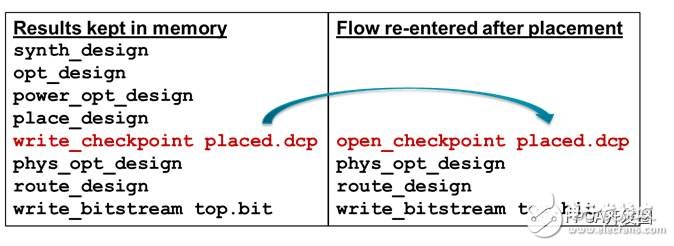

与同等意义的内存内设计流程相比,检查点应生成可重复性的结果。请考虑以下命令顺序,一个运行内存中的整个设计流程,另一个则使用放置的检查点通过 phys_opt_design 命令再次从内存中的流程进入该流程。

这两个运行应该给出相同的结果。尽管在执行 open_checkpoint 命令后,校验和可能因为网表的排序差异而不同,但在第一次执行 phys_opt_design 命令后,校验和应该可以收敛:

在运行之前,每一个执行命令都会自动排序,以确保网表的一致性,这样结果就不会因网表差异而出现分歧。

最大限度提高可重复性

如果可重复性对于您的设计环境至关重要,下面的操作可帮助您最大限度地提高可重复性:

在单线程模式下运行。

在不同运行之间使用不同数量的 CPU 时,同步线程可能会按照不同的顺序执行运算并造成有分歧的结果,即便运行使用相同的机器或系统也是如此。

要在单线程模式下运行,请使用:

set_param general.maxThreads 1

这不仅可禁用多线程,而且还可消除相关可重复性问题。

在相同机器上运行或者在使用相同操作系统的机器上运行。

这不仅可降低遇到内核运行方式所带来的不可重复性的概率,而且还可从一个系统到另一个系统实现系统调用,特别是在使用 Windows 和 Linux 操作系统的情况下。

以下操作可进一步降低这一概率

1) 微调环境,消除下列情况:

-

同一操作系统的不同版本

-

不同的服务包级别 (Windows)

-

不同分销或不同补丁级别 (Linux)

2) 消除计算硬件差异:

-

使用相同的通用物理及虚拟存储器容量。

-

使用相同的处理器架构和相同数量的内核。

-

如果使用的是虚拟机,则要保证配置完全相同。

报告不可重复性问题

如果您遇到了输入完全相同的不可重复性问题(如解决方案说明中所述),请打开服务请求并提供一个可演示该问题的测试案例。

没有测试案例,可能很难确定并修复任务问题,但它可帮助提供尽可能多的信息。

Linux 和 Windows 之间偶尔会出现不可重复性问题,我们建议限制 Vivado 只在 Linux 上运行或只在 Windows 上运行。

-

Linux

+关注

关注

87文章

11312浏览量

209701 -

WINDOWS

+关注

关注

4文章

3551浏览量

88801 -

Vivado

+关注

关注

19文章

812浏览量

66611

原文标题:【专家坐堂Q&A】Vivado 结果是否可重复用于相同的工具输入?

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vivado 2017.4和2018.2不同的Linux和Windows之间的实现结果

我应该使用什么操作系统?

(良哥独创)linux操作系统装回windows操作系统

Windows XP操作系统 ppt课件

Linux是什么?这种操作系统为何如此流行?

Linux和Windows操作系统你更希望用哪个?

Windows 10操作系统会有专门的Linux子系统

怎样实现在linux系统中对windows系统的远程操作?

Linux操作系统与Windows操作系统的五大区别

Windows和Linux操作系统的流式处理API

Linux与Windows服务器操作系统有什么区别?

每次Vivado编译的结果都一样吗

Linux 和 Windows 操作系统中 Vivado 结果是否可重复?

Linux 和 Windows 操作系统中 Vivado 结果是否可重复?

评论