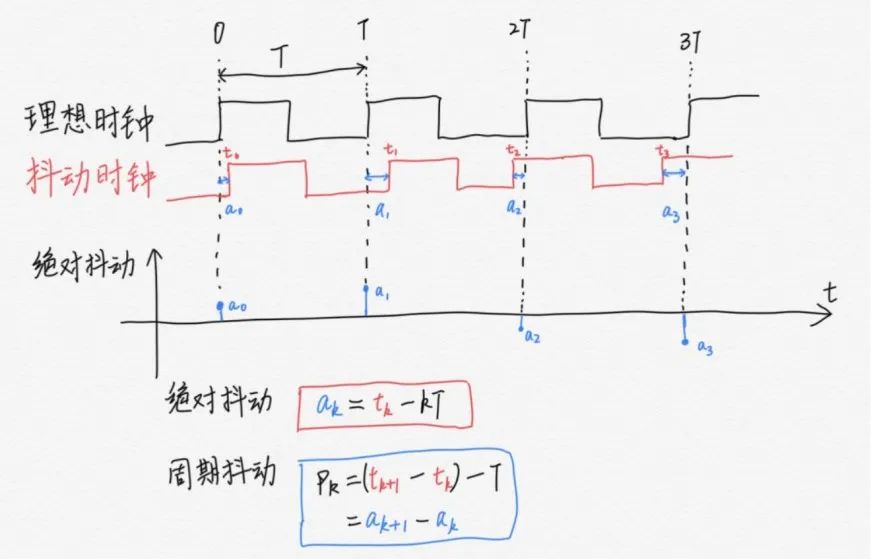

在高速串行通信系统中,CDR(时钟数据恢复)技术是实现数据传输的关键技术之一。然而,CDR电路的设计面临着一个重要的挑战——抖动。抖动现象指的是数据信号在实际传输过程中的位置相对于理想位置的偏离。这种偏离可能导致数据传输错误,因此,理解和控制抖动对于保证通信系统的可靠性至关重要。

抖动通常分为两种类型:确定性抖动和随机抖动。确定性抖动是由多个因素引起的,包括码间干扰、串扰、占空失真以及周期性抖动等。这些抖动的来源通常是可以预测的,比如开关电源引起的干扰。与之相对的是随机抖动,它通常是由半导体器件的热噪声引起的,并且难以预测。

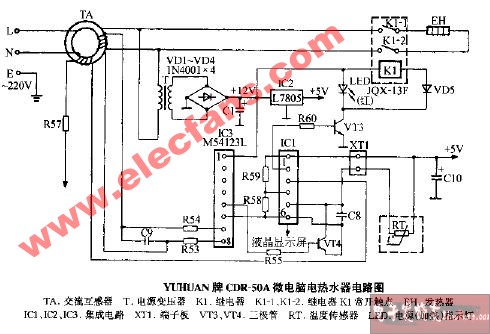

在CDR电路中,传送参考时钟、传送PLL(相位锁定环)、串化器以及高速输出缓冲器等部件都可能对传送抖动产生影响。传送抖动的大小通常用单位间隔的百分比或UI来表示。例如,0.2 UI的传送抖动意味着抖动占据了比特周期的20%。在设计中,我们希望这个数值尽可能低,因为更低的UI数值代表更少的抖动,从而意味着更优的信号质量。

同样地,CDR接收器也会有一个规格,指明在给定的比特率下它能容忍的最大抖动量。一般来说,比特误码率的标准设定为1e-12。接收器的抖动容限也用UI来表示,一个较大的UI值表明接收器能够容忍更多的抖动。例如,0.8 UI的接收抖动容限意味着即使80%的比特周期被噪声占据,接收器仍然能够可靠地接收数据。

抖动的量化通常借助于统计上的钟形分布来进行,该分布的中心点代表了理想的信号边沿位置。通过这种方式,设计人员可以直观地看到抖动对信号质量的影响,并据此进行优化设计。

在面对抖动问题时,设计人员需要采取一系列措施来确保信号的稳定传输。首先,选择合适的电路板材料和布线策略可以减小串扰和码间干扰。其次,使用高质量的电源和电源滤波器可以减少周期性抖动。此外,优化PLL的参数和串化器的设计也是降低确定性抖动的有效方法。对于随机抖动,虽然难以彻底消除,但可以通过改进半导体制程和散热设计来尽量降低其影响。

总之,抖动是CDR电路设计中的一个核心挑战,它直接关系到高速串行通信系统的性能和可靠性。通过深入理解抖动的来源和特性,以及采取合理的设计措施,可以有效地管理和减轻抖动的影响。随着通信技术的不断进步,对抖动的控制和管理将变得更加重要,这要求设计人员不断创新和优化,以实现更高效、更可靠的数据传输解决方案。

-

接收器

+关注

关注

14文章

2486浏览量

72487 -

电路设计

+关注

关注

6679文章

2474浏览量

206205 -

cdr

+关注

关注

1文章

51浏览量

18193

发布评论请先 登录

相关推荐

SERDES接口电路设计

请问如何在具有抖动的Artix-7 GTP数据流的情况下提高CDR性能?

采用bang-bang PD的CDR电路设计常见问题解答

去抖动延时可调键盘电路的设计

CDR电路设计与抖动管理

CDR电路设计与抖动管理

评论