本次技术分享介绍VeriStand的执行机制以及该机制下信号传输的延迟,当仿真测试对信号延迟有一定要求时,考虑VeriStand执行机制的影响是必要的,现在请跟随小编的步伐一起学习吧!

本文教程:

VeriStand执行机制

一、硬件单点采样

VeriStand添加通道时默认使用的是硬件单点采样模式,该模式下采集数据不会在缓存中停留等待,这是由于硬件单点采样模式不带缓冲机制,无需等待采集到特定个点数后再读取。

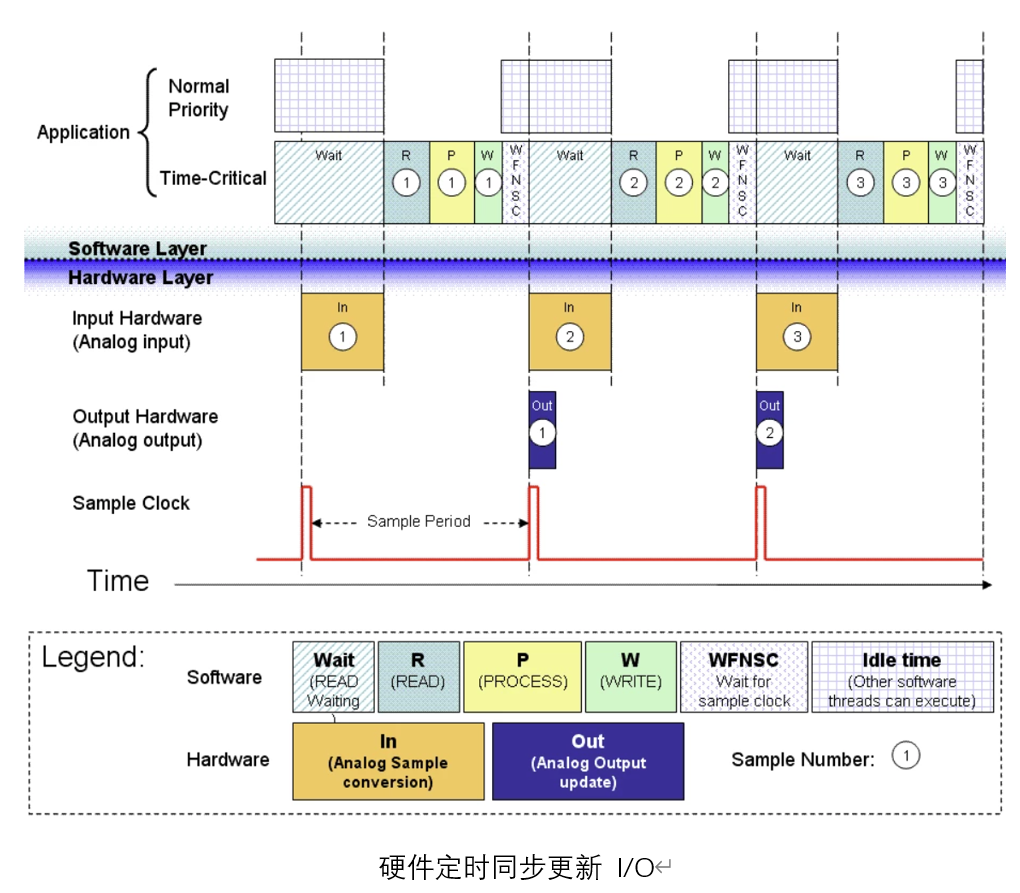

在VeriStand中设置硬件单点定时采集时,将使用机箱背板提供的时钟来同步AI和AO 。如下图,硬件定时同步更新 I/O模式下AI采集的值经过了R、P、W步骤后,需要等待下一次时钟的上升沿才能由AO输出,即AI、AO操作需要与时钟信号对齐。

二、VeriStand的工作机制和延迟

1、并行执行模式

在并行执行模式下,使用硬件定时同步更新 I/O,AI和AO需要与时钟对齐,AO输出的是上一次PCL主循环(Primary Control Loop)中AI读取并经模型处理的值,所以存在一个PCL执行时间的延迟,对于10k模拟频率的情况,延迟为100μs。

具体原理如上图,模型的执行结果直接传输到下一PCL主循环,AI、AO都对齐来自机箱背板的时钟信号实现同时执行,但AO输出的是上一个PCL的执行结果,过程中有一个PCL执行周期的延迟。

2、低延迟执行模式

低延迟执行模式下,AI采集到值并经过模型运算后立刻传到AO输出,无需等待到下一次PCL再进行AO输出;AI在采样时钟的上升沿进行采集,AO等待接受到模型执行结果后输出,AI到AO的延迟约等于模型执行时间(数据的硬件传输时间不超过1us)。

此时AI仍然严格对齐时钟,但是AO的更新时间由得到模型处理结果后对AO赋值的时间节点决定,因为模型的执行速度不是精确恒定,AO的输出节拍会有抖动,是否产生不良影响由具体情况而定。

当需要执行多个模型且模型之间有数据传递,模型的执行顺序设置会对延迟产生较大影响。

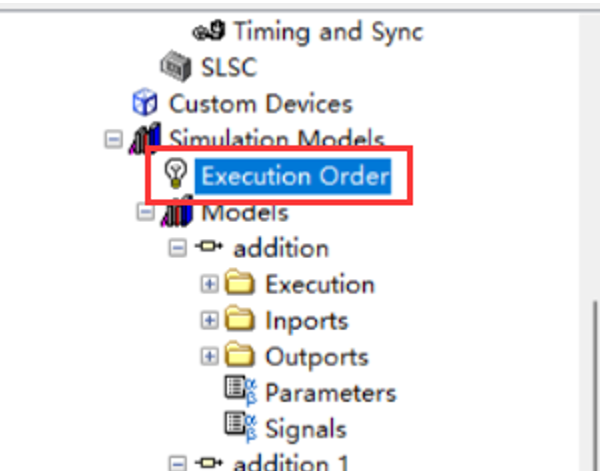

还记得之前教程出现过的Execution Order吗,在这里可以设置模型的执行顺序,执行前后顺序按Group分组,默认会把所有模型放到同一分组并行执行。下面通过示意图展示模型执行的机制,结论基于验证实验推导而来。

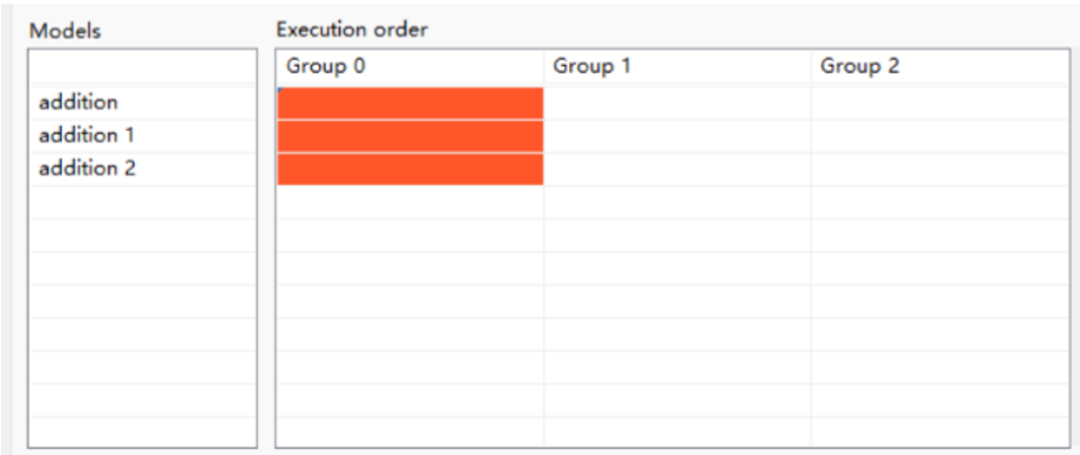

3.1 模型的并行执行

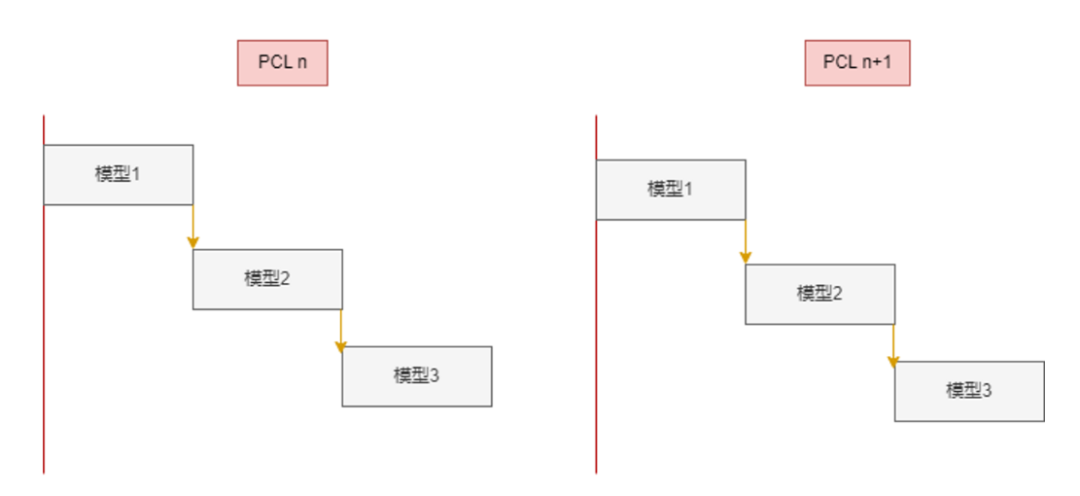

首先看默认的模型并行执行的情况,假设三个模型从上到下依次传递数据。

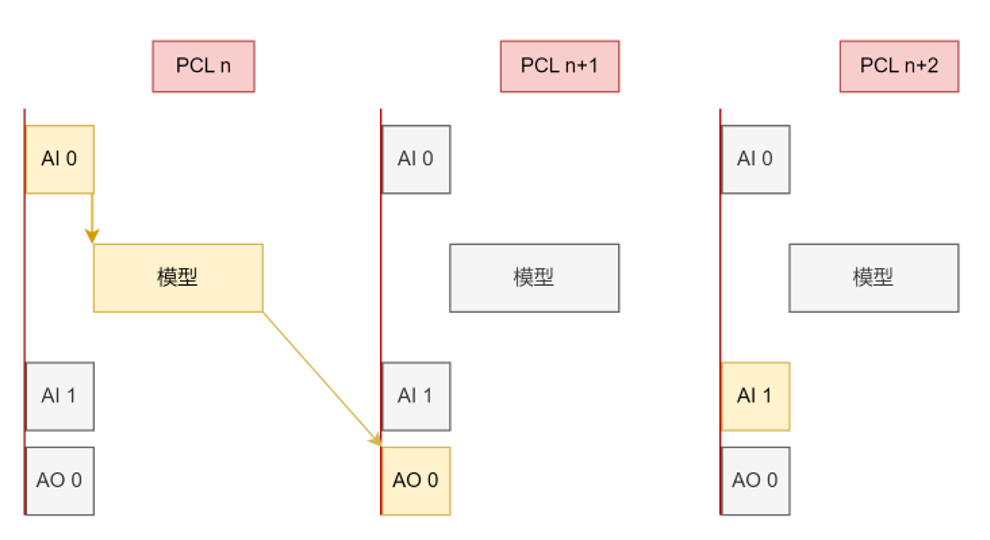

三个模型同组的执行机制如上图所示,类似于前文描述的 输入、模型、输出 并行执行模式,只不过这里变成了模型1、模型2、模型3并行执行,即三个模型依旧是同时执行,但每次传递数据到下一个模型都必须等待下一次PCL主循环。

所以,若VeriStand设置为并行执行,三个模型均在同一Group,则上图中PCL n进行了AI采集并立刻传输给模型1运算,经过传递,最终在PCL n+2中由模型3输出最终计算结构,并在下一次的PCL n+3中由AO输出,AI到AO有三个PCL周期的延迟。

同理,如果VeriStand设置为低延迟模式,三个模型依然是在同一Group,那么AI到AO的延迟=两个PCL执行周期+模型3的执行耗时。

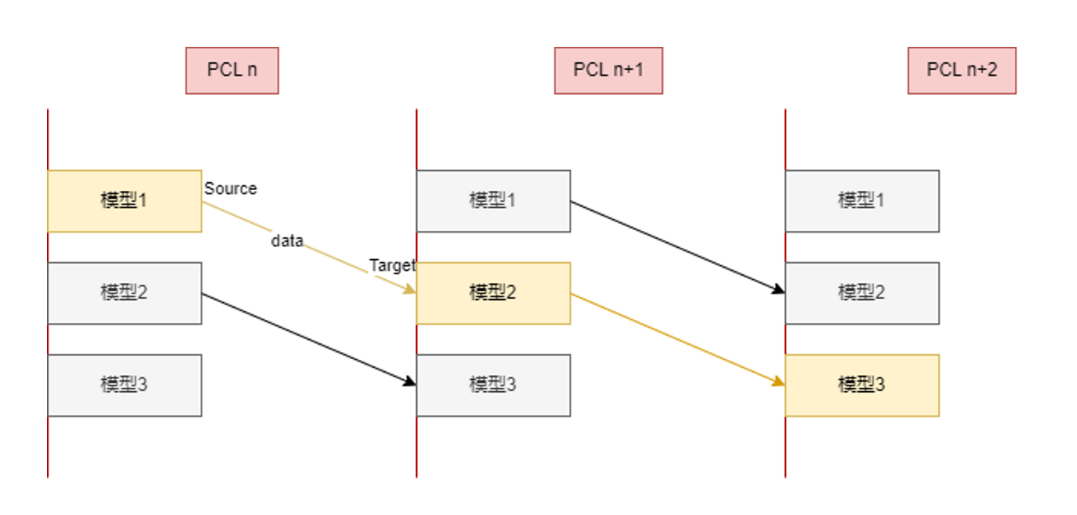

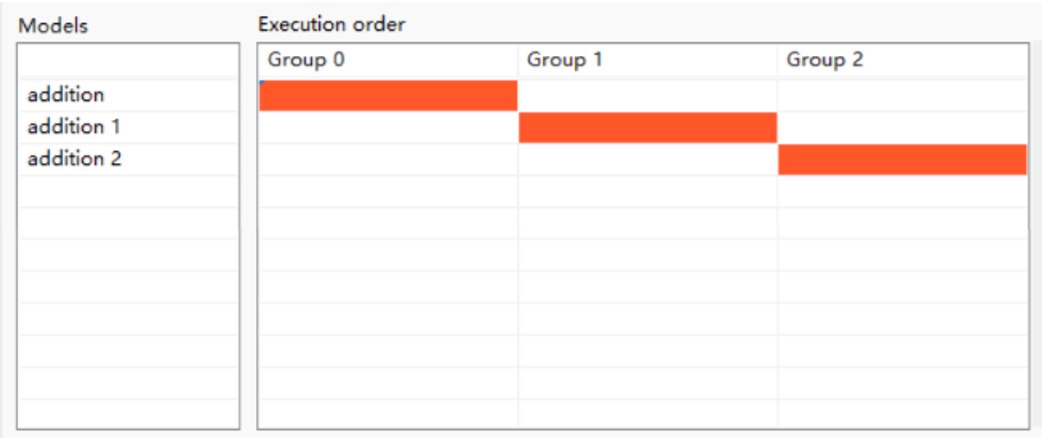

3.2 模型的分步执行

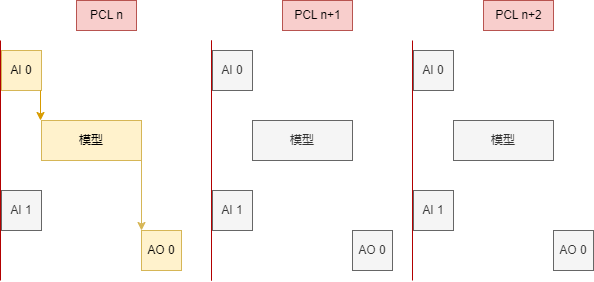

当模型被安排到前后按顺序执行的一个个Group时,模型的执行机制就类似于上文中描述的VeriStand低延迟执行模式。

如上图所示,三个模型不是并行执行,其按照设置的Group顺序前后进行。

若VeriStand设置为并行执行,模型执行顺序按照分组前后执行:AI在PCL n开始时采集,经过三个模型计算,运算结果在PCL n+1开始时由AO输出,AI到AO的延迟为一个PCL周期。

若VeriStand设置为低延迟模式,模型执行顺序按照分组前后执行:AI在PCL n开始时采集,经过三个模型计算,运算结果在第三个模型执行结束后立刻由AO输出,无需等待到下一次PCL主循环,AI到AO的延迟约等于三个模型的计算耗时。

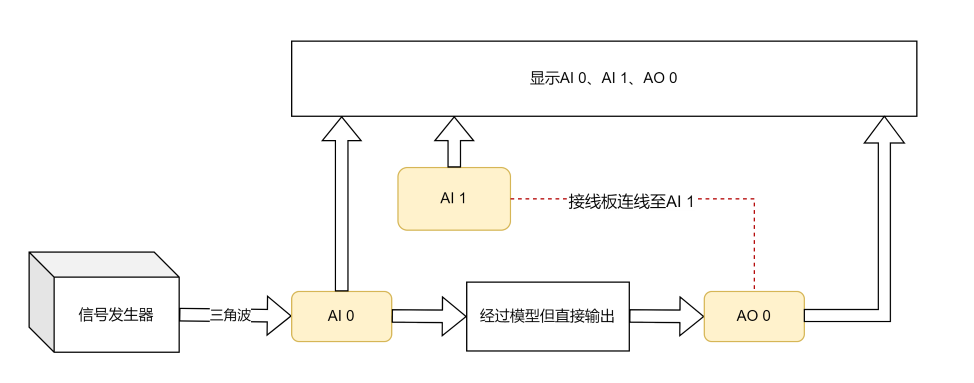

4、实验验证

感兴趣的小伙伴可以参考上图的原理设计一个实验来验证本文所提到的两种执行模式的原理和延迟。其中,信号发生器产生三角波输入到AI 0,VeriStand采集到AI 0的数据后映射到模型,模型不改变值并直接输出到AO 0,AO 0输出电压到AI 1,将AI 0、 AI 1、AO 0显示在波形显示面板。

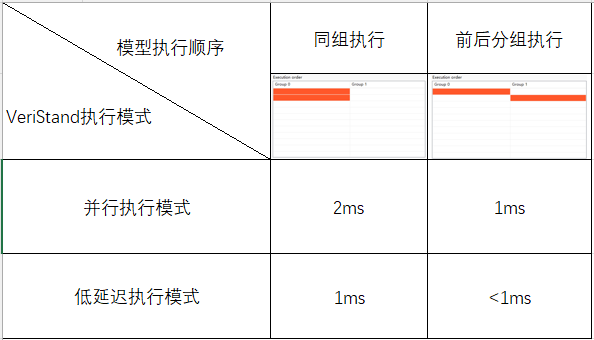

上图统计了各设置下执行时AI 0到AO 0的实验真实延迟,本次实验的VeriStand目标频率是1k,1ms等价于1个PCL周期,大家可以自己推导一下理论延迟做对比;两设置排列组合下所有情况的延迟都符合理论预设的预期。

以上就是本次分享的所有内容啦,欢迎大家留言讨论,交流分享!

-

硬件

+关注

关注

11文章

3413浏览量

66583 -

仿真测试

+关注

关注

0文章

91浏览量

11373 -

VeriStand

+关注

关注

7文章

13浏览量

22571

原文标题:VeriStand 执行机制

文章出处:【微信号:华穗科技,微信公众号:华穗科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

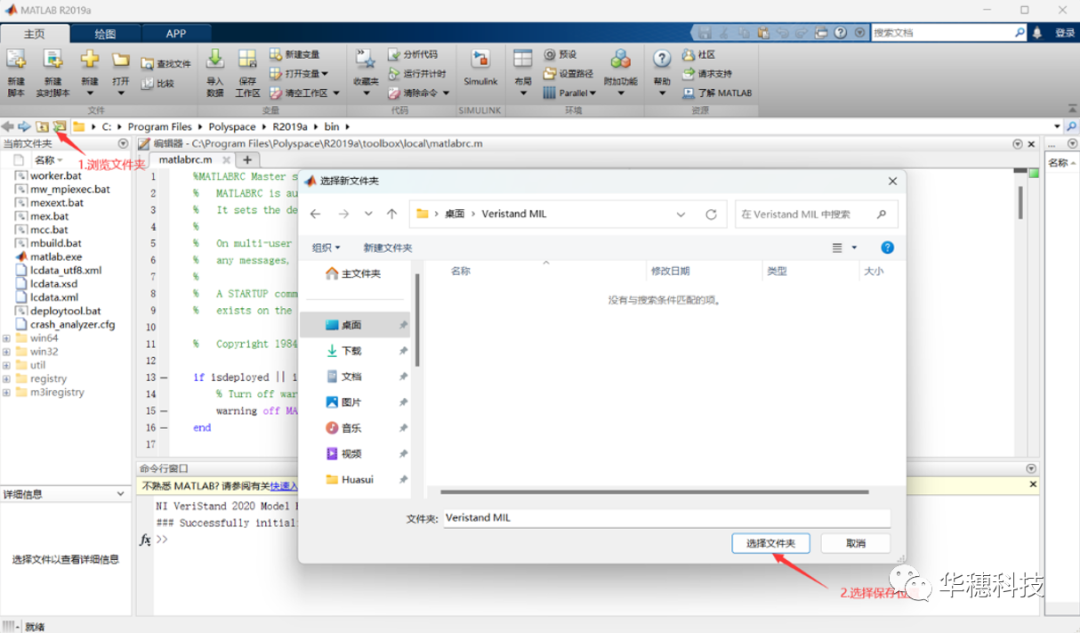

使用VeriStand搭建MIL测试环境

Simulink中的NI VeriStand Blocks在安装完VeriStand后没有自动出现,该怎么找到?

VeriStand 2014中Stimulus Profiles Editor的用法

NI VeriStand 2016 与matlab 2016 搭配的问题

matlab 2016a 与 NI VeriStand 2016 代码生成问题

labview建立veristand模型

Veristand,创建导入labview模型

veristand访问C模块

利用NI VeriStand 2010特性创建分布式系统

labview与veristand无法建立连接

veristand入XML文件

最新NI VeriStand 2010适用于从高性能多机箱系

在NI VeriStand环境中进行FPGA相关配置

如何使用VeriStand的User Channels、Alarms、Procedures功能?

VeriStand的执行机制

VeriStand的执行机制

评论