新思科技近日宣布了一项重大技术突破,正式推出全球领先的40G UCIe(Universal Chiplet Interconnect Express)IP全面解决方案。这一创新成果以每引脚高达40 Gbps的惊人速度,重新定义了行业标准,为追求极致计算性能的人工智能数据中心市场带来了前所未有的动力。

UCIe互连作为裸片到裸片连接的行业标杆,对于实现多裸片封装架构中的高带宽、低延迟连接具有不可估量的价值。新思科技的40G UCIe IP解决方案正是基于这一关键需求而精心打造,它能够有效促进异构及同构裸片或芯片组之间的数据流动,确保在复杂的人工智能数据中心系统中,海量数据能够高效、快速地传输,从而大幅提升整体计算效率与性能。

此次发布不仅展示了新思科技在半导体IP领域的深厚积累与创新能力,更为全球多芯片系统设计领域树立了新的标杆,预示着未来数据中心及人工智能应用的性能将迎来质的飞跃。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

458文章

51419浏览量

428716 -

数据中心

+关注

关注

16文章

4906浏览量

72514 -

新思科技

+关注

关注

5文章

818浏览量

50474

发布评论请先 登录

相关推荐

新思科技全新40G UCIe IP解决方案助力Multi-Die设计

随着物理极限开始制约摩尔定律的发展,加之人工智能不断突破技术边界,计算需求和处理能力要求呈现爆发式增长。为了赋能生成式人工智能应用,现代数据中心不得不采用Multi-Die设计,而这又带来了许多技术要求,包括高带宽和低功耗Die-to-Die连接。

利用Multi-Die设计的AI数据中心芯片对40G UCIe IP的需求

。为了快速可靠地处理AI工作负载,Multi-Die设计中的Die-to-Die接口必须兼具稳健、低延迟和高带宽特性,最后一点尤为关键。本文概述了利用Multi-Die设计的AI数据中心芯片对40G UCIe

Alpahwave Semi推出全球首个64Gbps UCIe D2D互联IP子系统

半导体连接IP领域的领先企业Alpahwave Semi近日宣布了一项重大突破,成功推出了全球首个64Gbps高速UCIe D2D(裸片对裸片)互联IP子系统。这一创新成果标志着Alp

40G光模块介绍及常见问题探讨

光模块厂家提供40G光模块,应用于数据中心,云计算,高性能计算场景,广泛兼容华为,华三,思科,锐捷等光纤模块品牌,助您实现高速数据传输。本文介绍40G光模块接口,光模块厂家,40G光模

UCIe规范引领Chiplet技术革新,新思科技发布40G UCIe IP解决方案

随着大型SoC(系统级芯片)的设计复杂度和制造难度不断攀升,芯片行业正面临前所未有的挑战。英伟达公司的Blackwell芯片B200,作为业界的一个典型代表,其晶体管数量相比上一代H1

新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速

IP,可实现异构和同构芯片之间的快速连接。 新思科技40G UCIe PHY IP 能够在同样

发表于 09-10 13:45

•469次阅读

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

提供了一个统一的协同设计与分析解决方案,通过新思科技3DIC Compiler加速从芯片到系统的各个阶段的多裸晶

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

3DIC Compiler协同设计与分析解决方案结合新思科技IP,加速英特尔代工EMIB技术的异构集成 摘要: 新思科技人工智能(AI)驱动型多

发表于 07-09 13:42

•847次阅读

新思科技推出业界首款PCIe 7.0 IP解决方案

PCIe 7.0 IP解决方案,加速万亿参数领域的芯片设计 新思科技推出业界首款完整的PCIe 7.0 IP解决

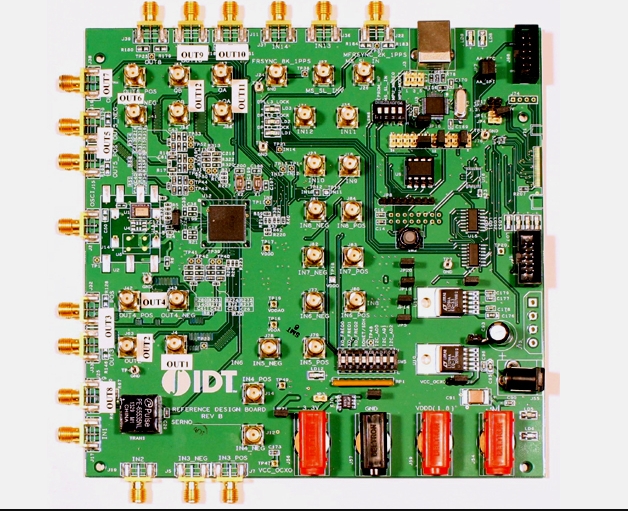

IEEE 1588和10G/40G同步以太网的82P33831同步管理单元评估板数据手册

电子发烧友网站提供《IEEE 1588和10G/40G同步以太网的82P33831同步管理单元评估板数据手册.rar》资料免费下载

发表于 05-10 15:52

•0次下载

新思科技与英特尔在UCIe互操作性测试进展

英特尔的测试芯片Pike Creek由基于Intel 3技术制造的英特尔UCIe IP小芯片组成。它与采用台积电公司N3工艺制造的新思科技

新思科技与英特尔深化合作加速先进芯片设计

近日,新思科技与英特尔宣布深化合作,共同加速先进芯片设计的步伐。据悉,新思科技的人工智能驱动的数字和模拟设计流程已经成功通过英特尔代工的Intel 18A工艺认证,这一突破性的进展标志

新思科技与英特尔深化合作,以新思科技IP和经Intel 18A工艺认证的EDA流程加速先进芯片设计

芯片制造商与EDA解决方案和广泛的IP组合紧密合作, 能够提升产品性能并加快上市时间 摘要: 新思科技数字和模拟EDA流程经过认证和优化,针对Intel 18A工艺实现功耗、性能和面积目标

发表于 03-05 10:16

•432次阅读

新思科技发布40G UCIe IP,加速多芯片系统设计

新思科技发布40G UCIe IP,加速多芯片系统设计

评论