在半导体制程技术的前沿,英特尔正稳步推进其“四年五个制程节点”计划,加速实现在2025年推出尖端的制程节点Intel 18A。

今天,我们将介绍英特尔的两项突破性技术:RibbonFET全环绕栅极晶体管和PowerVia背面供电技术。这两项技术首次成功集成于Intel 20A制程节点,也将用于Intel 18A。

RibbonFET:栅极“环抱”晶体管

通过RibbonFET晶体管,英特尔实现了全环绕栅极(GAA)架构。在晶体管中,栅极扮演着关键的开关角色,控制着电流的流动。RibbonFET使得栅极能够全面环绕带状的晶体管沟道,这一创新带来了三大优势:

•节约空间:晶体管沟道的垂直堆叠,相较于传统的水平堆叠,大幅减少了空间占用,有助于晶体管的进一步微缩;

•性能提升:栅极的全面环绕增强了对电流的控制,无论在何种电压下,都能提供更强的驱动电流,让晶体管开关的速度更快,从而提升晶体管性能;

•灵活设计:晶体管沟道可以根据不同的应用需求进行宽度调整,为芯片设计带来了更高的灵活性。

PowerVia:从“披萨”到“三明治”的转变

PowerVia背面供电技术改变了芯片布线的逻辑。

传统上,计算机芯片的制造过程类似于制作“披萨”,自下而上,先制造晶体管,再构建线路层,同时用于互连和供电。然而,随着晶体管尺寸的不断缩小,线路层变得越来越“拥挤”,复杂的布线成为了性能提升的瓶颈。

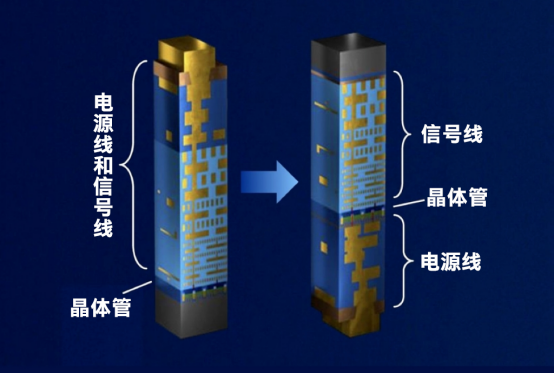

英特尔通过PowerVia实现了电源线与互连线的分离。首先制造晶体管,然后添加互连层,最后将晶圆翻转并打磨,以便在晶体管的底层接上电源线。形象地说,这一过程让芯片制造更像是制作“三明治”。

PowerVia革新了晶体管的布线方式

PowerVia革新了晶体管的布线方式

背面供电技术让晶体管的供电路径变得更加直接,有效改善了供电,减少了信号串扰,降低了功耗。测试显示,PowerVia能够将平台电压降低优化30%。

同时,这种新的供电方式还让芯片内部的空间得到了更高效的利用,使得芯片设计公司能够在不牺牲资源的前提下提高晶体管密度,显著提升性能。测试结果表明,采用PowerVia技术可以实现6%的频率增益和超过90%的标准单元利用率。

Intel 20A和Intel 18A的技术演进

半导体技术的创新是一个不断迭代的过程。在Intel 20A制程节点上,英特尔首次成功集成了RibbonFET和PowerVia这两项突破性技术。基于Intel 20A的技术实践,这两项技术将被应用于采用Intel 18A制程节点的首批产品:AI PC客户端处理器Panther Lake和服务器处理器Clearwater Forest。目前,新产品的样片已经出厂、上电并成功启动操作系统,预计将在2025年实现量产。

此外,这两项技术也将通过Intel 18A向英特尔代工(Intel Foundry)的客户提供。Intel 18A的缺陷密度已达到D0级别,小于0.40,显示出其在晶圆厂中的生产状况良好,良率表现优秀。今年7月,英特尔还发布了Intel 18A制程设计套件(PDK)的1.0版本,得到了生态系统的积极响应。

审核编辑 黄宇

-

英特尔

+关注

关注

60文章

9879浏览量

171434 -

晶体管

+关注

关注

77文章

9629浏览量

137826

发布评论请先 登录

相关推荐

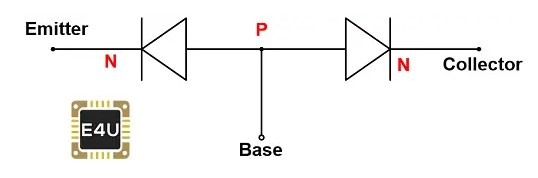

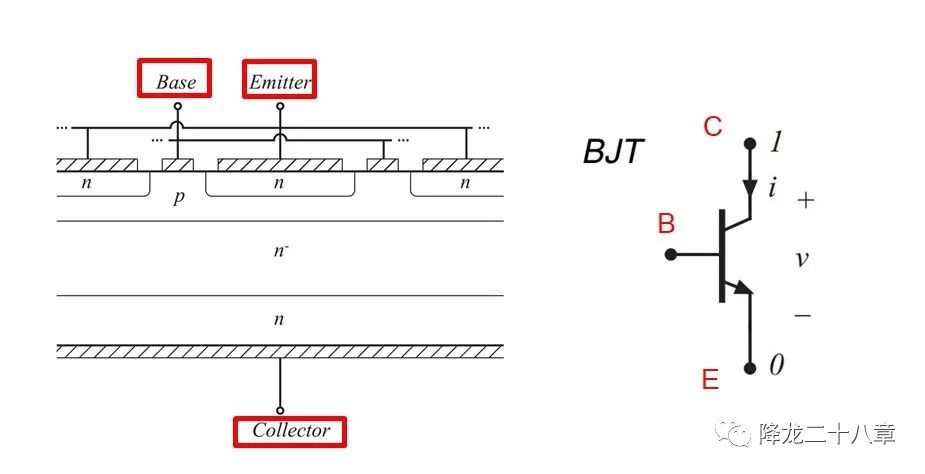

NMOS晶体管和PMOS晶体管的区别

晶体管处于放大状态的条件是什么

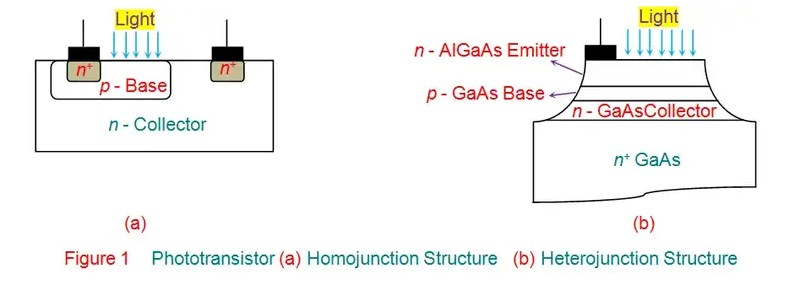

什么是光电晶体管?光电晶体管的工作原理和结构

晶体管的三种工作状态

什么是达林顿晶体管?达林顿晶体管的基本电路

晶体管的三个电极及工作区域

晶体管的三种工作状态及其特点

如何根据管脚电位判断晶体管

晶体管的三种工作状态介绍

晶体管的三个极的电压关系大小

晶体管三种接法的特点

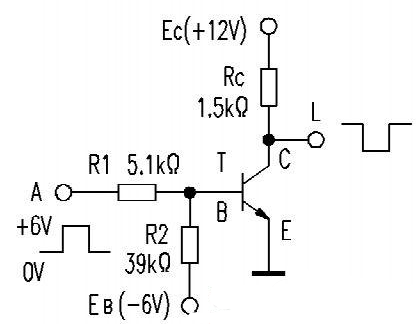

使用晶体管作为开关

技术前沿:“环抱”晶体管与“三明治”布线

技术前沿:“环抱”晶体管与“三明治”布线

评论